5.1实验目的

熟练掌握时序逻辑电路的设计。掌握计数器,数码管扫描显示电路以及秒表的原理。实现并仿真:

1)数码管扫描显示电路;

2)秒表电路。

5.2实验内容

(1)按照要求的解决方案,将四个输入在4个共阴极数码管上利用数码管扫描显示电路显示出来。

要求:

使用多个module实现;主模块中的代码最大化的进行精简,只用来实现各模块 间的信号传输,以及子模块的实例化;

计数器模块要使用不定位宽代码设计;

输入输出要考虑到小数点信号;

带复位信号,当复位信号为低电平时,四个数码管显示为0._0._0._0.;

仿真波形中输入用16进制显示,输出用2进制显示;

实例化代码全部使用.()来实现。

提示:先把设计图在草稿上画出来,可以大大简化代码设计(重要!)。

(2)设计秒表在4个共阴极数码管上利用上面的数码管扫描显示电路显示出来。要求显示从000.0-999.9循环计数。要求要有启动暂停信号go和复位信号rst。

提示:先把设计图在草稿上画出来,可以大大简化代码设计(重要!)。

解决方案不限,可以参考课堂上讲的思路或者书本上的思路。

(3)按照本模版撰写实验报告,版面排版要求及评分标准:

5.3数码管扫描显示电路

(1)设计代码

count.v

//计数器代码【时序电路】

`timescale 1ns / 1ps

module count #(parameter N=18)(input rst,clk,output [1:0] en);

reg [N-1:0] countnum;//计数器中的变量

always @(posedge clk)

if(!rst)

countnum<=0;

else

countnum<=countnum+1;

assign en=countnum[N-1:N-2];

endmodule

mux.v

//多路选择器 【组合电路】

`timescale 1ns / 1ps

module mux(in0,in1,in2,in3,dp,rst,en,data_select,dp_select,an);

input [3:0] in0,in1,in2,in3,dp;

input rst;

input [1:0] en;

output reg[3:0] data_select,an;

output reg dp_select;

always @*

if(!rst)

begin

an<=4'b1111;

dp_select<=1;

data_select<=4'd0000;

end

else

case(en)

2'b00:

begin

dp_select=dp[3]; an=4'b1000; data_select=in3;

end

2'b01:

begin

dp_select=dp[2]; an=4'b0100; data_select=in2;

end

2'b10:

begin

dp_select=dp[1]; an=4'b0010; data_select=in1;

end

default:

begin

dp_select=dp[0]; an=4'b0001; data_select=in0;

end

endcase

endmodule

decode.v

`timescale 1ns / 1ps

module decode(input [3:0] data_in,input dp_in,output reg [7:0] sseg);//8根输出线

always@*

begin

sseg=0;

case(data_in)

4'd0: sseg[7:1]=7'b1111110;

4'd1: sseg[7:1]=7'b0110000;

4'd2: sseg[7:1]=7'b1101101;

4'd3: sseg[7:1]=7'b1111001;

4'd4: sseg[7:1]=7'b0110011;

4'd5: sseg[7:1]=7'b1011011;

4'd6: sseg[7:1]=7'b1011111;

4'd7: sseg[7:1]=7'b1110000;

4'd8: sseg[7:1]=7'b1111111;

4'd9: sseg[7:1]=7'b1111011;

4'd10: sseg[7:1]=7'b1110111;

4'd11: sseg[7:1]=7'b0011111;

4'd12: sseg[7:1]=7'b1001110;

4'd13: sseg[7:1]=7'b0111101;

4'd14: sseg[7:1]=7'b1001111;

4'd15: sseg[7:1]=7'b1000111;

endcase

sseg[0]=dp_in;//小数点

end

endmodule

scan_led_display.v

`timescale 1ns / 1ps

module scan_led_display #(parameter M=18)(clk,rst,in3,in2,in1,in0,dp,sseg,an);

input clk, rst;

input[3:0] in3,in2,in1,in0,dp;

output [7:0]sseg;

output [3:0] an;

wire [3:0] data_in; //中间变量

wire dp_in; //中间变量

wire [1:0] en; //中间变量

count #(.N(M)) unit1(.rst(rst),.clk(clk),.en(en));

mux unit2(.in0(in0),.in1(in1),.in2(in2),.in3(in3),.dp(dp),.rst(rst),.en(en),.data_select(data_in),.an(an),.dp_select(dp_in));

decode unit3(.data_in(data_in),.dp_in(dp_in),.sseg(sseg));

endmodule

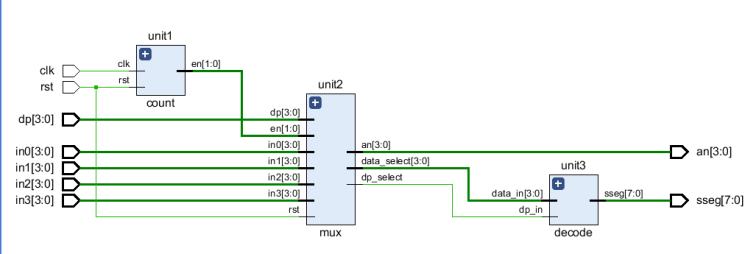

(2)RTL原理图(注意该把哪个文件设成top)

把scan_led_display.v设为top。

(3)testbench代码

testbench_scan_led_display.v

`timescale 1ns / 1ps

module testbench_scan_led_display

#(parameter N1=5);

reg clk,rst;

reg[3:0] in3,in2,in1,in0,dp;

wire [7:0] sseg;

wire [3:0] an;

scan_led_display #(.M(N1)) unit

(.clk(clk),.rst(rst),.in3(in3),.in2(in2),.in1(in1),.in0(in0),.sseg(sseg),.an(an),.dp(dp));

initial

begin

rst=1; clk=0; dp=4'b0000;

#15 rst=0;

#10 rst=1;

#10 rst=0;

#10 rst=1;

end

initial

begin

in0=4'd9;

in1=4'd10;

in2=4'd11;

in3=4'd12;

end

always

#2 clk=~clk;

initial

#200 $finish;

endmodule

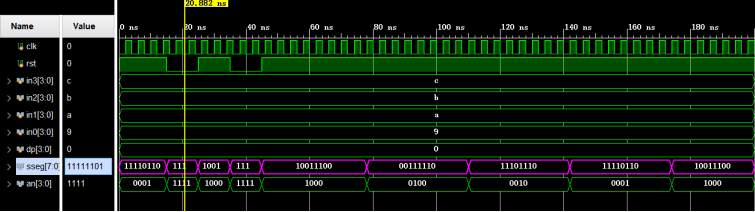

(4)仿真波形

5.4秒表电路

(1)设计代码

clk_FD.v

//计数器分频模块

`timescale 1ns / 1ps

module clk_FD #(parameter N=33,M=5*10**9)(clk,rst,clk_fd);

input clk,rst;

output reg clk_fd;

reg [N-1:0] regN;

always @(posedge clk)

if(!rst)

clk_fd<=0;

else if(regN<M-1)

regN<=regN+1;

else

begin

clk_fd<=~clk_fd;

regN<=0;

end

endmodule

watch.v

//计时模块

`timescale 1ns / 1ps

module watch(clk_fd,go,rst,d);

input clk_fd,go,rst;

output reg [3:0] d;

always @(posedge clk_fd)

if(!rst)

d<=4'd0;

else if(!go)

d<=d;

else if(d<4'd9)

d<=d+4'd1;

else

d<=4'd0;

endmodule

second_watch.v

//秒表计时模块

`timescale 1ns / 1ps

module second_watch #(parameter scan_time=18,N1=33,M1=5*10**9,N2=29,M2=5*10**8,N3=26,M3=5*10**7,N4=23,M4=5*10**6)

(clk,go,rst,sseg,an);

input clk,go,rst;

output [7:0] sseg;

output [3:0] an;

wire [3:0] in3,in2,in1,in0;

wire clk_001HZ,clk_01HZ,clk_1HZ,clk_10HZ;

//分频模块实例化4次

clk_FD #(.N(N1),.M(M1)) FD1(.clk(clk),.rst(rst),.clk_fd(clk_001HZ)); //100秒

clk_FD #(.N(N2),.M(M2)) FD2(.clk(clk),.rst(rst),.clk_fd(clk_01HZ)); //10秒

clk_FD #(.N(N3),.M(M3)) FD3(.clk(clk),.rst(rst),.clk_fd(clk_1HZ)); //1秒

clk_FD #(.N(N4),.M(M4)) FD4(.clk(clk),.rst(rst),.clk_fd(clk_10HZ)); //0.1秒

//计时模块实例化4次

watch w1(.clk_fd(clk_001HZ),.go(go),.rst(rst),.d(in3));

watch w2(.clk_fd(clk_01HZ),.go(go),.rst(rst),.d(in2));

watch w3(.clk_fd(clk_1HZ),.go(go),.rst(rst),.d(in1));

watch w4(.clk_fd(clk_10HZ),.go(go),.rst(rst),.d(in0));

//实例化数码管扫描模块

scan_led_display #(.M(scan_time)) scan(.clk(clk),.rst(rst),.in3(in3),.in2(in2),.in1(in1),.in0(in0),.dp(4'b0010),.sseg(sseg),.an(an));

endmodule

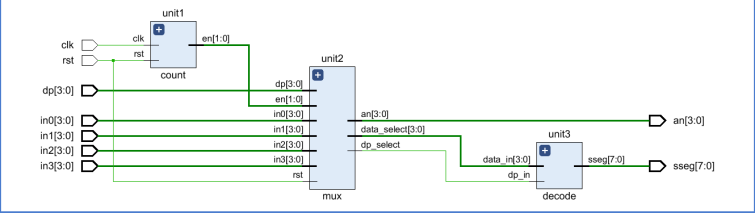

(2)RTL原理图(注意该把哪个文件设成top)

把second_watc.v和testbench_second_watch.v设为top。

(3)testbench代码

`timescale 1ns / 1ps

module testbench_second_watch;

reg clk,go,rst;

wire[7:0] sseg;

wire[3:0] an;

second_watch #(.scan_time(2),.N1(2),.M1(2),.N2(2),.M2(2),.N3(2),.M3(2),.N4(2),.M4(2))

sw(.clk(clk),.go(go),.rst(rst),.sseg(sseg),.an(an));

initial

begin

go=1; clk=0;

#20 go=0;

#5 go=1;

end

initial

begin

rst=1;

#5 rst=0;

#2 rst=1;

end

always #2 clk=~clk;

initial #100 $finish;

endmodule

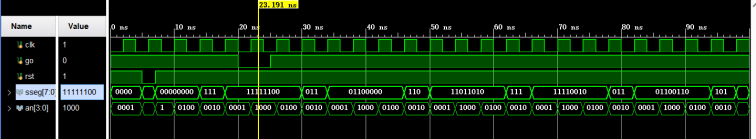

(4)仿真波形

最后

以上就是无限鱼最近收集整理的关于实验五 数码管扫描显示电路的全部内容,更多相关实验五内容请搜索靠谱客的其他文章。

发表评论 取消回复