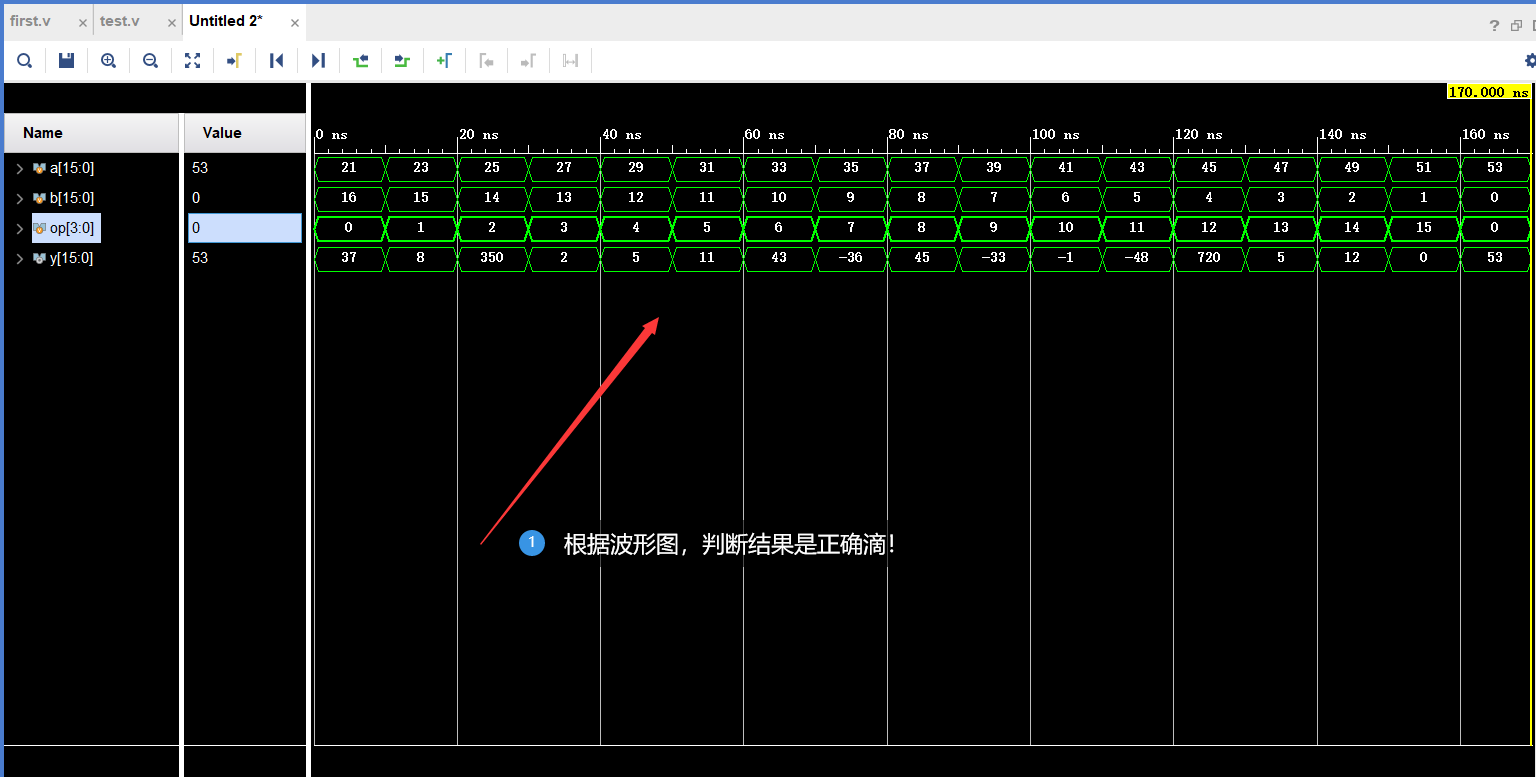

1. 使用 Verilog 完成 ALU 的设计,并编写测试仿真文件验证其正确性。要求: ALU 支持 16 位的加、减、与、或以及移位运算。

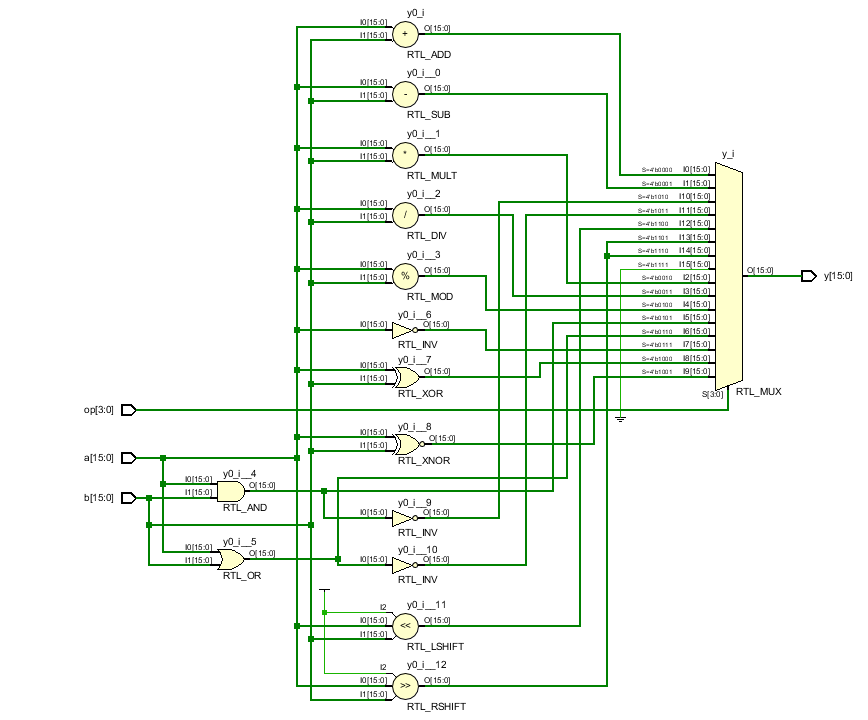

module ALU(a,b,op,y);

input[15:0]a,b;

input[3:0]op;

output y;

reg[15:0]y;

always@(*)begin

case(op)

//算术运算

4'd0: y = a + b;

4'd1: y = a - b;

4'd2: y = a * b;

4'd3: y = a / b;

4'd4: y = a % b; //求余

//位运算

4'd5: y = a & b; //与

4'd6: y = a | b; //或

4'd7: y = ~a; //非

4'd8: y = a ^ b; //异或

4'd9: y = a ~^ b; //同或

4'd10: y = ~(a & b);//与非

4'd11: y = ~(a | b);//或非

//移位运算

4'd12: y = a << b;//逻辑左移和算术左移结果相同

4'd13: y = a >> b;//逻辑右移

4'd14: y = a >>> b;//算术右移

4'd15: y = 0;

endcase

end

endmodule

module test(

);

reg[15:0] a,b;

reg[3:0] op;

wire[15:0] y;

ALU f(.a(a),.b(b),.op(op),.y(y));

initial begin

a = 21;b = 16;op = 0;

#170 $stop;

end

always begin

#10 a = a + 2;

b = b-1;

op = op+1;

end

endmodule

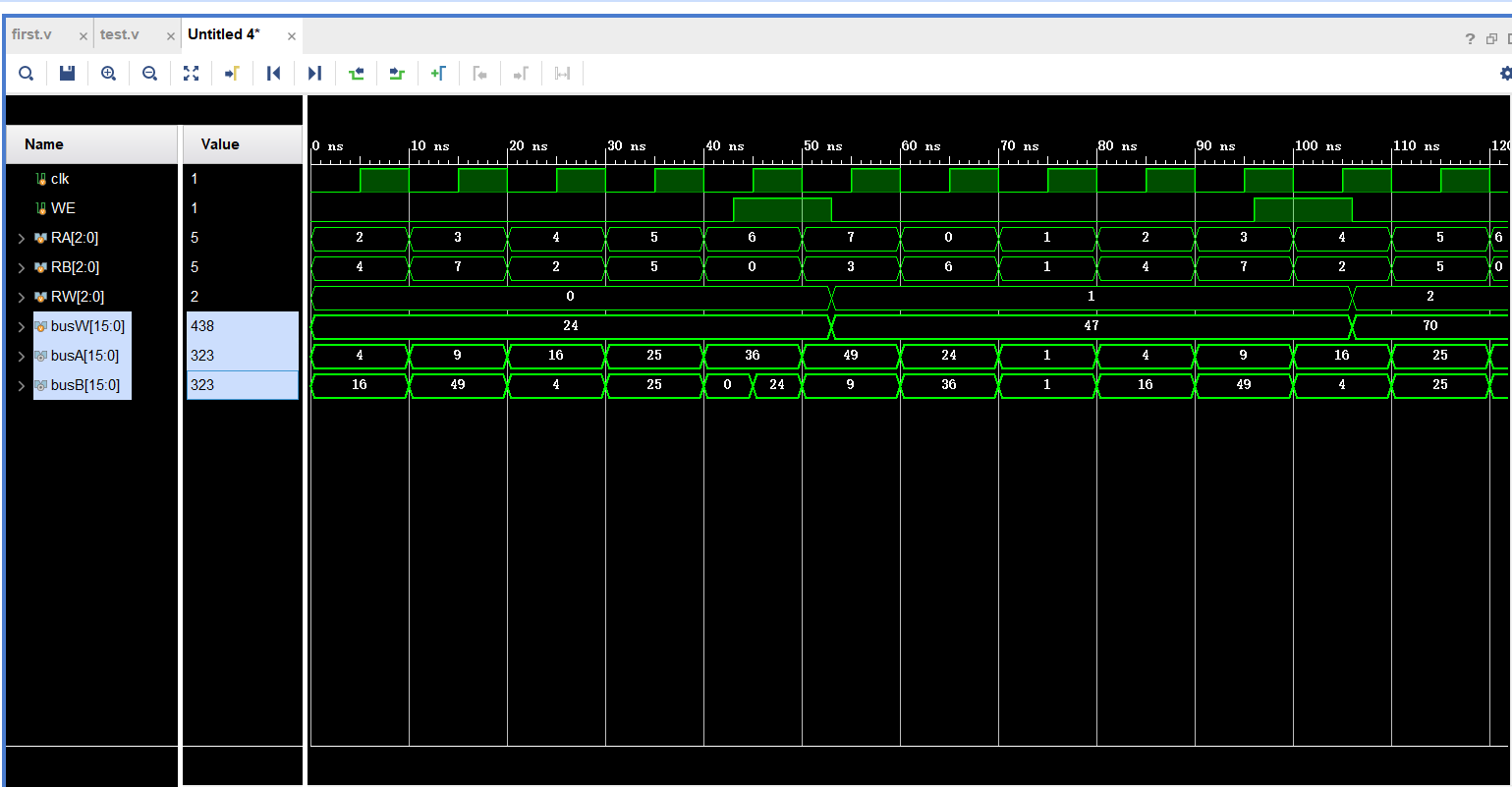

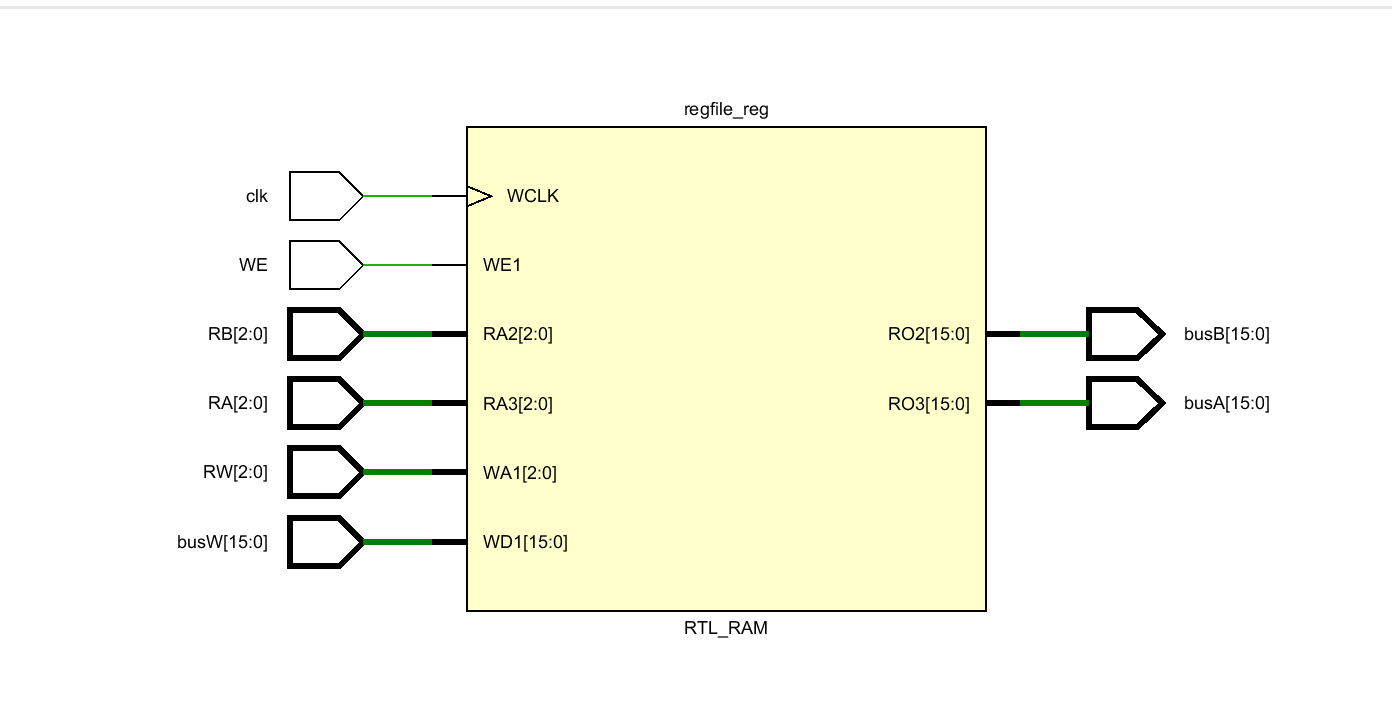

2. 使用 Verilog 完成通用寄存器堆的设计,并编写测试仿真文件验证其正确性。

要求 寄存器堆包含 8 个 16 位的寄存器; 寄存器堆有两个读端口和一个写端口。

设计一个8*16位的寄存器堆,即含有8个寄存器,每个寄存器16位。该寄存器堆有2个读端口、1个写端口,即能够同时读出2个寄存器的值,写入1个寄存器。读操作不需要时钟控制,写操作需要在上跳沿才能写入。

module RegFile(clk,WE,RA,RB,RW,busA,busB,busW);

input clk,WE;

//相当于地址,用来决定读或写的寄存器

input[2:0] RA,RB,RW;

input[15:0] busW;//要写入寄存器堆的内容

output[15:0] busA,busB;//从寄存器堆读出的内容

reg[15:0] regfile[7:0];//寄存器堆

integer i;

initial begin // 初始化寄存器堆

for(i=0;i<8;i=i+1) //总是习惯i++,老是报错

regfile[i] = i*i;

end

always@(posedge clk)

begin

if(WE == 1)

regfile[RW] = busW;

end

assign busA = regfile[RA];

assign busB = regfile[RB];

endmodule

module test(

);

reg clk,WE;

reg[2:0] RA,RB,RW;

reg[15:0] busW;

wire[15:0] busA,busB;

RegFile f(.clk(clk),.WE(WE),.RA(RA),.RB(RB),.RW(RW),

.busW(busW),.busA(busA),.busB(busB));

initial begin

clk=0;WE=0;

RA=3'd2;RB=3'd4;RW=3'd0;

busW = 16'd24;

#1000 $stop;

end

always #5 clk = ~clk;

always begin

#43 WE = 1;

#10 WE = 0;

RW = RW + 1;

busW = busW + 23;

end

always begin

#10 RA = RA + 1;

RB = RB + 3;

end

endmodule

最后

以上就是美好季节最近收集整理的关于【计算机组成原理】实验二、CPU 部件实现之 ALU 和寄存器堆的全部内容,更多相关【计算机组成原理】实验二、CPU内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复