使用Logisim设计和实现mips寄存器堆(即,regFile),具体要求如下:

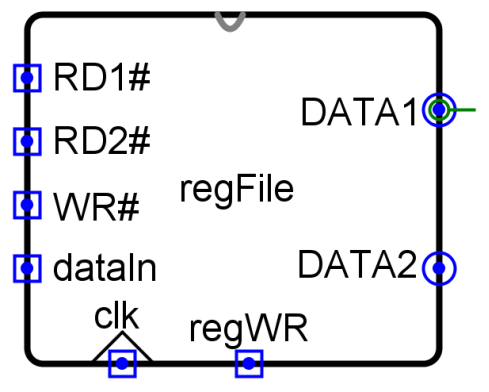

1,包含两个读寄存器号输入端口RD1和RD2,用来分别指定待读出数据的两个寄存器,这两个寄存器可能相同,也可能不同。读出的数据分别通过data1和data2两个输出端口获得;

2,包含一个写寄存器号输入端口WR,用来指定待写入数据的寄存器,数据通过dataIn端口送人寄存器;

3,数据写入时,需要写使能信号有效,即,regWrite=1,并在时钟clk上升沿到来时写入数据;

4,数据线位宽为32bit,端口号位宽5bit,时钟和写使能信号位宽1bit,实验时实现4~8个寄存器的读写控制即可。

mips寄存器堆的外形如下图所示。

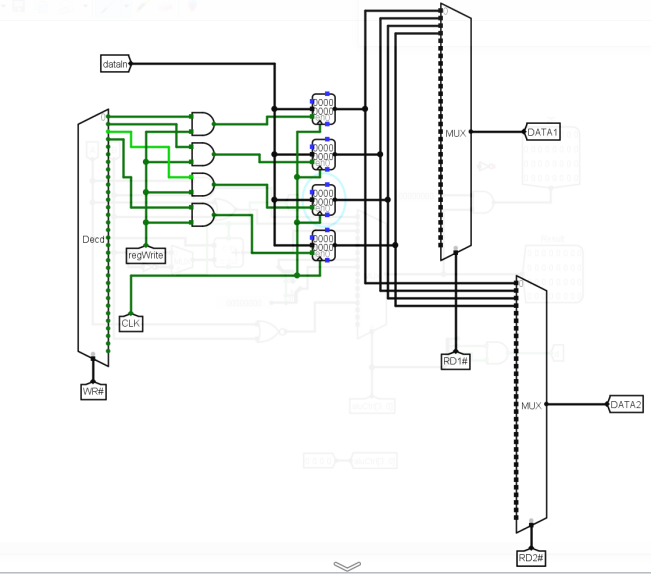

依题意、设计如下:

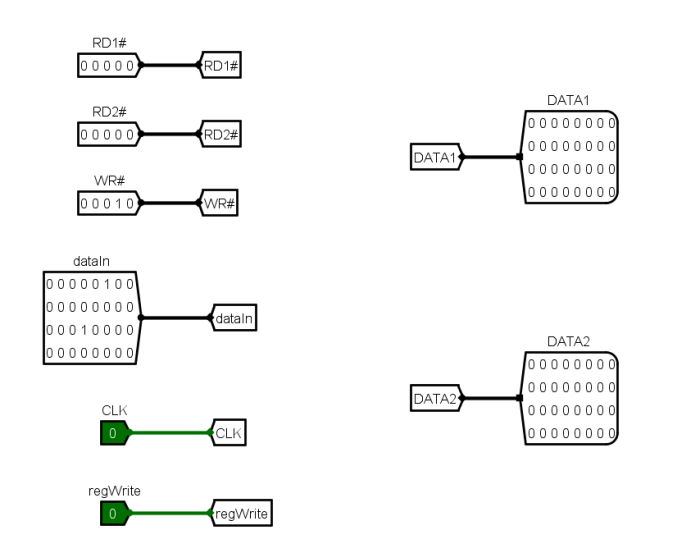

最后

以上就是慈祥大树最近收集整理的关于计算机组成原理 实验四 寄存器堆的设计与实现的全部内容,更多相关计算机组成原理内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复