代码段

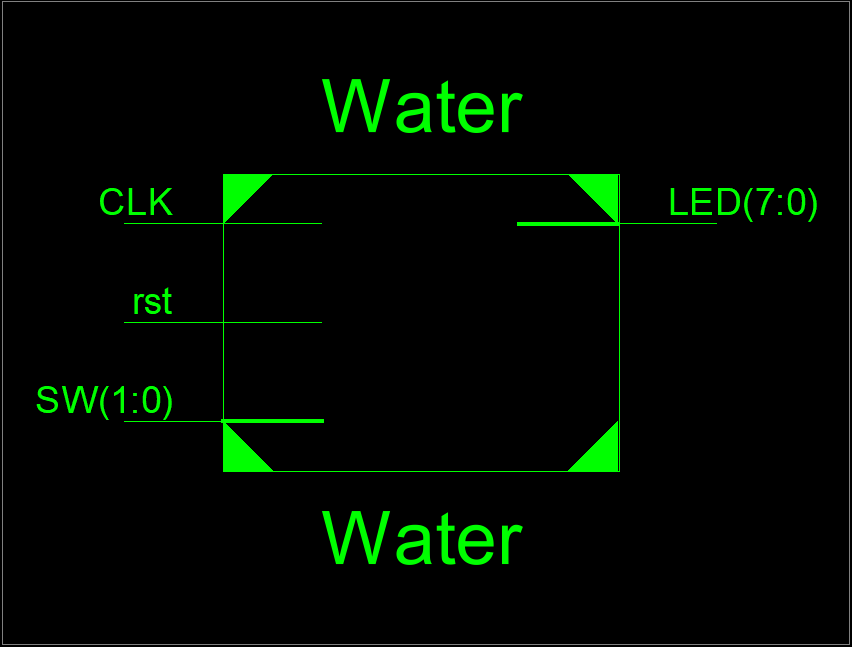

module Water(

input [1:0]SW,

input CLK,

input rst,

output reg [7:0] LED

);

wire CLK_1HZ;

reg [1:0] LS;

div uu1(CLK,rst,CLK_1HZ);

initial begin LED <= 8'b0; end

always @(posedge rst or posedge CLK_1HZ)

begin

if(rst) begin LED<=8'b00000000; end

else if( LED == 8'b0)

begin

case(SW)

2'b00:begin LED<=8'b10000000;LS<=SW; end

2'b01:begin LED<=8'b00000001;LS<=SW; end

2'b10:begin LED<=8'b00011000;LS<=SW; end

2'b11:begin LED<=8'b10000001;LS<=SW; end

endcase

end

else if( SW!=LS )

begin

case(SW)

2'b00:begin LED<=8'b10000000;LS<=SW; end

2'b01:begin LED<=8'b00000001;LS<=SW; end

2'b10:begin LED<=8'b00011000;LS<=SW; end

2'b11:begin LED<=8'b10000001;LS<=SW; end

endcase

end

else begin

case(SW)

2'b00: begin LED <= {LED[0],LED[7:1]};end

2'b01: begin LED <= {LED[6:0],LED[7]};end

2'b10: begin LED <= {LED[6:4],LED[7],LED[0],LED[3:1]};end

2'b11: begin LED <= {LED[4],LED[7:5],LED[2:0],LED[3]};end

endcase

end

end

endmodule

//分频器模块

module div(clk,rst,clk_div

);

input clk,rst;

output clk_div;

reg clk_div;

reg [23:0] counter;

initial begin counter = 24'd0; end

initial begin clk_div = 0; end

always @(posedge clk , posedge rst)

begin

if(rst)

begin

counter <= 24'b0;

clk_div <= 0;

end

else if(counter == 24'd12499999)

begin

clk_div <= ~clk_div;

counter <= 24'b0;

end

else

counter <= counter + 1'b1;

end

endmodule

测试文件

module test;

// Inputs

reg [1:0] SW;

reg CLK;

reg rst;

// Outputs

wire [7:0] LED;

// Instantiate the Unit Under Test (UUT)

Water uut (

.SW(SW),

.CLK(CLK),

.rst(rst),

.LED(LED)

);

always #1 CLK = ~CLK;

initial begin

SW = 2'b00;

CLK = 0;

rst = 0;

#100000000 SW = 2'b00; rst = 0;

#100000000 SW = 2'b01; rst = 0;

#100000000 SW = 2'b10; rst = 0;

#100000000 SW = 2'b11; rst = 0;

end

endmodule

仿真

管脚配置

# PlanAhead Generated IO constraints

NET "LED[7]" IOSTANDARD = LVCMOS18;

NET "LED[6]" IOSTANDARD = LVCMOS18;

NET "LED[5]" IOSTANDARD = LVCMOS18;

NET "LED[4]" IOSTANDARD = LVCMOS18;

NET "LED[3]" IOSTANDARD = LVCMOS18;

NET "LED[2]" IOSTANDARD = LVCMOS18;

NET "LED[1]" IOSTANDARD = LVCMOS18;

NET "LED[0]" IOSTANDARD = LVCMOS18;

NET "SW[1]" IOSTANDARD = LVCMOS18;

NET "SW[0]" IOSTANDARD = LVCMOS18;

NET "CLK" IOSTANDARD = LVCMOS18;

NET "rst" IOSTANDARD = LVCMOS18;

# PlanAhead Generated physical constraints

NET "LED[7]" LOC = R1;

NET "LED[6]" LOC = P2;

NET "LED[5]" LOC = P1;

NET "LED[4]" LOC = N2;

NET "LED[3]" LOC = M1;

NET "LED[2]" LOC = M2;

NET "LED[1]" LOC = L1;

NET "LED[0]" LOC = J2;

NET "CLK" LOC = H4;

# PlanAhead Generated IO constraints

NET "SW[1]" PULLDOWN;

NET "SW[0]" PULLDOWN;

NET "rst" PULLDOWN;

# PlanAhead Generated physical constraints

NET "rst" LOC = T3;

NET "SW[1]" LOC = U3;

NET "SW[0]" LOC = T4;

最后

以上就是活力萝莉最近收集整理的关于数电实验17:流水灯的全部内容,更多相关数电实验17内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复