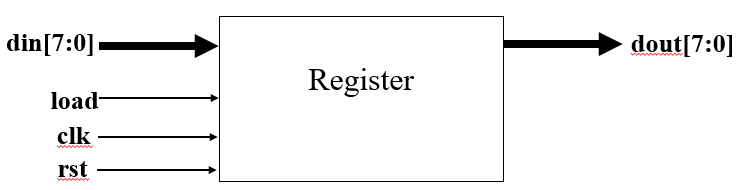

通用寄存器端口信号说明如下:

- dout:8位,输出,数据输出

- din:8位,输入,需要保存的数据

- load:1位,输入,load=1时该部件工作,load=0时该部件不工作

- clk:1位,输入,时钟信号,进行时序控制

- rst:1位,输入,复位信号,rst=0时,系统复位;rst=1时,系统正常工作

module register(clk,rst,load,din,dout);

input clk,rst,load;

input [7:0] din;

output reg[7:0] dout;

always@(posedge clk or negedge rst)

begin

if(rst==0)

dout <= 0;

else if(load)

dout <= din;

end

endmodule

将register.v设置为顶层模块

testbench文件

`timescale 10ns/1ns

module reg_tb();

reg clk;

reg [7:0] data_in;

reg rst;

reg load;

wire[7:0]data_out;

register mreg(.clk(clk),.rst(rst),.load(load),.din(data_in),.dout(data_out));

initial

begin

clk=0; rst=1; load=0; data_in=8'd23;

end

always #50 clk = ~clk;

initial

begin

#10 rst = 0;

#15 load = 1;

#10 rst = 1;

#20 load = 0;

#30 load = 1;

#15 data_in=8'd12;

#25 load = 0;

#25 rst = 0;data_in=8'd47;

#50 $finish;

end

endmodule

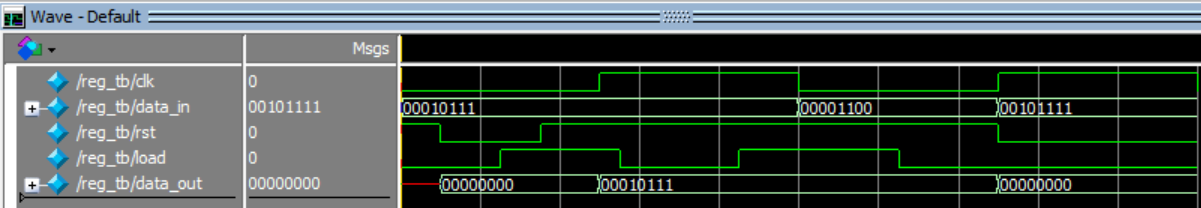

仿真波形图如下

最后

以上就是舒适小兔子最近收集整理的关于计算机组成原理 通用寄存器及其仿真的全部内容,更多相关计算机组成原理内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复