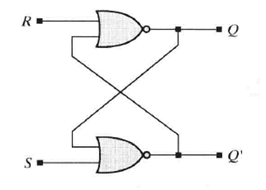

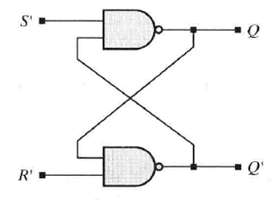

1:R-S锁存器

通过两个或非门(NOR)或者与非门(NAND)组成反馈电路组成。

R和S分别为置位端和复位端,使输出Q达到稳定的状态0或1

但NOR锁存器应避免11,NAND锁存器应避免00,在这两种状态下会导致下一个状态不确定的情况发生。

在任何时刻,输入的改变会立刻导致输出的改变,即电平敏感型锁存器。因此其抗燥性能较差。

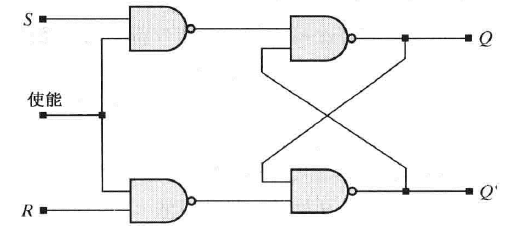

2:电平触发的锁存器

在基本的R-S锁存器的基础上添加输入控制门和CLK时钟输入信号。

2.1:待使能输入信号的S-R锁存器

通过时钟信号作为使能(门控),由使能信号决定S和R是否对电路产生影响。当锁存器处于使能状态时,透明锁存器的输出才会随数据输入变化而发生变化,若使能为0,s-r锁存器的输入一直保持。

在使能为1期间,Q可岁RS的变化进行多次翻转。

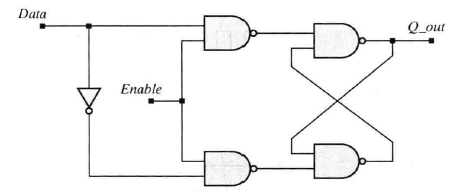

2.2:D锁存器

RS始终反向即可构成电平触发的D触发器

D锁存器可确保不会出现不稳定条件。

3:脉冲触发的触发器

触发器是边沿敏感的存储原件。数据存储的动作是由某一信号的上升沿或者下降沿进行同步的,该信号通常为时钟信号。

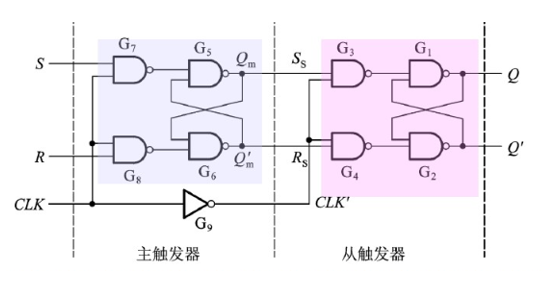

3.1主从RS触发器

当CLK为1时,主触发器按照RS的值进行翻转,从触发器保持状态

当CLK下降沿到达时,主触发器保持,从触发器根据主触发器的输出进行翻转。

因此在一个时钟周期内,输出状态只在下降沿到达时进行一次翻转。

注:仍需注意同时为1时的约束条件。

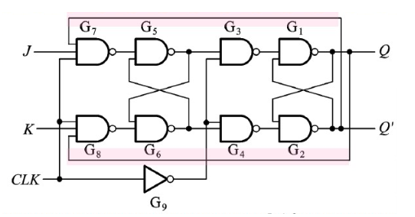

3.2 主次JK触发器

J为0、K为0,Q输出保持原状态;

J为1、K为0,Q输出为1;

J为0、K为1,Q输出为1;

J为1、K为1,Q输出发生偏转;

在一个时钟周期内,输出状态只在下降沿到达时进行一次翻转。

4:边沿触发的触发器

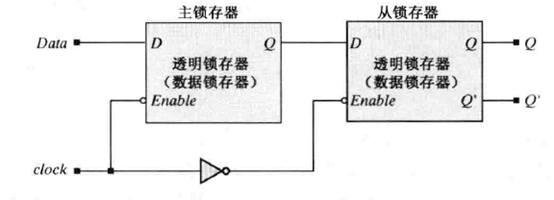

4.1:D触发器

利用下降沿出发点的D触发器,在CMOS工艺中,通常由传输门实现,其输入信号少,电路设计简便,因此被广泛应用。

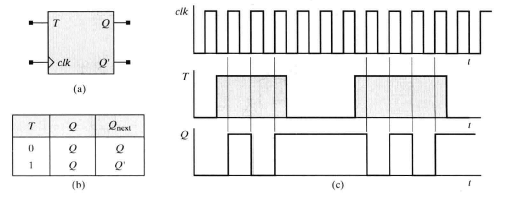

4.2:T触发器

T触发器在CLK上升沿判断输入信号T有效时,对输出自身进行翻转,否则输出保持。通常用于实现计数器。

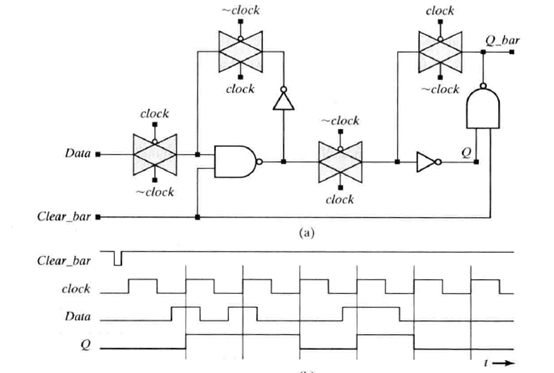

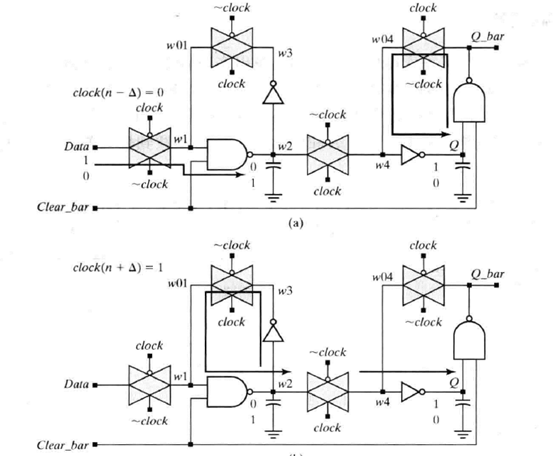

5:具有边沿触发功能的、带有附加清零信号Clear_bar的主从电路结构

清零信号Clear_bar为0时使得Q的输出无效,时钟为低电平是主传输门处于有效状态,时钟为高电平时从传输门处于有效状态。当时钟为低电平时,住传输门的输出有Data确定,当时钟为高时,主传输门的输出传递到从传输门。

总结:

- 锁存器的输出只与输入信号有关,没有时钟端;触发器受时钟控制,只有在时钟触发时才对采样进行采集,产生输出。

- 锁存器由电平控制,非同步控制;触发器则由时钟沿触发,为同步控制。

- 锁存器对时钟敏感,受布局布线影响较大,容易产生毛刺信号;触发器则受布局布线影响较小,不易产生毛刺信号。

- 锁存器所需门电路较触发器少,因此所需资源少。

注:在绝大多数的设计中应避免出现锁存器。

最后

以上就是热情抽屉最近收集整理的关于数字电路基础--IC设计之存储器件 (锁存器、触发器、寄存器)1:R-S锁存器2:电平触发的锁存器3:脉冲触发的触发器4:边沿触发的触发器5:具有边沿触发功能的、带有附加清零信号Clear_bar的主从电路结构 总结:的全部内容,更多相关数字电路基础--IC设计之存储器件内容请搜索靠谱客的其他文章。

发表评论 取消回复