目录

边沿检测

这是如何实现的呢?

下面给出Verilog HDL代码:

给出测试代码:

在Modelsim进行功能仿真:

ISE中进行综合得到RTL Schematic:

边沿检测

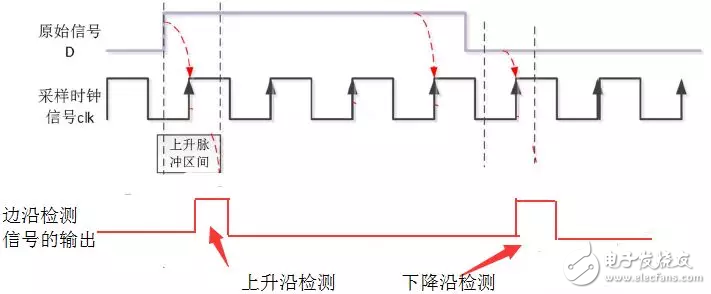

顾名思义,就是检测一个信号的边沿,当信号上升沿或下降沿到来时,获取一个脉冲信号。

时序图如下图:

这是如何实现的呢?

下面给出分析过程:

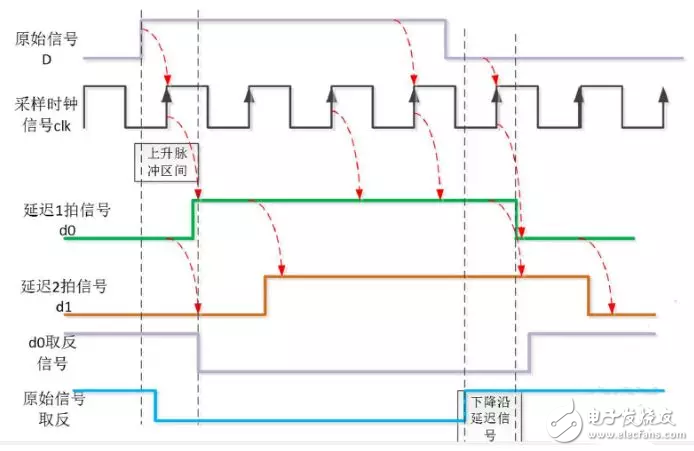

如下图:

d0为输入信号D延迟1拍得到的信号,同理d2是输入信号D延迟2拍得到的信号,上图同时给出了d0和D的取反信号。

可以发现:

原始信号与延迟一拍的信号 d0 的反向信号相与,就是上升沿脉冲;

而原始信号取反,然后与延迟一拍信号d0相与就是下降沿脉冲。

如果担心采样不稳定,可以利用延迟两拍的 d1 信号进行相 与。如果担心不定态,还可以将脉冲信号进行锁存。

下面给出Verilog HDL代码:

//脉冲检测

module dff(clk, D, reset, D_falling_edge, D_rising_edge);

input clk;

input D;

input reset;

output D_rising_edge,D_falling_edge;

reg d0;

reg d1;

reg Q;

always @(posedge clk or negedge reset)

begin

if(!reset)

begin

d0 <= 1'b0;

d1 <= 1'b0;

Q <= 1'b0;

end

else

begin

d0 <= D;

d1 <= d0;

Q <= d1;

end

end

assign D_falling_edge = d0 & (~D);

assign D_rising_edge = (~d0) & D;

endmodule

给出测试代码:

//测试文件

module dff_tb;

reg D;

reg clk;

reg reset;

wire D_falling_edge, D_rising_edge;

always

begin

#10 clk = ~clk;

end

initial

begin

clk = 1'b0;

reset = 1'b0;

D = 1'b0;

#30 reset = 1'b1;

#30 D = 1'b1;

#80 D = 1'b0;

end

dff u1(.clk(clk), .reset(reset), .D(D), .D_falling_edge(D_falling_edge), .D_rising_edge(D_rising_edge));

endmodule

在Modelsim进行功能仿真:

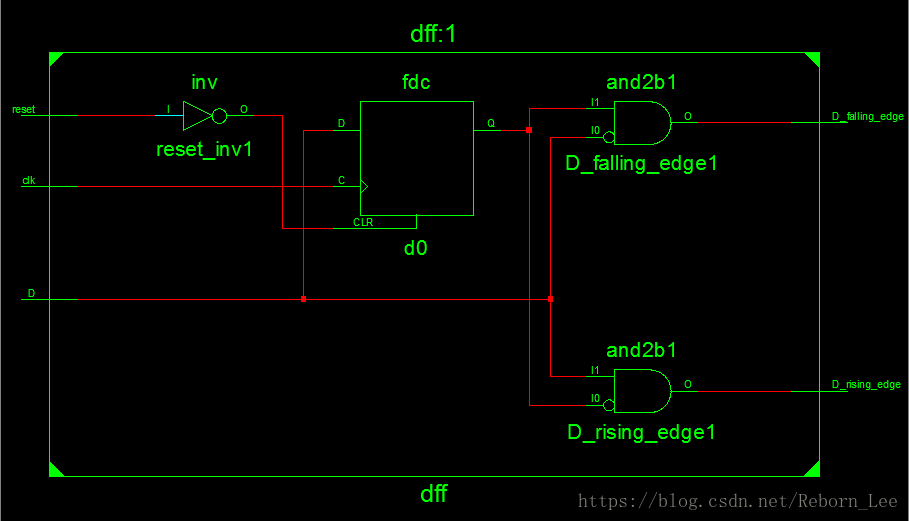

ISE中进行综合得到RTL Schematic:

这个原理图我们是可以看懂的,RTL Schematic就是寄存器传输级电路原理图,它是由各门电路组成,通过看RTL图可以初步验证自己的HDL描述是否正确。

参考文献:http://www.elecfans.com/emb/fpga/20180415662221.html

最后

以上就是落后抽屉最近收集整理的关于用移位寄存器实现边沿检测(功能仿真及ISE综合)的全部内容,更多相关用移位寄存器实现边沿检测(功能仿真及ISE综合)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复