我们设计的Verilog代码必须有对应的电路结构,这也是综合工具要求的,因为我们最终需要将代码综合后生成的配置文件烧写到FPGA中。如何快速掌握Verilog中可综合的相关语法,代码如何映射到FPGA中,我们以一个具体的例子讲解涉及的语法,将语法相关的知识放在工程实际应用中理解,没必要专门的拿本Verilog语法书看上几个月,不懂的可以直接到网上查资料就好了。

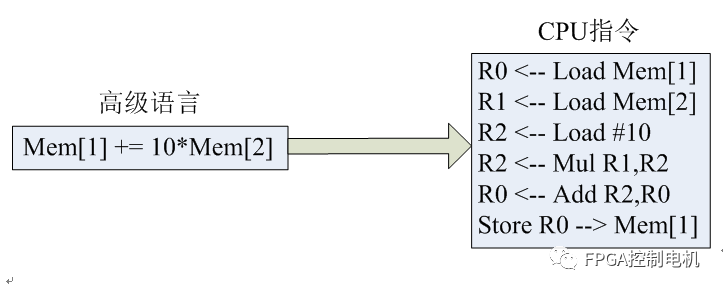

我们以高级语言编写的程序:Mem[1] += 10*Mem[2]为例讨论,

(1)、该程序在通用CPU中如何处理

(2)、该程序如何映射到FPGA

首先我们探讨Mem[1] += 10*Mem[2]是如何在CPU中运行的。

第一步:编辑工具需要将高级语言编译成机器可以阅读的语言,如图1所示,具体流程,CPU将Mem[1]中的数据搬运到R0寄存器中,将Mem[2]中的数据搬运到R1寄存器中,将数据10搬运到R2寄存器中,CPU控制R1与R2寄存器中的数据相乘结果存到R2寄存器中,CPU控制R2与R0寄存器中的数据相加结果存放到R0寄存器中,最后CPU将R0寄存器中的数据存放到Mem[1]存储器中,最后CPU释放用到的R0、R1、R2寄存器,从而完成了Mem[1] += 10*Mem[2]的全部过程。

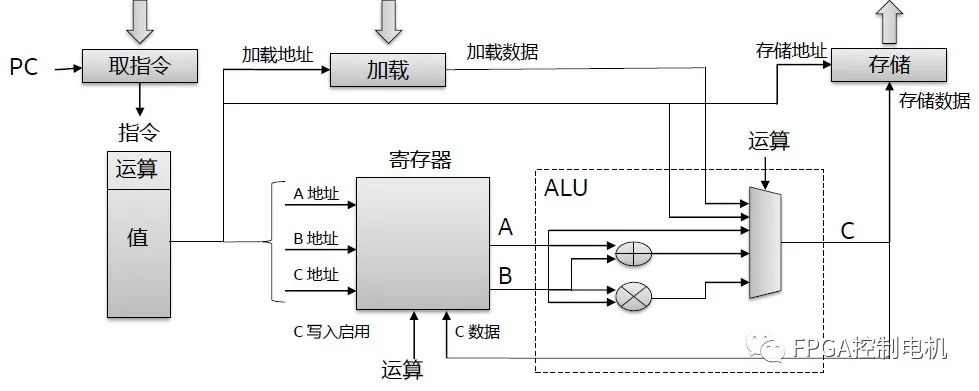

第二步:有了CPU可以理解的语言,那如何调用CPU内部的硬件实现呢。接下来我们探讨一下第一步中的算法如何在简单CPU上运行,如图2所示,CPU中最基本的硬件资源包括:取指令、寄存器、ALU、存储器等,CPU内部的架构是固定和通用的,它可以涵盖所有情况的通用数据路径,数据位宽固定,运算功能固定;CPU的处理数据的本质应该是根据指令按照一定的时序操作固定的寄存器资源。

图 1

图 2

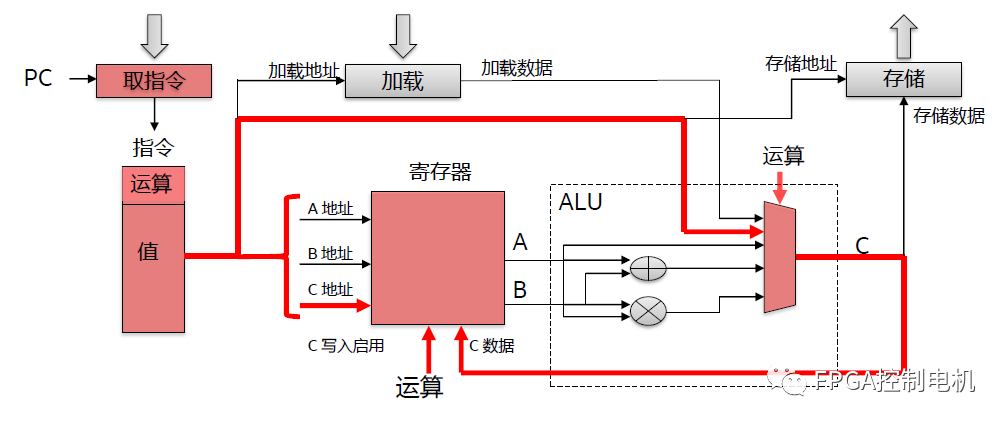

第三步:接下来我们了解一下CPU中单个指令如何工作的。如图3中红色标记的通路,灰色部分的硬件在该指令下没有参与工作,处于闲置状态;说明CPU工作时硬件资源的利用率极低。

图 3

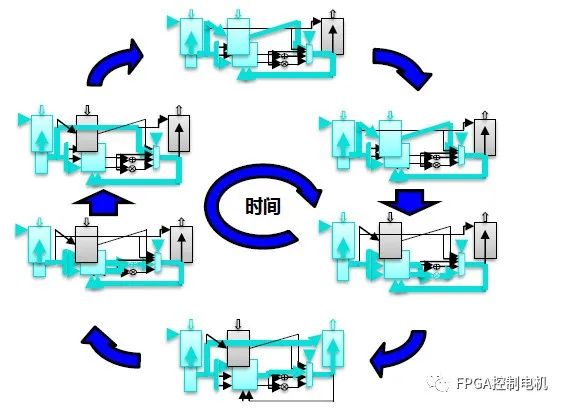

第四步:我们了解一下CPU连续工作的状态,如图4所示,CPU工作是按照顺序调用内部的硬件资源。

图 4

本期我们探讨了程序在通用CPU中如何处理,下一期我们探讨该程序如何映射到FPGA中。

得到金句:怎么改变生活?其实就是四个字:直面恐惧。--梁宁 引用得到APP产品得到金句。

最后

以上就是稳重荷花最近收集整理的关于8位寄存器verilog代码_Verilog描述语言与电路模型(四)的全部内容,更多相关8位寄存器verilog代码_Verilog描述语言与电路模型(四)内容请搜索靠谱客的其他文章。

发表评论 取消回复