我是靠谱客的博主 大胆春天,这篇文章主要介绍FPGA Implementation of BPSK Modulator and DemodulatorFPGA Implementation of DBPSK Modulator and Demodulator,现在分享给大家,希望可以做个参考。

FPGA Implementation of DBPSK Modulator and Demodulator

前言

本设计使用开发工具为Quartus prime 18.1和Matlab 2018B

工程连接:

一、方案设计

1、系统介绍

DBPSK介绍:

2DPSK又称为相对相移键控,它不是利用载波相位的绝对数值传送数字信息,而是用前后码元的相对载波相位值传送数字信息。所谓相对载波相位是指本码与前一码元初相之差。

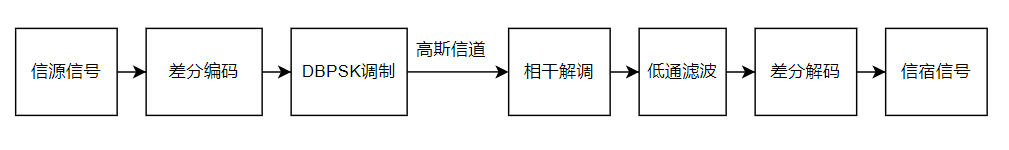

2、系统流程图

3、模块分析

3.1 信源差分编码

差分编码原理:

B(n) = A(n) ^ B(n-1)

相对码 = 绝对码 异或 相对码前一马元

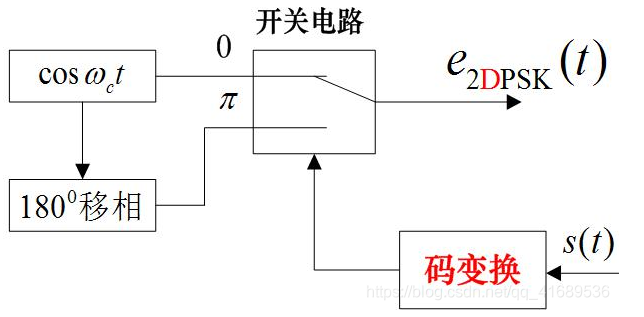

3.2 DBPSK调制

2DPSK 信号键控法调制原理框图如图所示。其中码变换是将绝对码变成相对码,开关电路的作用是当输入为 0 时,相位为 0;当输入为 1 时,相位为π。

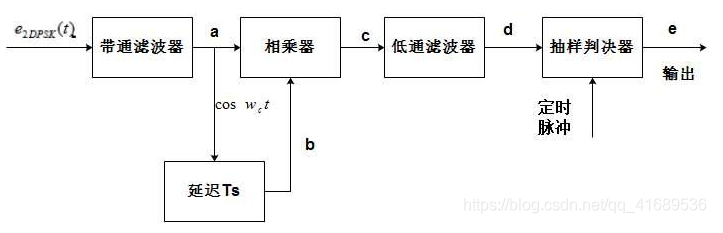

3.3 DBPSK解调

2DPSK 信号解调的一种方法是差分相干解调法。用这种方法解调不需要专门的相干载波,只需由收到的 2DPSK 信号延迟一个码元周期 TB,再与 2DPSK信号自己相乘。相乘器起到了相位比较作用,相乘结果反映了前后码元的相位差, 经低通滤波后再抽样判决,即可直接恢复出原始的二进制数字信息。

3.4 信宿差分解码

差分译码原理:

A(n) = B(n) ^ B(n-1)

绝对码 = 相对码 异或 相对码前一码元

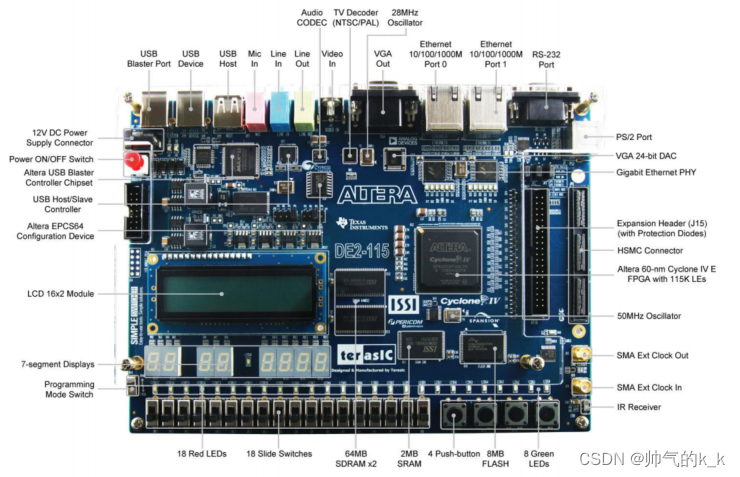

3.5 开发板DE2-115

二、matlab实现

1、 信源差分编码

%% 产生二进制序列

s=randi([0 1],max,1); %产生介于0-1之间的长度为max的1列随机序列 输入序列码元

Sinput=[]; %输入序列波形

for n=1:length(s)

if s(n)==0

A=zeros(1,Code_Len); %码元宽度为2000

else

s(n)=1;

A=ones(1,Code_Len);

end

Sinput=[Sinput A];

end

figure(1);subplot(2,1,1);plot(Sinput);

grid on;axis([0,Code_Len*length(s),-2,2]);title('输入信号波形');

%% 差分编码

Sbianma=encode(s,15,11,'hamming'); %汉明码编码后序列,一行15列的二进制数字

a1=[];%差分编码序列波形

b1=[];%解调载波

for n=1:length(Sbianma) %差分编码

if Sbianma(n)==0

B=zeros(1,Code_Len); %每个值2000个点

else

Sbianma(n)=1;

B=ones(1,Code_Len);

end

a1=[a1 B]; %s(t),码元宽度2000

c=cos(2*pi*f*t); %载波信号 0相位

b1=[b1 c]; %与s(t)等长的载波信号,变为矩阵形式

end

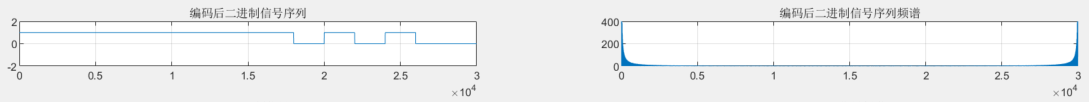

figure(2);subplot(6,2,1);plot(a1);%差分编码后序列波形

grid on; axis([0 Code_Len*length(Sbianma) -2 2]);title('编码后二进制信号序列');

figure(2);subplot(6,2,2); plot(abs(fft(a1)));%差分编码后序列频谱

grid on;axis([0 Code_Len*length(Sbianma) 0 400]);title('编码后二进制信号序列频谱');

2、 DBPSK调制

%% 调制

a2=[];%PSK调制信号波形

b2=[];%调制载波

for n=1:length(Sbianma)

if Sbianma(n)==0

C=ones(1,Code_Len); %每个值2000点

d=cos(2*pi*f*t); %载波信号 0相位

else

Sbianma(n)=1;

C=ones(1,Code_Len);

d=cos(2*pi*f*t+pi); %载波信号 Pi相位

end

a2=[a2 C]; %s(t),码元宽度2000

b2=[b2 d]; %与s(t)等长的载波信号

end

tiaoz=a2.*b2; %DBPSK e(t)调制

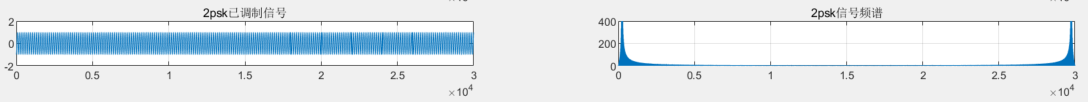

figure(2);subplot(6,2,3);plot(tiaoz);%BPDK调制信号波形

grid on; axis([0 Code_Len*length(Sbianma) -2 2]);title('2psk已调制信号');

figure(2);subplot(6,2,4); plot(abs(fft(tiaoz))); %BPDK调制信号频谱

grid on;axis([0 Code_Len*length(Sbianma) 0 400]);title('2psk信号频谱');

3、加入高斯白噪声

%% 加入高斯白噪声

%-----------------带有高斯白噪声的信道---------------------

tz=awgn(tiaoz,10); %信号tiaoz加入白噪声,信噪比为10

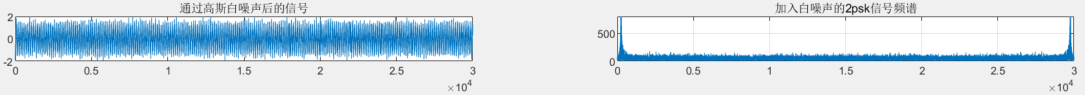

figure(2);subplot(6,2,5);plot(tz);

grid on;axis([0 Code_Len*length(Sbianma) -2 2]);title('通过高斯白噪声后的信号');

figure(2);subplot(6,2,6); plot(abs(fft(tz)));

grid on;axis([0 Code_Len*length(Sbianma) 0 800]);title('加入白噪声的2psk信号频谱');

4、 相干解调

%% 相干解调

jiet=2*b1.*tiaoz; %同步解调

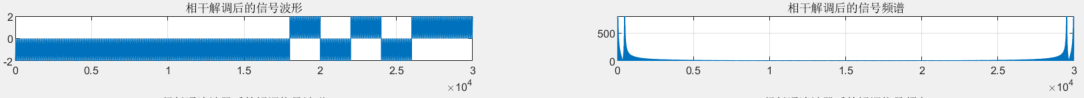

figure(2);subplot(6,2,7);plot(jiet);

grid on ;axis([0 Code_Len*length(Sbianma) -2 2]);title('相干解调后的信号波形');

figure(2);subplot(6,2,8);plot(abs(fft(jiet)));

grid on;axis([0 Code_Len*length(Sbianma) 0 800]);title('相干解调后的信号频谱');

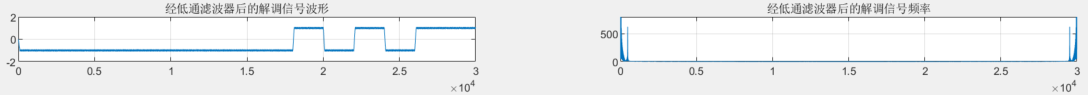

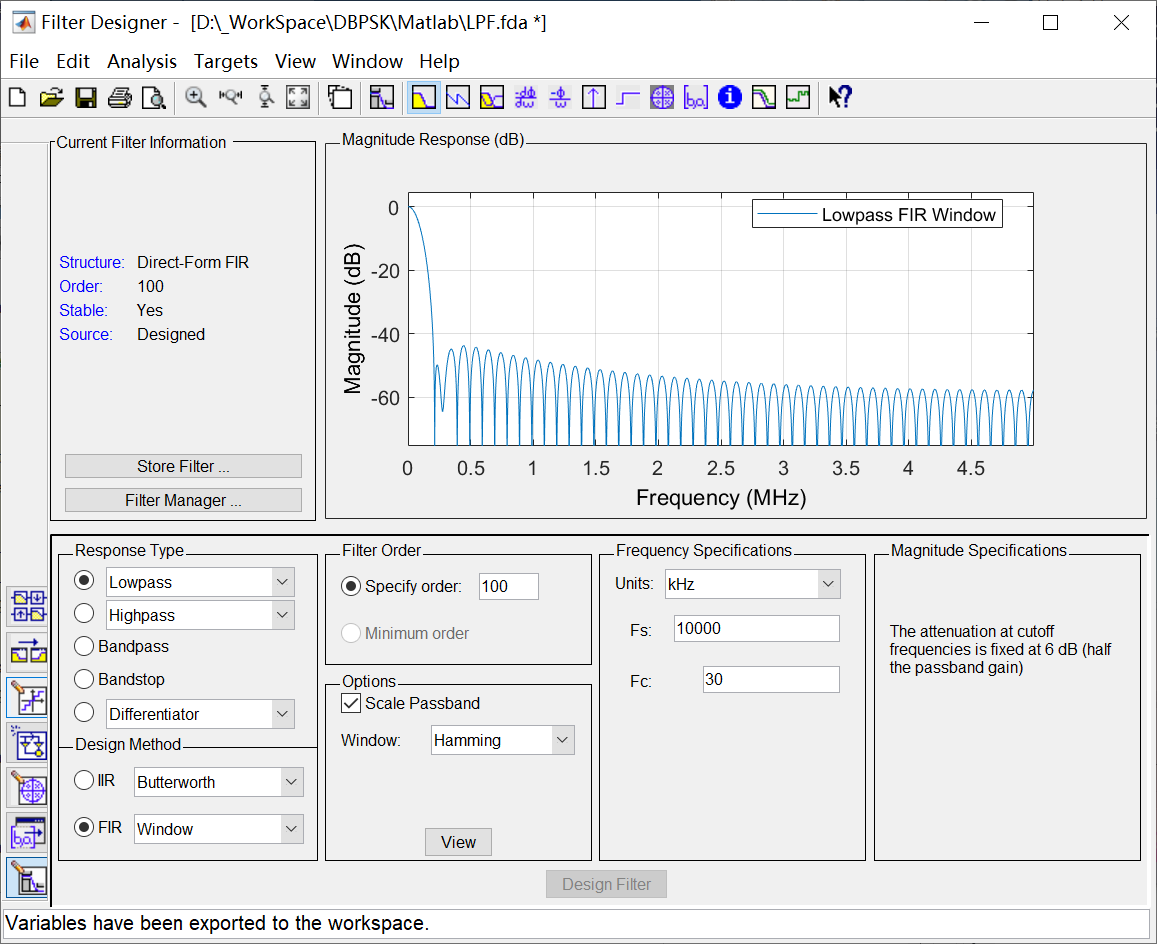

5、 低通滤波

%% FIR滤波

LPF = LPF10M_100_30K;%FIR低通滤波,采样频率10M,15阶,截止频率3M

jt = filter(LPF,jiet);%fir滤波

figure(2);subplot(6,2,9);plot(jt);

grid on ;axis([0 Code_Len*length(Sbianma) -2 2]);title('经低通滤波器后的解调信号波形');

figure(2);subplot(6,2,10);plot(abs(fft(jt)));

grid on;axis([0 Code_Len*length(Sbianma) 0 800]);title('经低通滤波器后的解调信号频率');

FIR滤波器设计

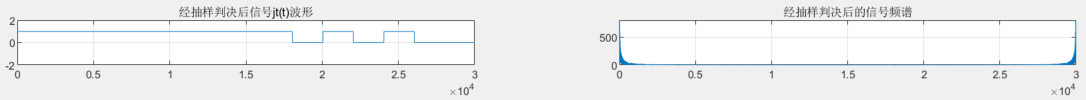

6、 抽样判决

%% 抽样判决

for m=1:Code_Len*length(Sbianma)

if jt(m)<0

jt(m)=1;

else jt(m)>0

jt(m)=0;

end

end

figure(2);subplot(6,2,11);plot(jt);

grid on ;axis([0 Code_Len*length(Sbianma) -2 2]);title('经抽样判决后信号jt(t)波形');

figure(2);subplot(6,2,12);plot(abs(fft(jt)));

grid on;axis([0 Code_Len*length(Sbianma) 0 800]);title('经抽样判决后的信号频谱');

7、 信宿差分解码

%% 差分解码

n=1:Code_Len:Code_Len*length(Sbianma);

a5=[];

a5=[a5 jt(n)];

s1=decode(a5,15,11,'hamming'); %汉明译码

a6=[];

for n=1:length(s1)

if s1(n)==0

G=zeros(1,Code_Len);

else

s1(n)=1;

G=ones(1,Code_Len);

end

a6=[a6 G];

end

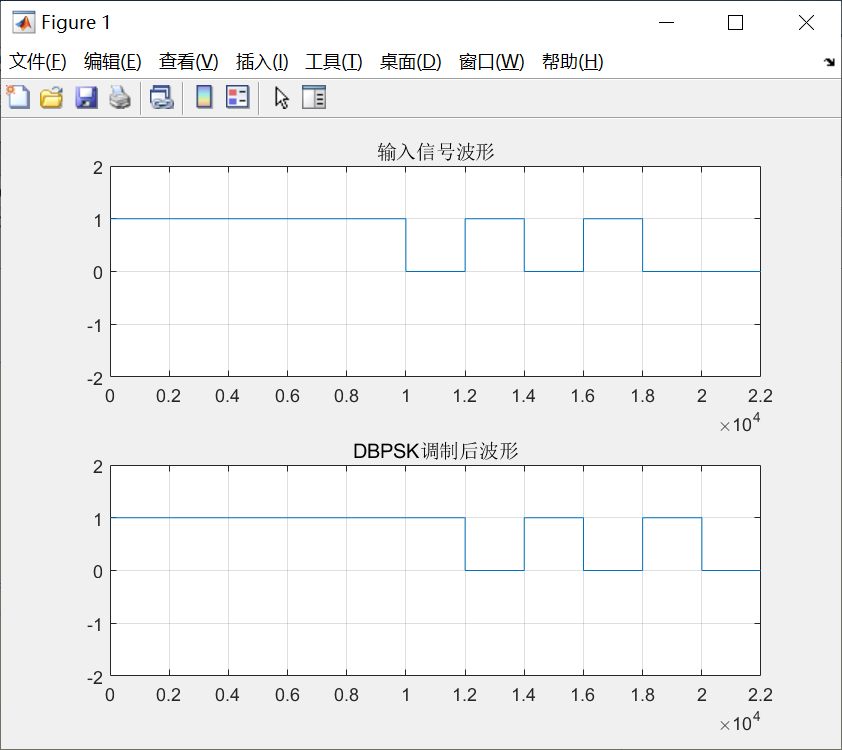

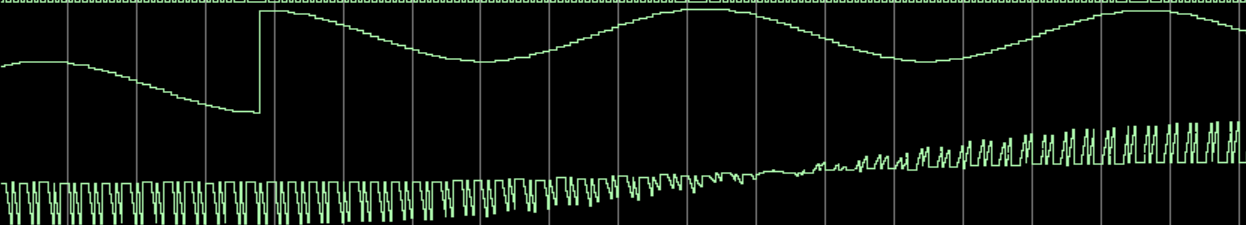

figure(1);subplot(2,1,2);plot(a6);

grid on;axis([0 Code_Len*length(s) -2 2]);title('DBPSK调制后波形');

输入信号和输出信号对比

三、FPGA实现

1、随机序列生成

/*

m:x^8+x^4+x^3+x^2+1

*/

module msequence8#(

parameter seed= 8'b1111_1111

)(

input clk,

input rst_n,

input en,

output reg [31:0]num,

output mse8, //m sequence

output reg [7:0]rand8

);

assign mse8 = rand8[0];

always @ (posedge clk or negedge rst_n)begin

if(!rst_n) begin

rand8 <= seed;

num <= 32'd1;

end

else if(en) begin

rand8[0] <= rand8[1];

rand8[1] <= rand8[2];

rand8[2] <= rand8[3];

rand8[3] <= rand8[4];

rand8[4] <= rand8[5];

rand8[5] <= rand8[6];

rand8[6] <= rand8[7];

rand8[7] <= rand8[0] ^ rand8[4] ^ rand8[5] ^ rand8[6];

num <= num + 1'b1;

end

else

rand8 <= rand8;

end

endmodule

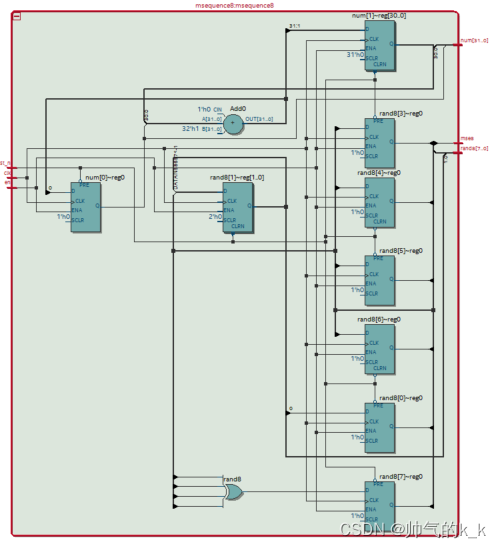

RTL视图:

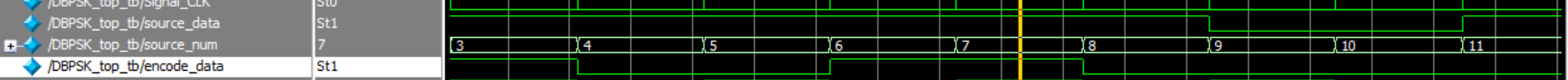

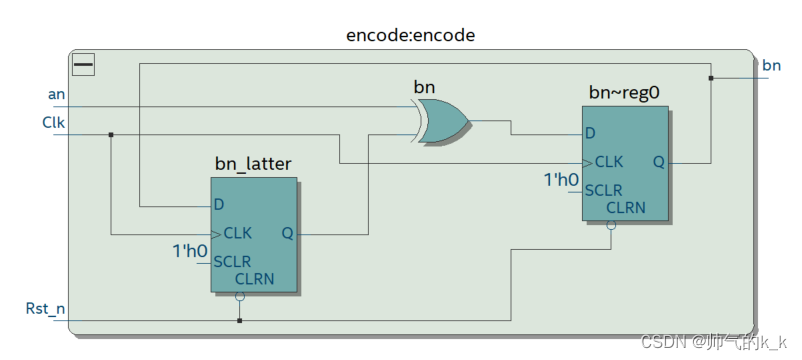

2、 信源差分编码

module encode(

input Clk,

input Rst_n,

input an,//绝对码

output reg bn//相对码

);

reg bn_latter;//相对码前一码元

always@(posedge Clk or negedge Rst_n)begin

if(!Rst_n)

bn_latter <= 0;

else

bn_latter <= bn;

end

always@(posedge Clk or negedge Rst_n)begin

if(!Rst_n)

bn <= 0;

else

bn <= an ^ bn_latter;

end

endmodule

RTL:

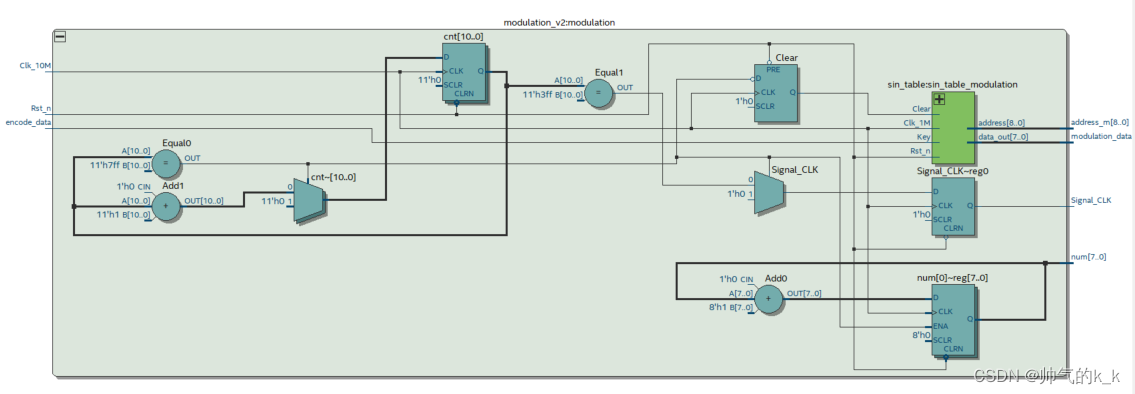

3、 DBPSK调制

module modulation_v2(

input Clk_10M,

input Rst_n,

// input [31:0]data_in,//串行差分编码信号输入

input encode_data,

output reg Signal_CLK,//码元同步时钟

output reg [7:0]num,

output [8:0]address_m,

output signed [7:0]modulation_data//调制信号输出

);

reg [10:0]cnt;

reg Clear;

always @(posedge Clk_10M, negedge Rst_n)begin

if (!Rst_n) begin

cnt <= 11'd0;

num <= 8'd0;

Clear <= 1;

Signal_CLK <= 1'b0;

end

else if (cnt == 11'd2047)begin

cnt <= 11'd0;

num <= num + 1'b1;

Clear <= 0;

Signal_CLK <= 1'b0;

end

else if (cnt == 11'd1023)begin

cnt <= cnt + 1'b1;

num <= num;

Clear <= 1;

Signal_CLK <= 1'b1;

end

else begin

cnt <= cnt + 1'b1;

num <= num;

Clear <= 1;

Signal_CLK <= 1'b0;

end

end

//调制载波

sin_table sin_table_modulation(

.Clk_1M(Clk_10M),//10M

.Rst_n(Rst_n),

.Clear(Clear),

.Key(encode_data),

.address(address_m),

.data_out(modulation_data)//80K

);

endmodule

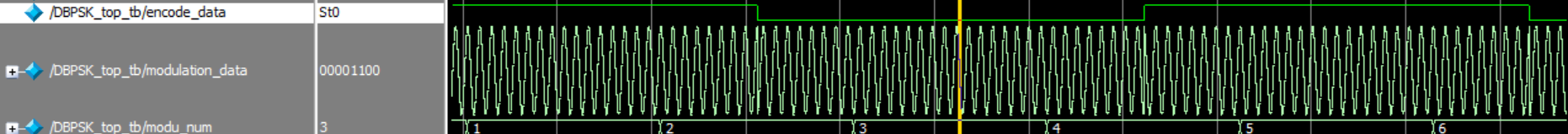

RTL视图:

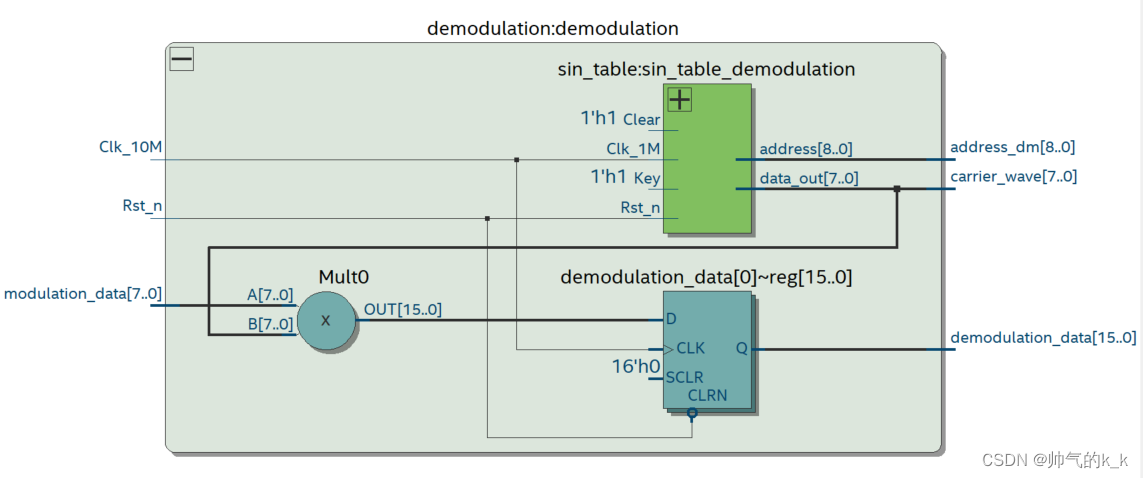

4、 相干解调

module demodulation(

input Clk_10M,

input Rst_n,

input signed [7:0]modulation_data,

output signed [7:0]carrier_wave,

output [8:0]address_dm,

output reg signed [15:0]demodulation_data

);

//解调载波

sin_table sin_table_demodulation(

.Clk_1M(Clk_10M),//1M

.Rst_n(Rst_n),

.Clear(1'b1),

.Key(1'b1),

.address(address_dm),

.data_out(carrier_wave)//8K

);

//载波相乘

always @(posedge Clk_10M, negedge Rst_n)begin

if (!Rst_n)

demodulation_data <= 16'd0;

else

demodulation_data <= modulation_data * carrier_wave;

end

endmodule

RTL视图:

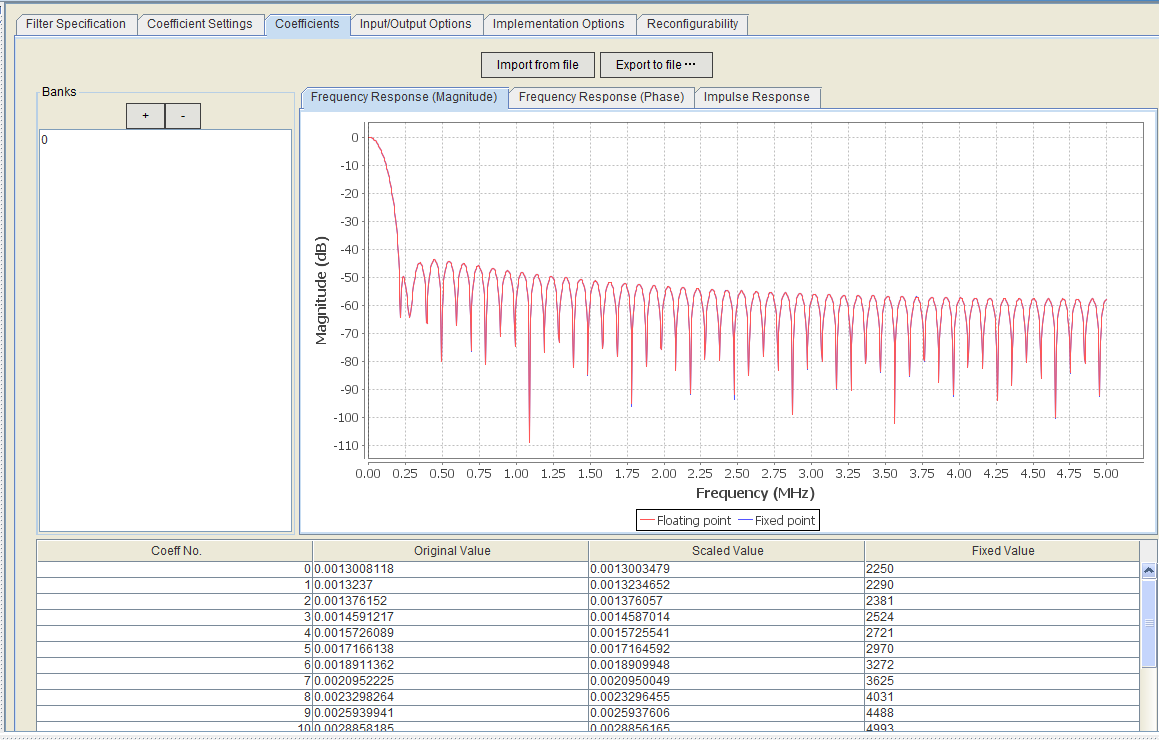

5、 低通滤波

FIR IP核调用

//低通滤波

//wire [37:0]fir_out;

wire ast_source_valid;

wire [1:0]ast_source_error;

reg [6:0]cnt1;

//reg extract_signal;//0.1ms定时提取信号

assign demd_bitstream = fir_out[38];

FIR FIR(

.clk(Clk_50M), // clk

.reset_n(Rst_n), // rst.reset_n

.ast_sink_data(demodulation_data), // avalon_streaming_sink.data

.ast_sink_valid(Fs_10M), // fs

.ast_sink_error(2'd0), // .error

.ast_source_data(fir_out), // avalon_streaming_source.data

.ast_source_valid(ast_source_valid), // .valid

.ast_source_error(ast_source_error) // .error

);

6、 抽样判决

always @(posedge Fs_1M, negedge Rst_n)begin//0.1ms定时提取信号

if (!Rst_n)begin

cnt1 <= 7'd0;

extract_signal <= 1'b0;

end

else if (cnt1 == 7'd100)begin

cnt1 <= 7'd0;

extract_signal <= fir_out[38];

end

else begin

cnt1 <= cnt1 + 1'b1;

extract_signal <= extract_signal;

end

end

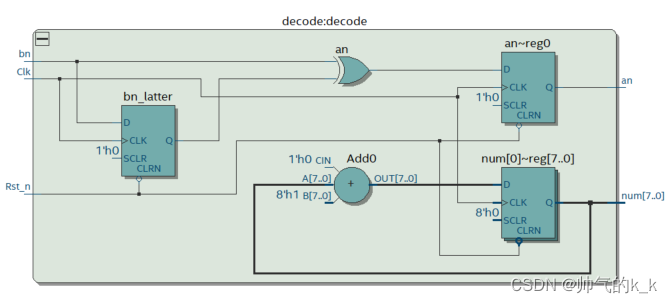

7、 信宿差分解码

module decode(

input Clk,

input Rst_n,

input bn,//相对码

output reg [7:0]num,

output reg an//绝对码

);

reg bn_latter;//相对码前一码元

always@(posedge Clk or negedge Rst_n)begin

if(!Rst_n)

bn_latter <= 0;

else

bn_latter <= bn;

end

always@(posedge Clk or negedge Rst_n)begin

if(!Rst_n)begin

an <= 0;

num <= 8'd0;

end

else begin

an <= bn ^ bn_latter;

num <= num + 1'b1;

end

end

endmodule

RTL视图:

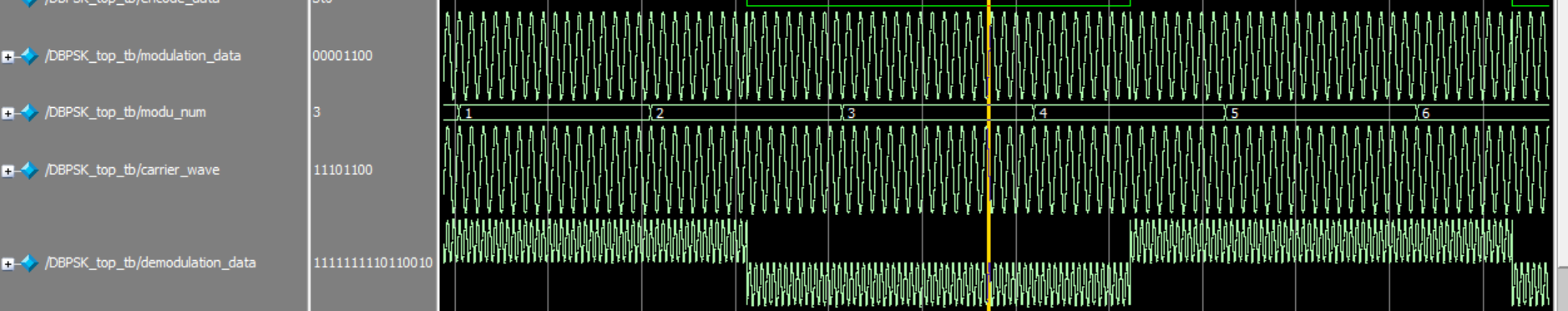

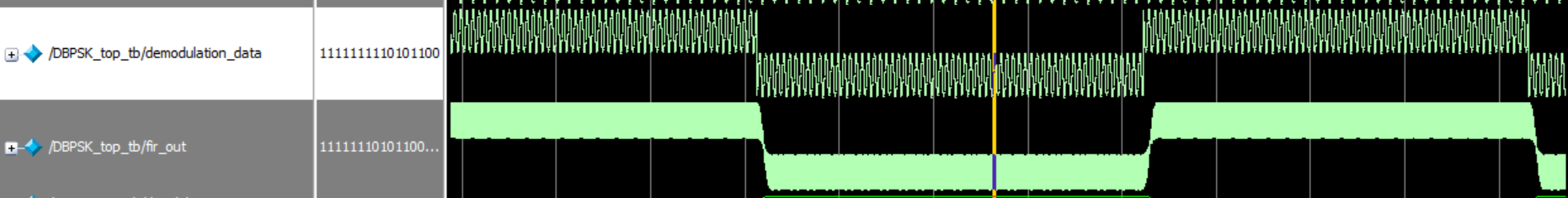

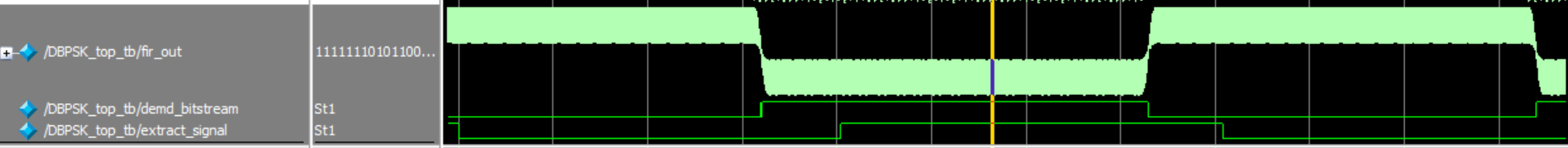

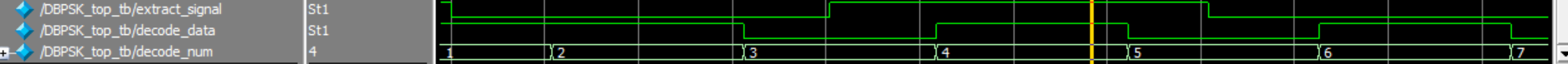

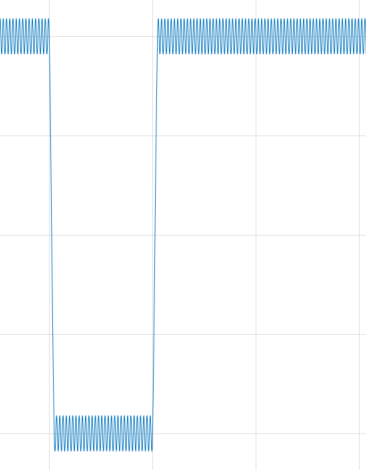

四、结果分析

浮点定点对比

matlab浮点:

FPGA定点:

对比结果:

浮点效果比定点好

五、产考资料

- https://blog.csdn.net/john_cxc/article/details/104928736

- https://www.docin.com/p-320216290.html

最后

以上就是大胆春天最近收集整理的关于FPGA Implementation of BPSK Modulator and DemodulatorFPGA Implementation of DBPSK Modulator and Demodulator的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复