| @GZMTU_DZXXGCWHB 基于FPGA的2FSK调制解调器 设计要求:

目录 第一部分:实训目的 第二部分:实训准备(包含实训设备及器材) 第三部分:实训要求 第四部分:实训内容 2FSK调制器设计 2FSK信号调制仿真结果 分频法实现2FSK解调器 包络检波法 2FSK信号解调仿真结果 在线逻辑分析仪(ILA) 整体电路 第五部分:源代码 M序列发生器 ROM地址发生器0 ROM地址发生器1 开关选通器 对输入正弦波信号进行整形 微分操作 实现脉冲展宽 第六部分:实训结果 2FSK信号的调制 2FSK信号的解调 实物图 第一部分:实训目的数字调制技术是现代通信的一个重要内容,在数字通信系统中,由于数字信号具有丰富的低频成份,不宜进行无线传输或长距离电缆传输,因而需要将基带信号进行数字调制(Digital Modulation)。数字调制同时也是数字信号频分复用的基本技术。数字调制与模拟调制都属于正弦波调制,但是,数字调制是调制信号为数字型的正弦波调制,因而数字调制具有自身的特点,一般说来数字调制技术分为两种类型:一是把数字基带信号当作模拟信号的特殊情况来处理;二是利用数字信号的离散取值去键控载波,从而实现数字调制。后一种方法通常称为键控法。例如可以对载波的振幅、频率及相位进行键控,便可获得振幅键控(ASK)、移频键控(FSK)、相移键控(PSK)等调制方式。移频键控(FSK)是数字信息传输中使用较早的一种调制形式,它由于其抗干扰及衰落性较好且技术容易实现,因而在集散式工业控制系统中被广泛采用。以往的键控移频调制解调器采用“定功能集成电路+连线”式设计;集成块多,连线复杂,容易出错,且体积较大,本设计采用 Xilinx公司的 FPGA 芯片,有效地缩小了系统的体积,降低了成本,增加了可靠性,同时系统采用Verilog语言进行设计,具有良好的可移植性及产品升级的系统性。 |

第二部分:实训准备(包含实训设备及器材)

|

第三部分:实训要求1、 用Verilog实现2FSK调制和解调; 2、 对任意输入二进制数进行调制,并解调。载波频率分别为32MHz和20MHZ; 3、 分别对调制和解调结果仿真。 |

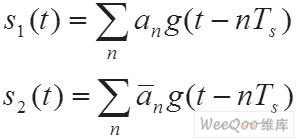

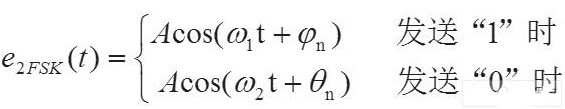

第四部分:实训内容调制信号是二进制数字基带信号时,这种调制称为二进制数字调制。在二进制数字调制中,载波的幅度、频率和相位只有两种变化状态。相应的调制方式有二进制振幅键控(2ASK),二进制频移键控(2FSK)和二进制相移键控(2PSK)。2FSK就是用两种不同频率的载波来传送数字信号。特别适合应用于衰落信道,其占用频带较宽,频带利用率低,实现起来较容易,抗噪声与抗衰减的性能较好,在中低速数据传输中得到了广泛的应用。 1 调制解调的基本原理 FSK就是利用载波信号的频率变化来传递数字信息。 在2FSK中,载波的频率随二进制基带信号在f1和f2两个频率点之间变化。故其表达式为:

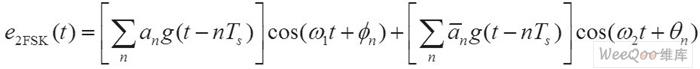

也就是说,一个2FSK信号可以看成是两个不同载频的2ASK信号的叠加。因此,2FSK信号的时域表达式又可以写成:

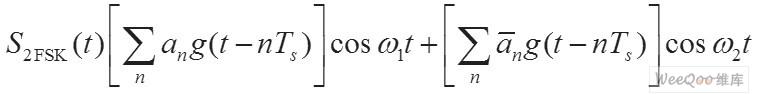

在移频键控中, 和 不携带信息,通常可以令和 为零。因此,2FSK信号的表达式可简化为:

其中:  2FSK信号的产生方法主要有两种。一种可以采用模拟调频电路来实现,另一种可以采用键控法来实现,即在二进制基带矩形脉冲序列的控制下通过开关电路对两个不同的独立频率源进行选通,使其在每个码元Ts期间输出f1或f2两个载波之一。这种方法产生2FSK信号的差异在于:由调频法产生的2FSK信号在相邻码元之间的相位是连续变化的。而键控法产生的2FSK信号,是由电子开关在两个独立的频率源之间转换形成,故相邻码元之间的相位不一定连续。 针对FSK信号的特点,我们可以提出基于FPGA的FSK调制器的一种实现方法--分频法,这种方法是利用数字信号去控制可变分频器的分频比来改变输出载波频率,产生一种相位连续的FSK信号,而且电路结构简单,容易实现。在2FSK信号中,载波频率随着二元数字基带信号(调制信号)的“1”或“0”而变化,“1”对应于频率为f1的载波,“0”对应于频率为f2的载波。2FSK的已调信号的时域表达式为:

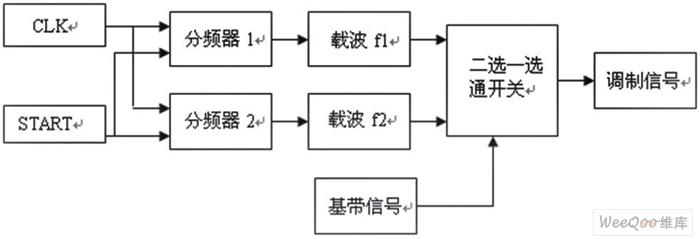

2FSK信号的常用解调方法是采用非相干解调和相干解调。其解调原理是将2FSK信号分解为上下两路2ASK信号分别进行解调,然后进行判决。这里的抽样判决是直接比较两路信号抽样值的大小,可以不专门设置门限。 判决规则应与调制规则相呼应,调制时若规定“1”符号对应载波频率f1,则接收时上支路的样值较大,应判为“1”,反之则判为“0”。 2FSK调制器设计键控法也常常利用数字基带信号去控制可变分频器的分频比来改变输出载波频率,从而实现FSK的调制。实现2FSK调制的原理方框图如图1所示。

其中FSK调制的核心部分包括分频器、二选一选通开关等,图中的两个分频器分别产生两路数字载波信号;二选一选通开关的作用是以基带信号作为控制信号,当基带信号为“0”时,选通载波f1;当基带信号为“1”时,选通载波f2。从选通开关输出的信号就是数字FSK信号。这里的调制信号为数字信号。 2FSK信号调制仿真结果整个设计使用Verilog语言编写,以Xilinx Zynq-7020 SoC为下载的目标芯片,在Vivado软件平台上进行布局布线后进行波形仿真,其中200MHZ为输入主时钟信号;start为起始信号,当out为“1”的时候,开始解调;rd_data0、rd_data1为载波信号;out为基带信号;

dout为经过FSK调制器后的调制信号;当输入的基带信号out=‘0’时,输出的调制信号dout为f1,当输入的基带信号out=‘1’时,输出的调制信号dout为f2。 2FSK解调器设计 分频法实现2FSK解调器过零检测法与其他方法比较,最明显的优点就是结构简单、易于实现,而且对增益起伏不敏感,特别适用于数字化实现。它是一种经济、实用的最佳数字解调方法。

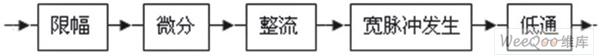

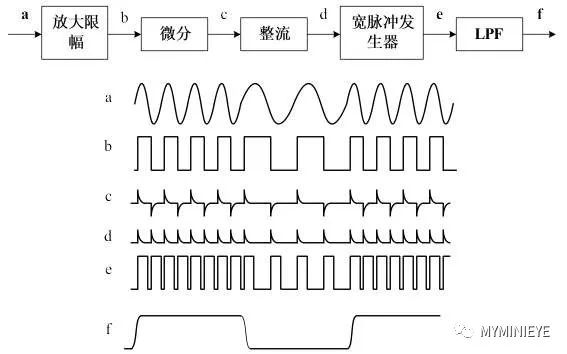

FSK过零检测法。 它利用信号波形在单位时间内与零电平轴交叉的次数来测定信号频率。输入的已调信号经限幅放大后成为矩形脉冲波,再经微分电路得到双向尖脉冲,然后整流得到单向尖脉冲,每个尖脉冲代表信号的一个过零点,尖脉冲重复的频率是信号频率的两倍。将尖脉冲去触发一单稳态电路,产生一定宽度的矩形脉冲序列,该序列的平均分量与脉冲重复频率,即输入频率信号成正比。所以经过低通滤波器的输出平均量的变化反映了输入信号的变化,这样就完成了频率-幅度的变换,把码元“1”与“0”在幅度上区分开来,恢复出数字基带信号。实现2FSK解调器的原理方框图如图所示。

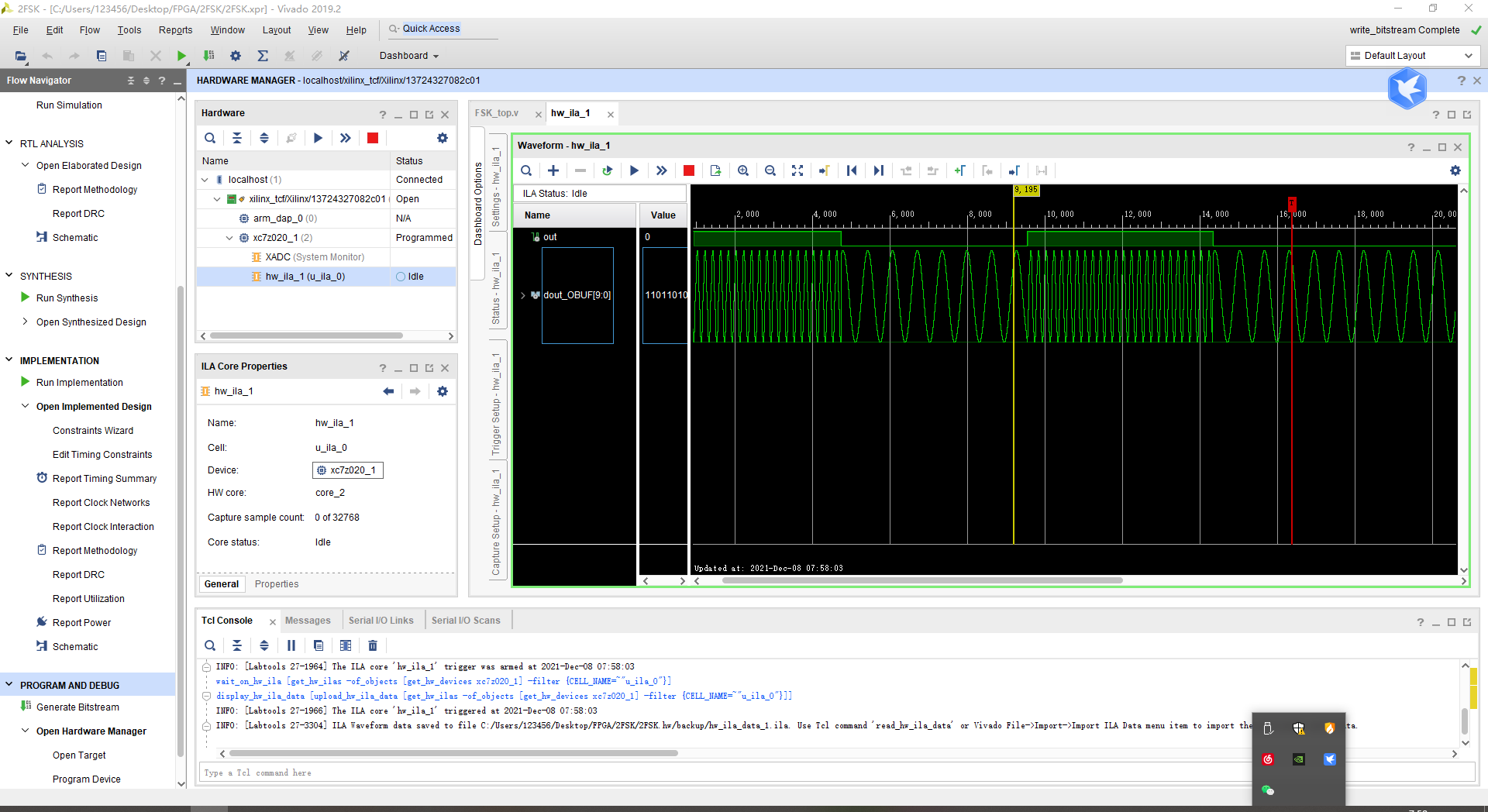

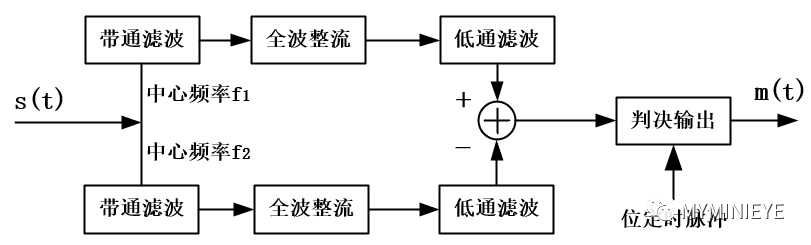

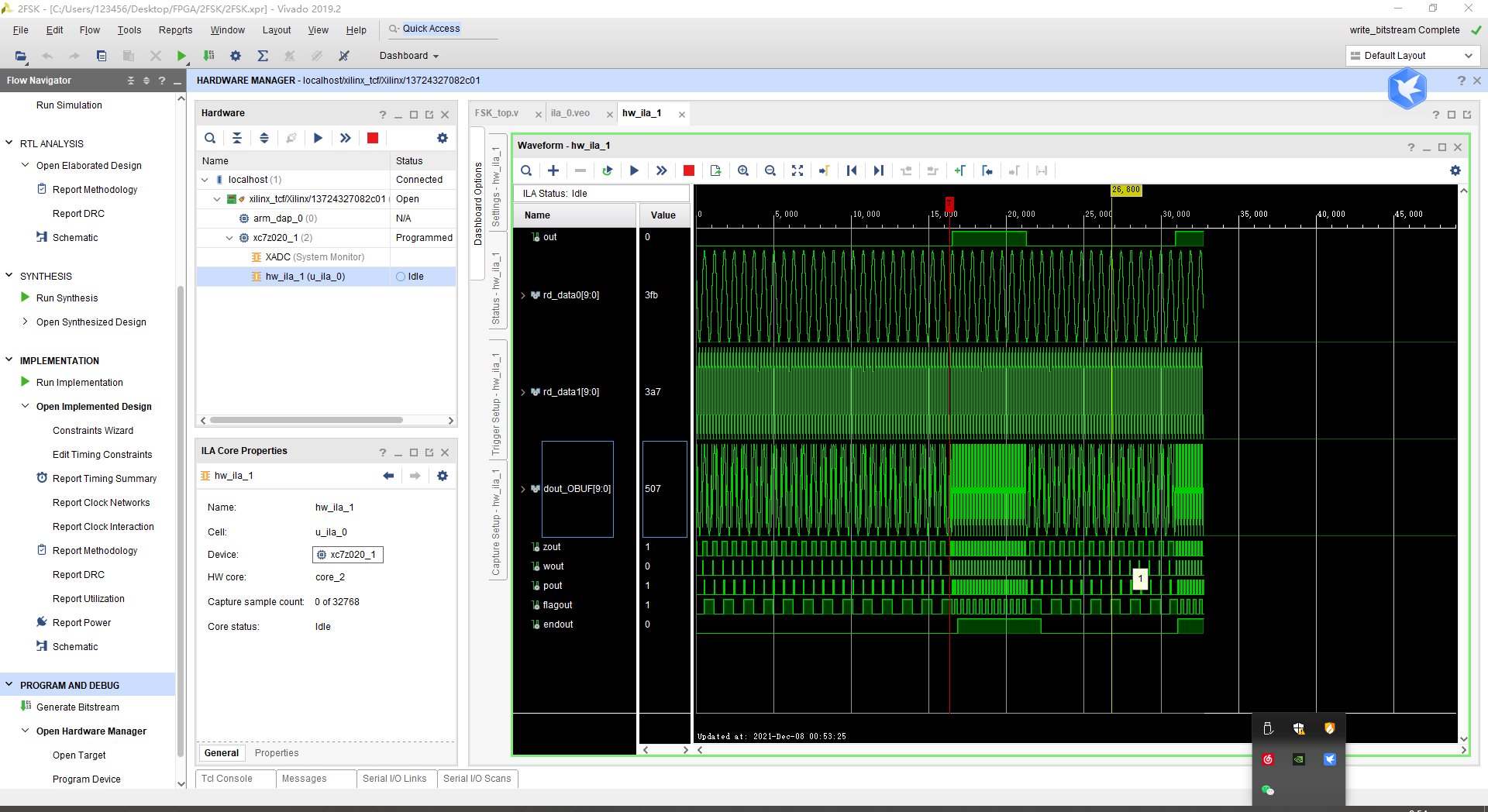

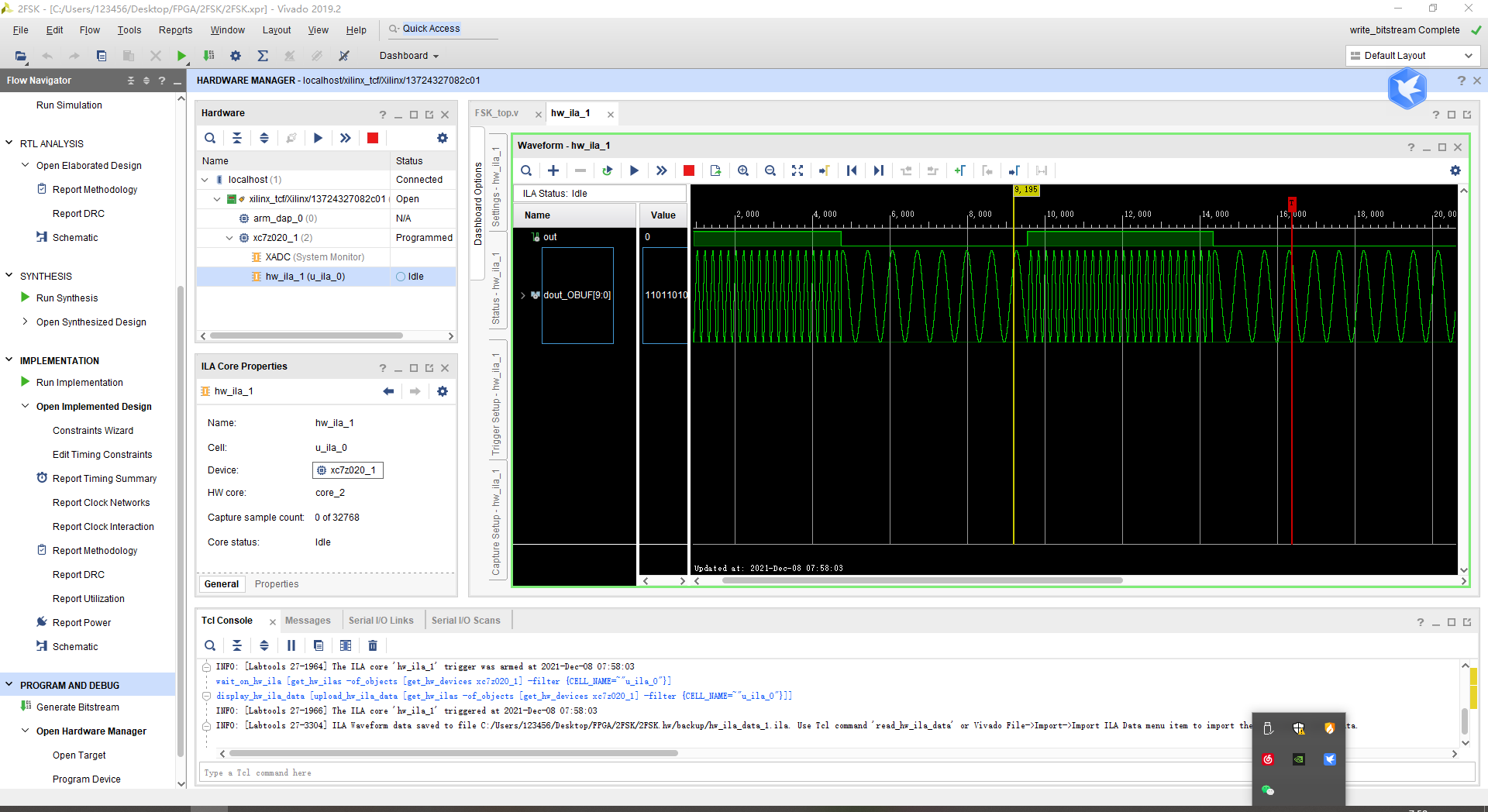

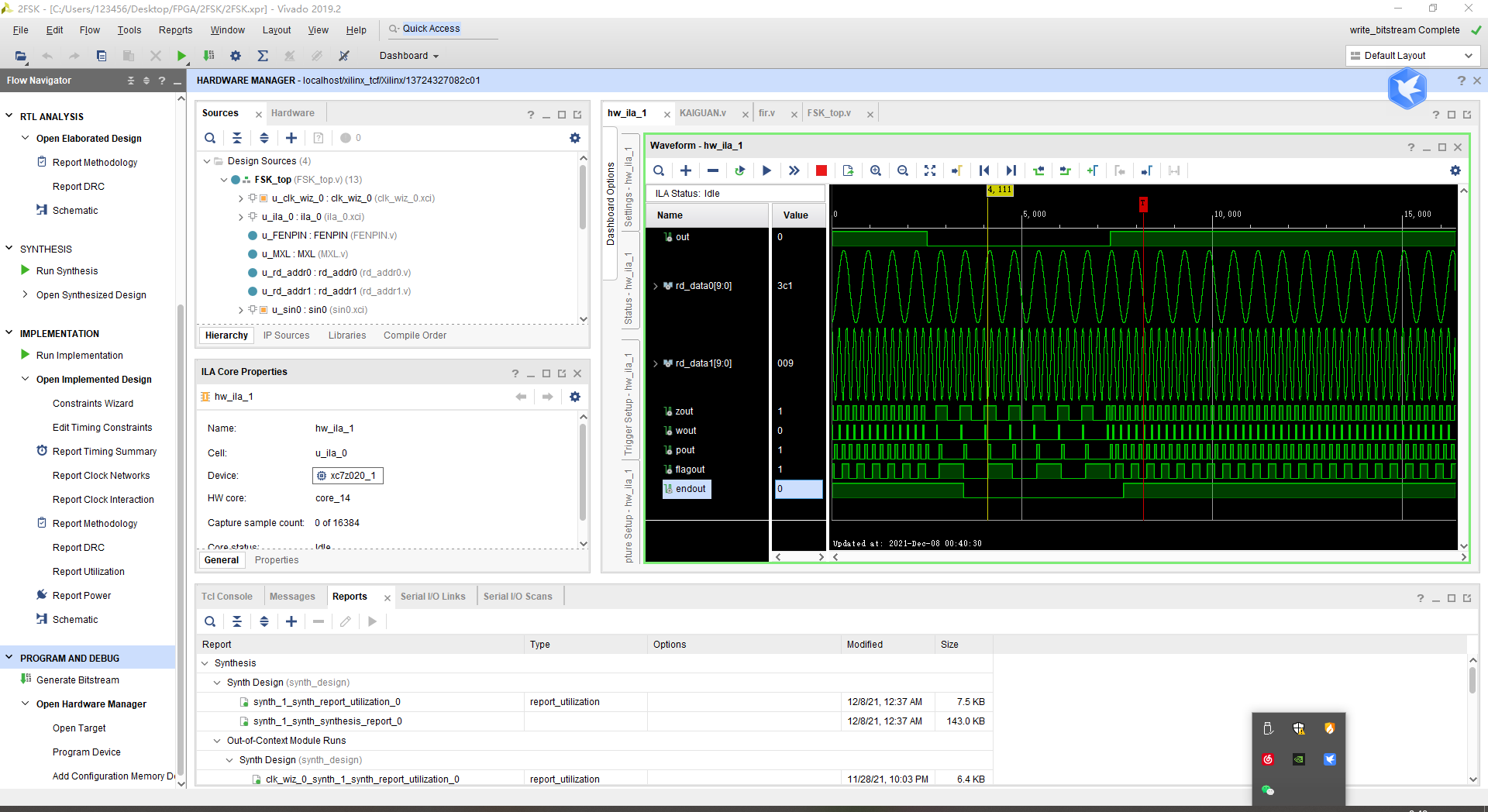

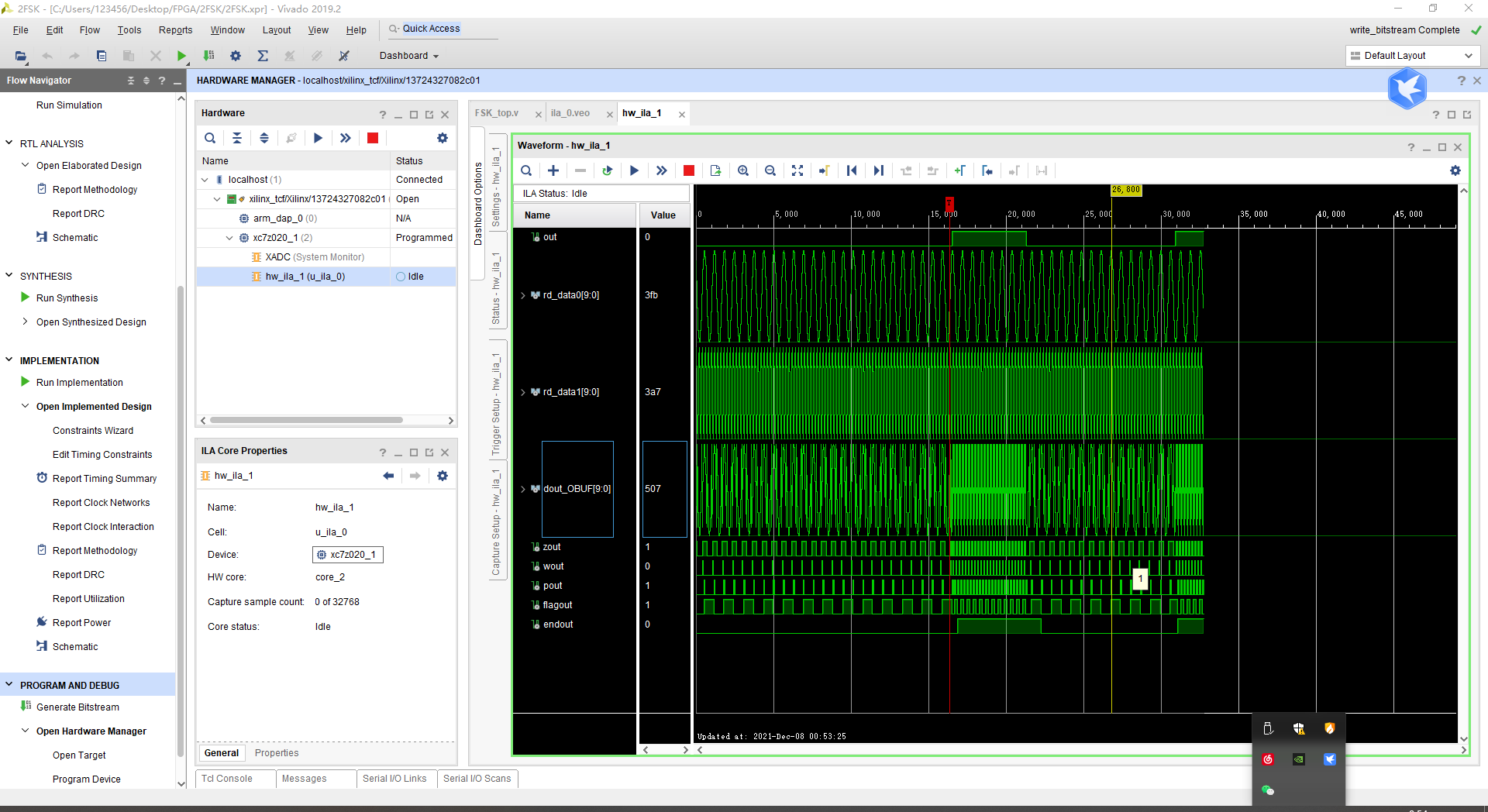

FSK信号经过限幅、微分、整流后形成与频率变化相对应的脉冲序列,由此再形成 相同宽度的矩形脉冲,矩形脉冲的低频分量与数字信号相对应,由滤波器滤出低频分量, 然后经抽样判决,即可得到原始的数字调制信号。 包络检波法2FSK的包络检波法解调原理如下,可视为由两路2ASK解调电路组成,这里两个带通滤波器,对应两个中心频率,用以分开两路2ASK信号,将两路滤波之后的包络信号相减,在经过抽样判决其进行判决,根据调制规则(f1代表符号1,f2代表符号0),当判决值大于0时,判决为1,否则判决为0。 包络检波首先需要通过带通滤波器将FSK信号进行滤波分离,显然,当调制度较 小的时候,两路FSK信号频谱混叠严重,带通滤波器的通带比较窄,能量损失比较严重,会引入另一路信号的频谱干扰,因此性能下降严重,通常需要调制度大于2的时候才能获得较好测性能。 2FSK信号解调仿真结果整个设计使用Verilog语言编写,以Xilinx Zynq-7020 SoC为下载的目标芯片,在Vivado软件平台上进行布局布线后进行波形仿真,其中dout为输入信号,本文中在调制阶段的被调制信号,即是调制信号中的输出信号,dout为输出信号,在正常情况下out就是在调制信号中的输入信号,在flagout=1时,cnt开始计数。通过判断cnt的数值大小,来解调输出信号dout。 调制解调器设计仿真结果如下图所示。比较输入信号out与输出信号endout,完全一样,只是系统仿真结果有一定的延时。仿真结果表明,系统设计正确 。

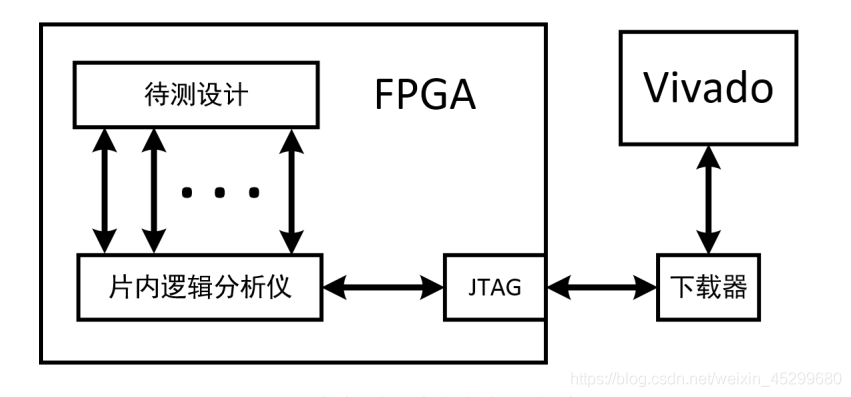

在线逻辑分析仪(ILA)Vivado的在线逻辑分析仪(ILA)其借用了传统逻辑分析仪的理念以及大部分的功能, 并利用 FPGA 中的逻辑资源, 将这些功能植入到 FPGA 的设计当中。如下图所示,ILA占用一部分FPGA内部逻辑资源,可看做一个模块,被设计模块所调用。ILA使用时需要与下载器连接,将FPGA的测试信号传回到vivadoIDE中,显示波形以供调试。运行过程如下:

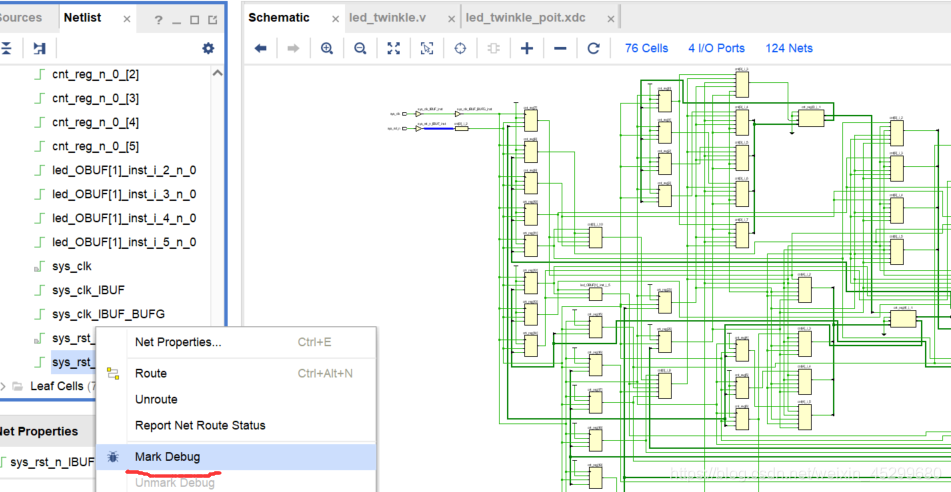

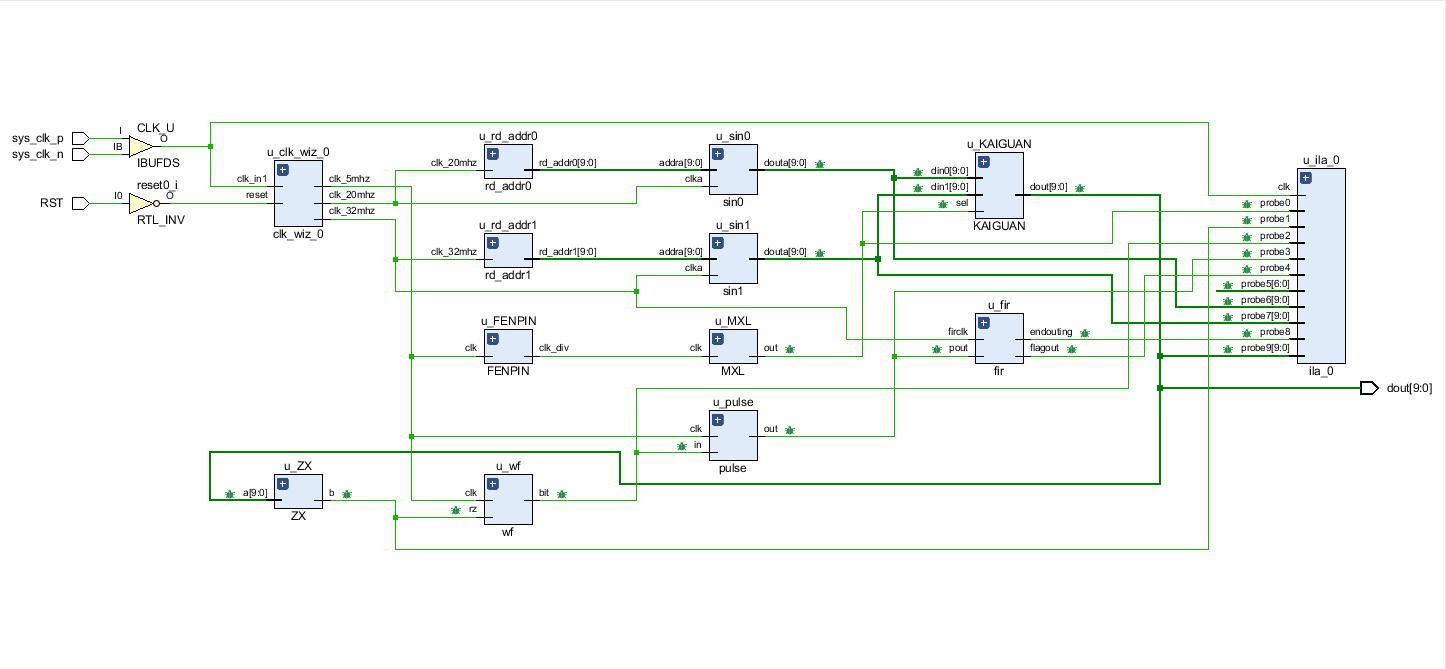

整体电路Vivado可实现硬件描述语言或网表文件(VHDL、Verilog、BDF、TDF、EDIF、 VQM)对应的RTL电路图的生成。其方法为:选择Tools︱RTL Viewer,可以打开FSK 工程个层次的RTL电路图,双击图形中有关模块,或选择左侧各项,可了解个层次的电路结构,如下图所示

第五部分:源代码(由于程序编写工程较复杂,仅贴出部分程序,更多详情请查看随文档附的Vivado项目工程) M序列发生器module MXL( input clk, output out ); reg out; reg[3:0] tmp = 4'b0; always @(posedge clk )begin if(tmp > 4'd15) tmp<=4'd0; else tmp<=tmp+1'b1; case(tmp) 4'd0:out<=0; 4'd1:out<=1; 4'd2:out<=0; 4'd3:out<=0; 4'd4:out<=1; 4'd5:out<=1; 4'd6:out<=0; 4'd7:out<=1; 4'd8:out<=1; 4'd9:out<=0; 4'd10:out<=1; 4'd11:out<=0; 4'd12:out<=0; 4'd13:out<=0; 4'd14:out<=0; 4'd15:out<=0; endcase end endmodule ROM地址发生器0module rd_addr0( input clk_20mhz, output reg [9:0] rd_addr0 //读ROM地址 ); reg rd_addr0; always@(posedge clk_20mhz)begin rd_addr0 <= rd_addr0 + 10'd1; end endmodule ROM地址发生器1module rd_addr1( input clk_32mhz, output reg [9:0] rd_addr1 //读ROM地址 ); reg rd_addr1; always@(posedge clk_32mhz)begin rd_addr1 <= rd_addr1 + 10'd1; end endmodule 开关选通器module KAIGUAN( input [9:0] din0, output [9:0] dout, input [9:0] din1, input sel ); wire [9:0] MW_din0l; wire [9:0] MW_din1l; reg [9:0] MW_dtempl; always@(sel) begin case(sel) 1'd0:MW_dtempl <= MW_din0l; default:MW_dtempl <= MW_din1l; endcase end assign dout = MW_dtempl; assign MW_din0l = din0; assign MW_din1l = din1; endmodule 对输入正弦波信号进行整形module ZX( input [9:0] a, output b ); reg b; always @(a[9:0]) case({a[9],a[8]}) 2'b11:b<=1; 2'b00:b<=0; 2'b10:b<=1; 2'b01:b<=0; //按高两位进行判决 endcase endmodule 微分操作module wf( input clk, input rz, output reg bit ); reg [1:0]pre; always @(posedge clk) begin pre[1]=pre[0]; pre[0]=rz; if(pre==2'b01) //上升边沿检测,即微分 bit<=1; else bit<=0; end endmodule 实现脉冲展宽module pulse( input in, input clk, output out ); wire out; reg delay1; reg delay2; reg delay3; always@(posedge clk) begin delay1 <= in; delay2 <= delay1; delay3 <= delay2; end assign out = delay2 + delay3; endmodule module fir( input firclk, input pout, output endouting, output reg flagout ); reg endout; reg [6:0] cnt; always@(posedge pout) //检测pout高电平标志位flag = 1 第二次高电平为2 begin if(flagout == 2) flagout <= 1; else flagout <= flagout + 1; end always@(posedge firclk) begin //检测频率计数器 if (flagout == 1) cnt <= cnt + 1; else cnt <= 0; end always@(posedge ~flagout) begin //检测频率计数器 if (cnt >= 101) endout <= 1; else if(cnt < 102) endout <= 0; else endout <= ~endout; end //信号输出 assign cntou = cnt; assign endouting = ~endout; endmodule 参考文献 |

第六部分:实训结果如下图,成功实现对实训要求各功能的实现: 2FSK信号的调制

2FSK信号的解调 实物图

|

| 资源:Xiinx_FPGA_2fsk调制-硬件开发文档类资源-CSDN下载 资源:Quarter_2FSK_调制解调-硬件开发文档类资源-CSDN下载 |

最后

以上就是任性鸵鸟最近收集整理的关于基于FPGA的2FSK调制解调器第一部分:实训目的第二部分:实训准备(包含实训设备及器材)第三部分:实训要求第四部分:实训内容第五部分:源代码第六部分:实训结果的全部内容,更多相关基于FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复