实验用仪器设备及材料

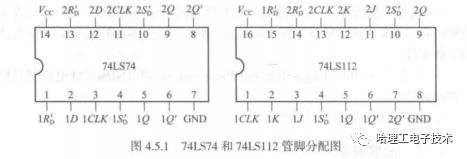

数字实验箱,数字万用表,双D触发器741LS74,双JK触发器74LS112,TTL四-2输

入与非门741S00。74LS74和741S112的管脚分配图如图4.5.1所示。

设计要求

1.设计任务

设计产生时钟脉冲信号的实验方案。

设计测试JK触发器功能的实验方案。

设计测试D触发器功能的实验方案。

设计用与非门将JK触发器转换成D触发器的电路

设计用与非门将D触发器转换成JK触发器的电路。

2.设计提示

触发器具有两个稳定状态,用以表示逻辑状态1和0。在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存储器件,是构成各种时序电路的最基本逻辑单元。

在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。本实验采用741LS112双JK触发器,是下降沿触发的边沿触发器。

JK触发器的特性方程为:Q*=JQ'+K'Q

J和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成与的关系。Q与Q为两个互补输出端。通常把Q=0、=1的状态定为触发器0状态;而把Q=1,Q=0定为1状态。JK触发器常被用作缓冲存储器、移位寄存器和计数器。JK触发器的逻辑符号如图4.5.2所示

在输入信号为单端的情况下,D触发器用起来最为方便,双D触发器741S74为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前D端的状态。D触发器的应用很广,可用作数字信号的寄存、移位寄存、分频和波形发生等。D触发器逻辑符号如图4.5,3所示。

D触发器的特性方程为:Q*=D

实验内容、方法及步骤

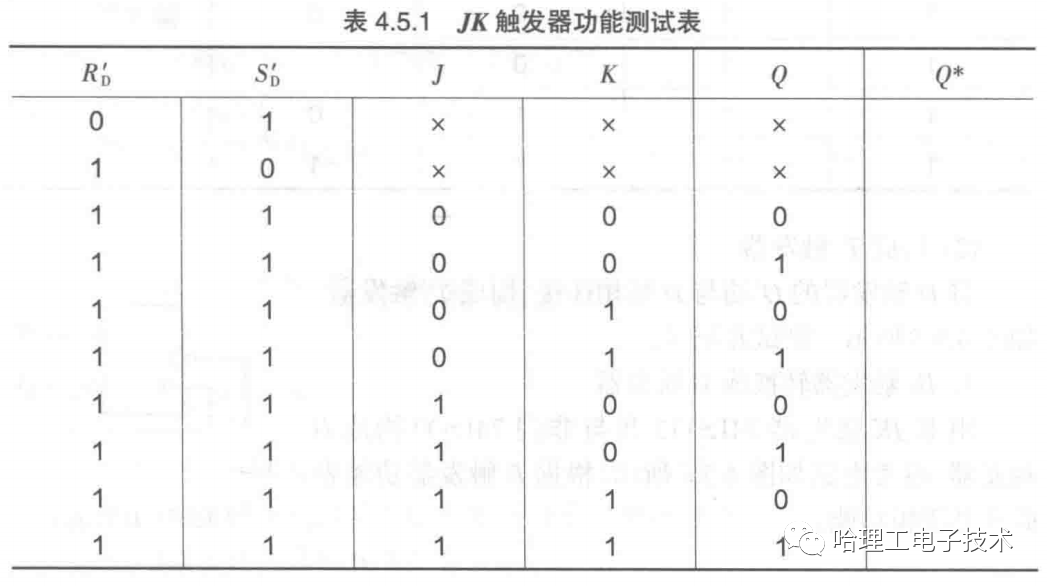

1.测试双JK触发器74LS112的逻辑功能

(1)测试RD'、SD'的复位、置位功能

任取一只JK触发器,RD'、SD'、J、K端接逻辑开关输出插口,CLK端接单次脉

冲源,Q、Q'端接至逻辑电平显示输入插口。要求改变RD'、SD'(J、K、CLK处于任

意状态),并在RD'=0(SD'=1)或SD'=0(RD'=1)作用期间任意改变J、K及CLK的状态,

观察Q、Q'状态。测试结果记入表4.5.1中。

2)测试JK触发器的逻辑功能

按触发器功能表改变JKCK端状态,观察Q、Q状态变化,观察触发器状态更新是否发生在CLK脉冲的下降沿,将测试结果记入表4.5.1中。

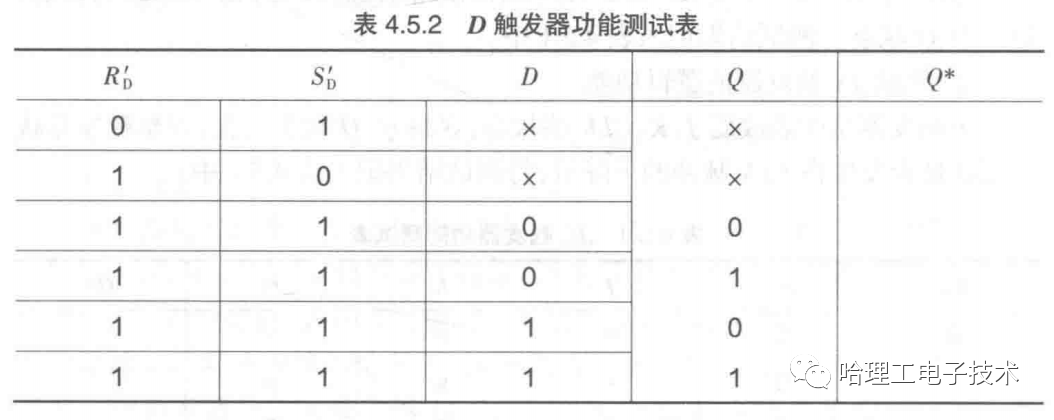

2.测试双D触发器74LS74的逻辑功能

(1)测试D触发器的逻辑功能

任取一只D触发器,D端接逻辑开关输出插口,CLK端接单次脉冲源,Q、Q'端接至逻辑电平显示输入插口。观察触发器状态更新是否发生在CLK脉冲的

上升沿(即由0→1),测试结果记入表4.5,2中。

3.D触发器转换成JK触发器

用双D触发器74LS74和与非门74LS00构成JK触发器,参考电路如图4.5.7所示,根据JK触发器功能表验证其逻辑功能。4.用741LS112实现4进制加法(减法)计数器用双JK触发器74LS112构成4进制加法计数器,参考电路如图4.5.8所示,CLK端接连续脉冲时钟源,Q1、Q0端接至逻辑电平显示输入插口。观察Q1、Q0。状态更新规律画出状态转换图。电子技术基础试验与实训教程图书下载地址

最后

以上就是悦耳麦片最近收集整理的关于74ls00与非门触发器功能表_【数电试验】集成触发器的全部内容,更多相关74ls00与非门触发器功能表_【数电试验】集成触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复