目录:

- 0. 前言

- 0.0 vcs+verdi联合仿真教父级别教程

- 1. 异步复位的串联T触发器

- 1.1 题目描述

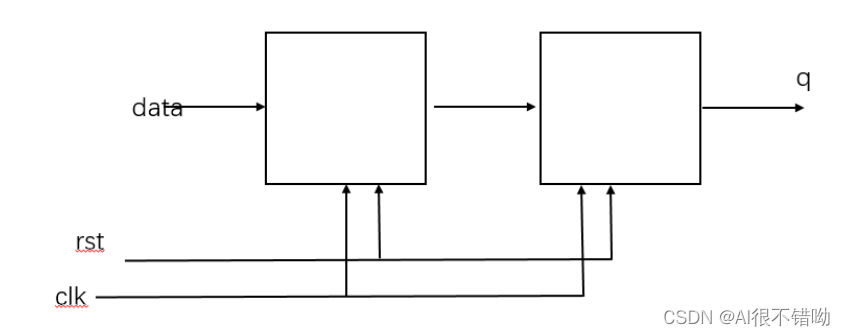

- 1.1.1 信号示意图

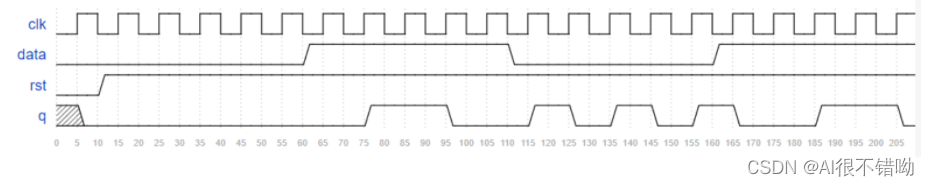

- 1.1.2 波形示意图

- 1.1.3 输入描述

- 1.1.4 输出描述

- 1.2 解题思路

- 1.3 代码实现

- 1.4 测试文件

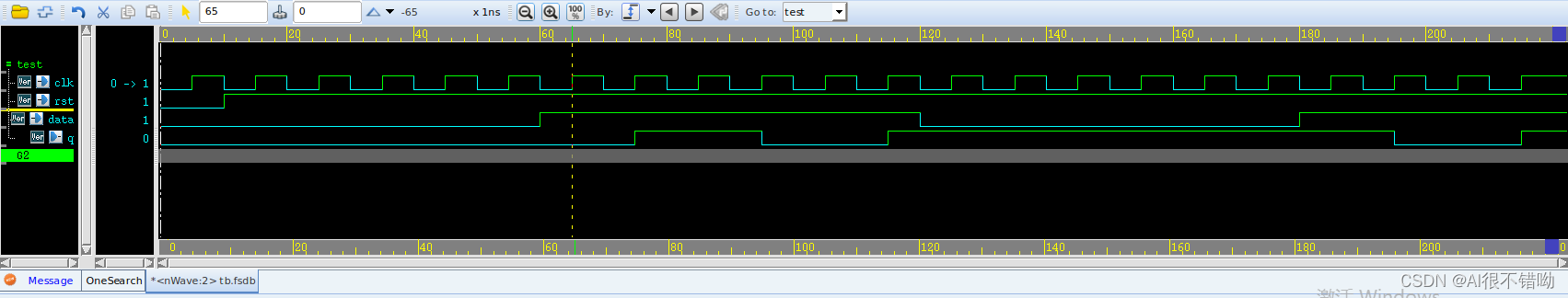

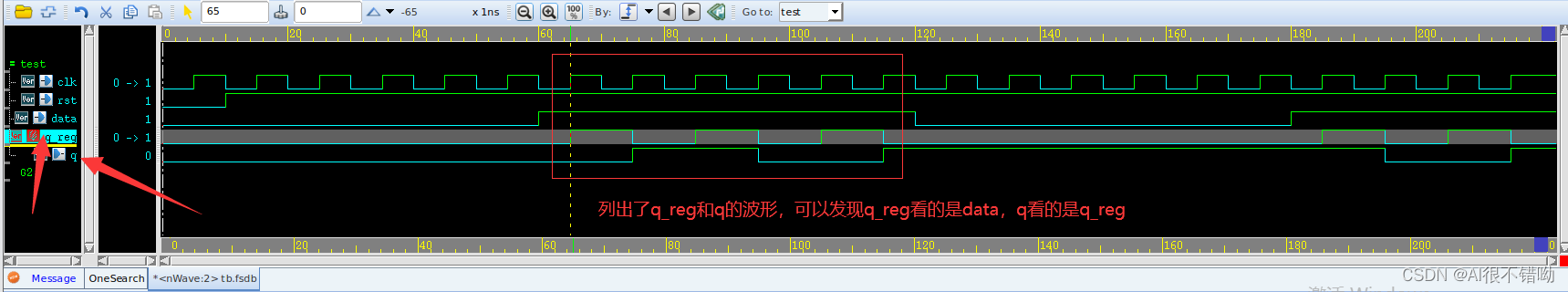

- 1.5 仿真波形

- 2. 奇偶校验

- 2.1 题目描述

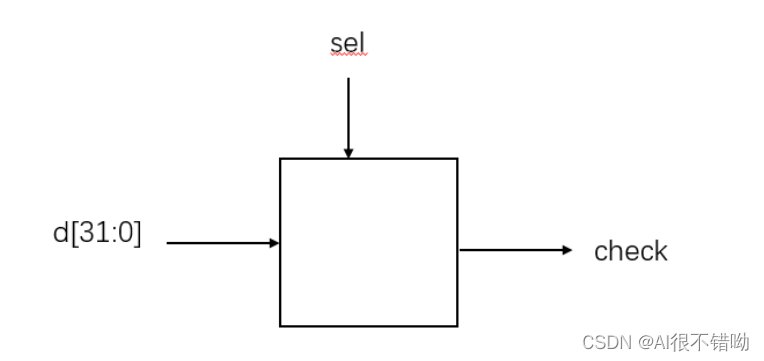

- 2.1.1 信号示意图

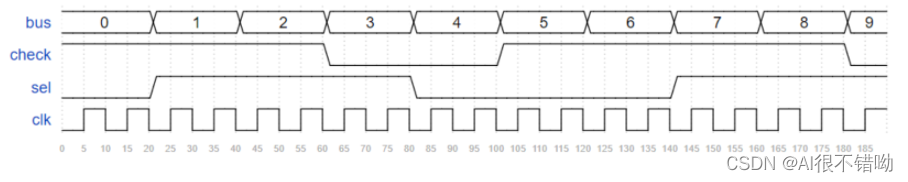

- 2.1.2 波形示意图

- 2.1.3 输入描述

- 2.1.4 输出描述

- 2.2 解题思路

- 2.3 代码实现

- 2.4 测试文件

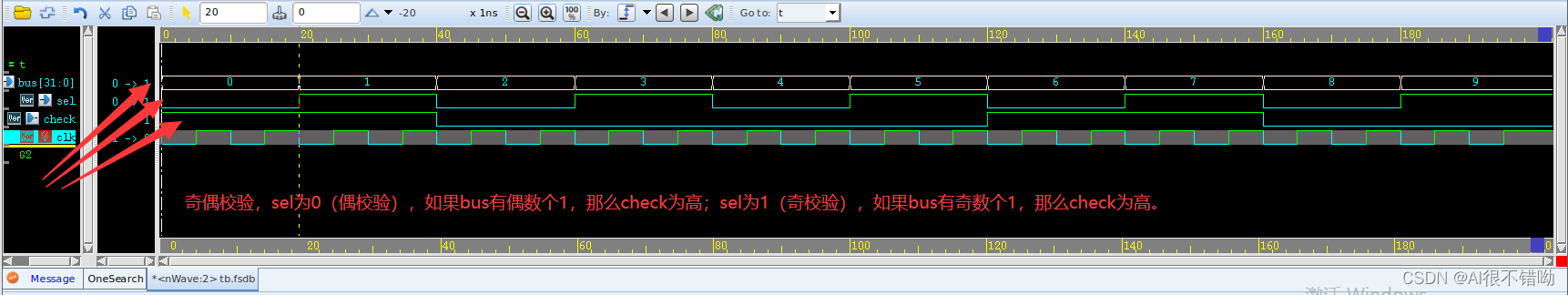

- 2.5 仿真波形

- 参考文献

0. 前言

今天只刷了一个题,为啥呢?是因为难吗?好像不是哦!!!因为我看牛客网上的题好像是漏洞百出,所以萌生出一个大胆的想法,那就是自己写设计和测试文件,使用vcs+verdi联合仿真(随大流,哈哈哈)。咱不说别的,就光装环境花了一天,呜呜呜。不过现在基本上环境是没有问题了,关于环境,我是参考大佬做的,见参考文献。

0.0 vcs+verdi联合仿真教父级别教程

点击就送!!!

1. 异步复位的串联T触发器

点击查看原题

1.1 题目描述

用verilog实现两个串联的异步复位的T触发器的逻辑

1.1.1 信号示意图

1.1.2 波形示意图

1.1.3 输入描述

输入信号 data, clk, rst

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位

1.1.4 输出描述

输出信号 q

类型 reg

1.2 解题思路

需要注意的是,关于各个信号是什么电平有效呢?这个需要我们根据题目要求搞清楚,这里需要吐槽的是,明明是低电平复位,官方竟然没有定义成rst_n(_n默认就是低电平有效的,个人习惯)。

知识点1:T触发器===>输入为1,输出翻转;输入为0,输出保持。

知识点2:异步复位表示不需要等待时钟就可以完成复位。同时,还有同步复位,一般情况下,最好是使用同步复位,单有时候避免不了异步复位,因为省资源,很省,哈哈,因此,出现了异步复位,同步释放的操作,广泛应用。

1.3 代码实现

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

//*************code***********//

reg q_reg;

always @ (posedge clk or negedge rst) begin

if(!rst) begin

q_reg <= 1'b0;

end

else begin

if(data) begin

q_reg <= ~q_reg;

end

else begin

q_reg <= q_reg;

end

end

end

always @ (posedge clk or negedge rst) begin

if(!rst) begin

q <= 1'b0;

end

else begin

if(q_reg) begin

q <= ~q;

end

else begin

q <= q;

end

end

end

//*************code***********//

endmodule

1.4 测试文件

2022.6.28

关于测试文件,我暂时还没做,等我先熟悉一下vcs和verdi联合使用,哈哈!敬请期待。

2022.6.29 21:17

我来更新我之前的承诺了,哈哈哈,没想到硬肝了一天,硬是啃下了这块硬骨头。

关于我如何学习的可以参照我之后写的一篇文章,敬请期待

2022.6.30

爆肝几小时,出了一篇vcs+verdi联合仿真教父级别教程,哈哈,话不多说,直接给你传送门

1 module Tff_2_tb();

2 reg clk=0;

3 always #5 clk = ~clk; // Create clock with period=10

4

5 reg data=0,rst=0;

6

7 initial begin

8 #10 rst = 1;

9 #210 $finish;

10 end

11

12 always

13 begin

14 #60 data = ~data;

15 end

16

17 initial begin

18 $fsdbDumpfile("tb.fsdb");

19 $fsdbDumpvars;

20 end

21

22 Tff_2 test(.data(data),

23 .clk(clk),

24 .rst(rst),

25 .q(q));

26 endmodule

1.5 仿真波形

敬请期待!!!

没有q_reg信号

添加了q_reg信号,看的更清晰

2. 奇偶校验

2.1 题目描述

现在需要对输入的32位数据进行奇偶校验,根据sel输出校验结果(1输出奇校验,0输出偶校验)

2.1.1 信号示意图

2.1.2 波形示意图

2.1.3 输入描述

输入信号 bus sel

类型 wire

2.1.4 输出描述

输出信号 check

类型 wire

2.2 解题思路

1、简单理解奇偶校验

奇校验:原始码流+校验位 总共有奇数个1

偶校验:原始码流+校验位 总共有偶数个1

2、计算奇偶校验的方法 按位求异或得到奇校验结果,对其求反得到偶校验结果

3、关于涉及到的基础知识,可以移步到我的另一个专栏,传送门。

2.3 代码实现

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

wire temp_reg;

assign temp_reg = ^bus;

assign check = sel ? temp_reg : ~temp_reg;

//*************code***********//

endmodule

2.4 测试文件

1 module odd_sel_tb();

2 reg clk=0;

3

4 always #5 clk = ~clk; // Create clock with period=10

5

6 reg [31:0] bus = 0;

7 reg sel = 0;

8 wire check;

9

10 odd_sel t(.bus(bus),

11 .sel(sel),

12 .check(check));

13

14 always begin

15 #20 sel = ~sel;

16 end

17

18 always begin

19 #20 bus++;

20 end

21

22 initial begin

23 $fsdbDumpfile("tb.fsdb");

24 $fsdbDumpvars;

25 #200 $finish;

26 end

27 endmodule

2.5 仿真波形

好了,这就是这两个题目的全部了,如有感兴趣的,可以评论区或者私聊我获取相应的文件。

希望大家看完之后可以给个三连,让更多的人都能看到,感谢!!!

加油,奥里给!!!

===========================================================================

参考文献

关于虚拟机的搭建

tb参考

最后

以上就是无语早晨最近收集整理的关于【牛客网刷题系列 之 Verilog快速入门】~ 异步复位的串联T触发器、奇偶校验0. 前言1. 异步复位的串联T触发器2. 奇偶校验的全部内容,更多相关【牛客网刷题系列内容请搜索靠谱客的其他文章。

发表评论 取消回复