我是靠谱客的博主 清秀故事,这篇文章主要介绍verilog 异步复位的串联T触发器 四选一多路器 奇偶校验 移位运算与乘法异步复位的串联T触发器:四选一多路器奇偶校验:移位运算与乘法:,现在分享给大家,希望可以做个参考。

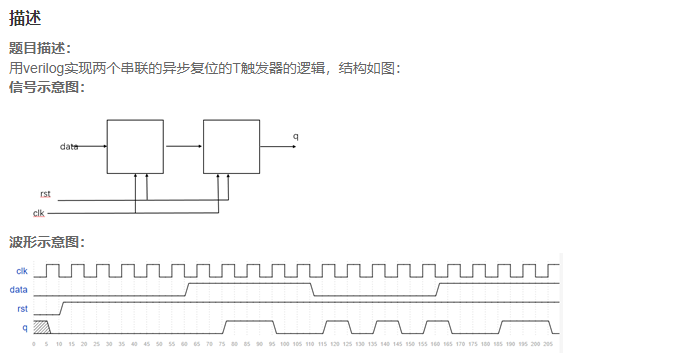

异步复位的串联T触发器:

由真值表可知,T=1时, Qn+1 = ~ Qn ,T=0时, Qn+1 = Qn

即:输入为1下时,输出0到1到0不断翻转,输入为0锁存上一个时序结果。

所以串联T触发器:

// 第1个触发器输出为q1,第2个触发器输出为q

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

reg q1;

always@(posedge clk or negedge rst)begin

if(~rst)begin

q1<=0; q<=0;

end

else begin

if(data) q1<=!q1;

else q1<=q1;

if(q1) q<=!q;

else q<=q;

end

end

endmodule

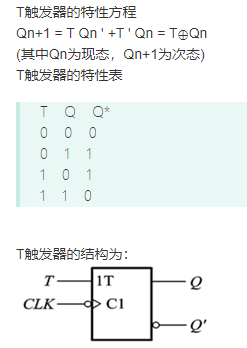

四选一多路器

注意,线网类型不能写always,wire用assign

`timescale 1ns/1ns

module mux4_1(

input[1:0] d1,

input[1:0] d2,

input[1:0] d3,

input[1:0] d0,

input[1:0] sel,

output[1:0] mux_out

);

assign mux_out = sel[0]? (sel[1]? d0:d2):(sel[1]? d1:d3);

endmodule

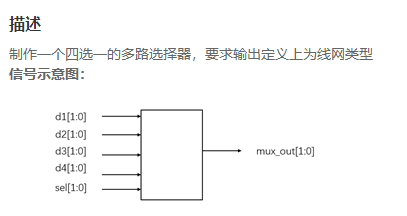

奇偶校验:

奇偶校验,检验传输数据中1的个数,

通过检验位将传输1的个数变成奇数就是奇校验,变成偶数就是偶校验

8'b01100100 //原数据

9'b01100100_0 //奇校验 (将传输1的个数变成奇数就是奇校验)

9'b01100100_1 //偶校验 (将传输1的个数变成偶数就是偶校验)

// 偶校验:异或

// 奇校验:同或(异或取反)

// 连续运算

& a[3:0] // AND: a[3]&a[2]&a[1]&a[0].相当于 (a[3:0] == 4'hf)

| b[3:0] // OR: b[3]|b[2]|b[1]|b[0].相当于 (b[3:0] != 4'h0)

^ c[2:0] // XOR: c[2]^c[1]^c[0]

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

assign check = sel? ^bus : ~^bus;

endmodule

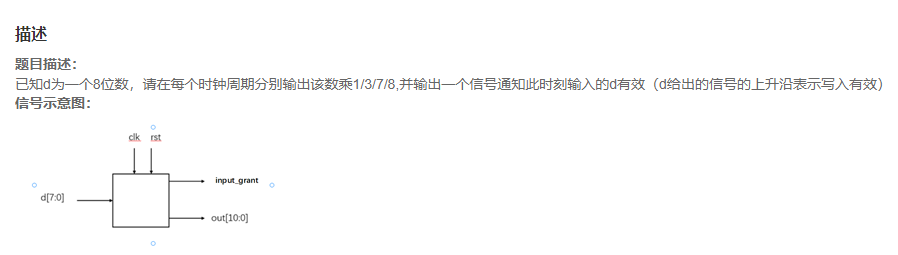

移位运算与乘法:

硬件中进行乘除法运算是比较消耗资源的一种方法,可以将乘除运算转换为位运算

如果 b * a,且 a = 2n, 则 b* a 可以转换为 (b << n)

如果 b * a,且 a = 2n -1, 则 b* a 可以转换为 (b << n) - b

| 乘运算 | 位运算 |

|---|---|

| ×1 | din |

| ×3 | (din<<2) - din // 左移2位然后减去本身 |

| ×7 | (din<<3) - din |

| ×8 | din<<3 |

// 3段

`timescale 1ns/1ns

module multi_sel(

input [7:0]d ,

input clk,

input rst,

output reg input_grant,

output reg [10:0]out

);

reg [1:0] count4;

reg [7:0] d_reg;

always @ (posedge clk or negedge rst) begin // count周期计数

if (!rst)

count4 <= 2'd0;

else if (count4 == 2'd3)

count4 <= 2'd0;

else

count4 <= count4 + 1;

end

always@(posedge clk or negedge rst)begin

if(~rst) begin

d_reg <=0;

input_grant <=0;

end

else if(count4 == 0)begin // 写入有效,写入到数据寄存器

d_reg <= d;

input_grant <= 1;

end

else begin

d_reg <= d_reg; // 寄存器数据不变(保存的原始输入),此时写入无效

input_grant <= 0;

end

end

always @ (posedge clk or negedge rst) begin

if (!rst)begin

out <= 0;

end

else begin

case(count4)

2'd0: out <= d;

2'd1: out <= (d_reg<<2) - d_reg;

2'd2: out <= (d_reg<<3) - d_reg;

2'd3: out <= (d_reg<<3);

endcase

end

end

endmodule

最后

以上就是清秀故事最近收集整理的关于verilog 异步复位的串联T触发器 四选一多路器 奇偶校验 移位运算与乘法异步复位的串联T触发器:四选一多路器奇偶校验:移位运算与乘法:的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复