数电技术基础大恶补08:时序逻辑电路

目录

- 1.时序逻辑电路

- 2.时序电路的分类

- 3.时序逻辑电路的分析方法

- 4.常用时序逻辑电路

- 4.1 移位寄存器

- 4.2 计数器

- 4.3 顺序脉冲发生器

- 4.4 序列信号发生器

- 5.时序电路设计方法

- 6.时序电路动态特性

1.时序逻辑电路

特点:

①任一时刻的输出不仅取决于该时刻的输入,还与电路原来的状态有关。

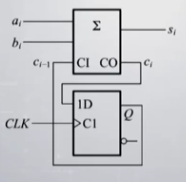

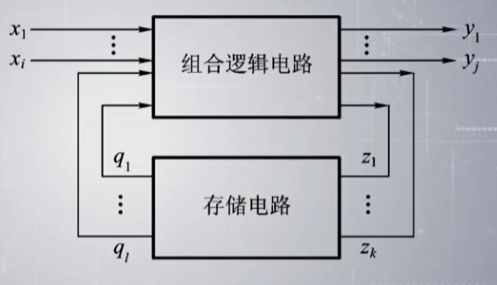

②在电路结构上,包含存储电路和组合电路,存储器状态和输入变量共同决定输出,如下图所示。

它的结构框图如下:

它的描述方法通过三个方程组来实现,分别是输出方程、驱动方程、状态方程。

输出方程:输出与输入间的对应关系,即y = f(x,q)

驱动方程:存储电路中的关系,即z = f(x,q)

状态方程:状态的相应关系,即Q* = f(z,q)

2.时序电路的分类

同步时序电路:所有触发器的时钟信号统一,同时发生

异步时序电路:所有触发器的时钟信号并不是同时发生的

米利(Mealy)型时序电路:输出信号不仅取决于存储电路的状态,还取决于输入,即Y = F(X,Q)

穆尔(Moore)型时序电路:输出信号仅仅取决于存储电路的状态,即 Y = F(Q)

3.时序逻辑电路的分析方法

同步时序逻辑电路的分析方法:

分析:找出给定时序电路的逻辑功能,即找出在输入和CLK作用下,电路的次态和输出。

步骤:

①从给定电路写出存储电路中每个触发器的驱动方程(输入的逻辑式) ,得到整个电路的驱动方程。

②将驱动方程代入触发器的特性方程,得到状态方程。

③从给定电路写出输出方程。

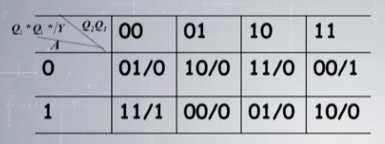

④列出状态转移表(01表)

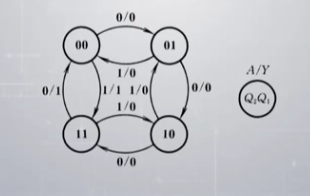

⑤状态转换图:如流程图、状态图、波形图

异步时序逻辑电路的分析方法:找出与时钟有关的信号,按同步进行分析,而与时钟无关的信号还要单独分析,因此异步的电路会更加复杂。

4.常用时序逻辑电路

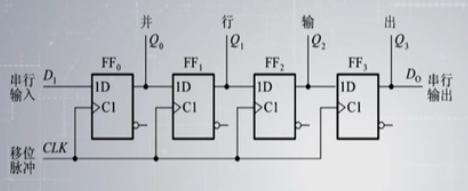

4.1 移位寄存器

移位寄存器的作用:串并转换、左右移位、保持、异步清零。

因为从CLK上升沿到达开始到输出端新状态的建立需要经过一段传输延迟时间,所以当

CLK的上升沿同时作用于所有的触发器时,它们输入端(D端)的状态还没有改变。于是FF1按Q0原来的状态翻转,FF2按Q1原来的状态翻转,FF3按Q2原来的状态翻转。同时,加到寄存器输人端Di的代码存人FF0。总的效果相当于移位寄存器里原有的代码依次右移了1位。

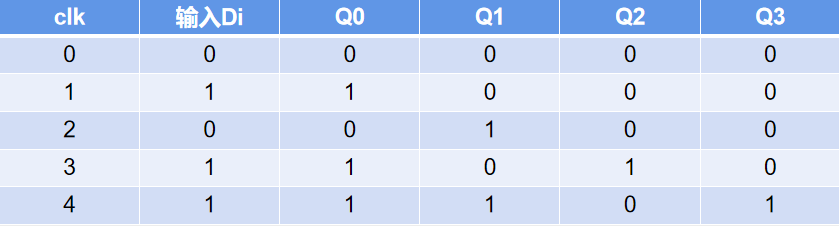

例如,在4个时钟周期内输人代码依次为1011,而移位寄存器的初始状态为Q0Q1Q2Q3 = 0000,那么在移位脉冲(也就是触发器的时钟脉冲)的作用下,移位寄存器里代码的移动情况将如下图所示。

4.2 计数器

功能:计脉冲数、分频、定时、产生节拍脉冲等

分类:同步计数器(CLK同时触发)、异步计数器(CLK不同步触发)

优缺点:和同步计数器相比,异步计数器结构简单,但是也存在两个明显的缺点。第一,工作频率比较低,因为异步计数器是串行的连接方式;第二,在电路状态译码时存在竞争–冒险现象。

4.3 顺序脉冲发生器

有一定顺序的脉冲信号,用来控制芯片,也就是芯片的一些固定的时序,产生这个顺序脉冲的电路就是顺序脉冲发生器。

4.4 序列信号发生器

测试经常用到一组特定的串行数字信号,产生这组信号的电路就是序列信号发生器。

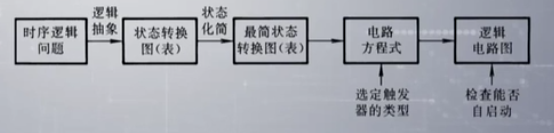

5.时序电路设计方法

① 逻辑抽象:也就是得到状态的转换的关系,画出状态转换图

②状态简化:将等价的状态合并,得出最简的状态转换图

③状态分配(编码):确定触发器数目,给每个状态规定一个代码

④选定触发器类型:求出状态方程,驱动方程,输出方程这三大方程

⑤逻辑图(电路)

⑥检查自启动:如果不能自启动,还要采取措施解决

具体例子:数字密码锁的设计

6.时序电路动态特性

由于时序电路通常包含组合电路和存储电路两部分,所以时序电路中的竞争一冒险现象也有两个方面:

一方面组合电路因竞争–冒险而产生的尖峰脉冲,虽然对组合逻辑电路本身的稳态输出没有影响,但是组合逻辑竞争产生的尖峰脉冲如果被存储电路接收,引起触发器翻转,则电路将发生误动作。

另一方面存储电路本身也存在竞争一冒险问题。存储电路中竞争–冒险现象的实质是由于触发器的输入信号和时钟信号同时改变而通过不同的路径到达同一触发器便产生了竞争,从而导致触发器误动作。因为这种现象一般只发生在异步时序电路中,所以在设计较大的时序系统时多数都采用同步时序电路。

最后

以上就是飘逸火车最近收集整理的关于数电技术基础大恶补08:时序逻辑电路1.时序逻辑电路2.时序电路的分类3.时序逻辑电路的分析方法4.常用时序逻辑电路5.时序电路设计方法6.时序电路动态特性的全部内容,更多相关数电技术基础大恶补08:时序逻辑电路1.时序逻辑电路2.时序电路内容请搜索靠谱客的其他文章。

发表评论 取消回复