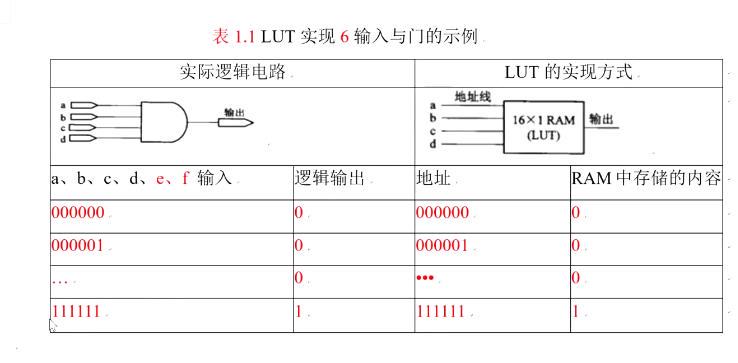

查找表LUT

本质上是RAM,一个6输入的LUT中包括6为地址线的64*1的RAM,6输入的LUT有64中输出结果,将64中结果存储下来,可以根据不同的地址输入查找处相应输出结果。

LUT实现6输入与门的事例如下:

地址线有64种组合,进行寻址,并存储数据。

Verilog HDL的抽象级别

指同一个物理电路可以在不同层次上用硬件描述语言描述。

①系统级:实现设计模块外部特性(行为级)

②算法级:实现算法运行模型(行为级)

③RTL级:描述数据在寄存器之间的流动、处理、控制(数据流描述方式)

④门级:逻辑门之间的连接(结构化描述)

⑤开关级:描述器件中三极管和存储节点之间的模型(结构化描述)

综合使用时是混合级

1、结构化描述方式

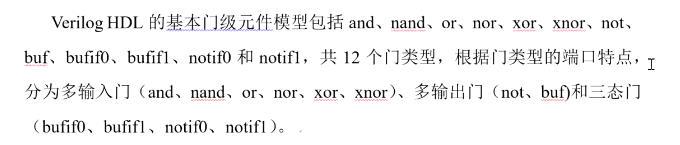

又承元件例化,直接调用verilog的基本门级元件的方法叫门级结构描述;调用定义的module的方法叫模块结构描述。

分别有and-与、nand-与非、nor-或非、xor-异或、xnor-同或、not-非、buf-缓冲器、bufif0-低电平使能的三态缓冲器、bufif1-高电平使能的三态缓冲器、notif0-低电平使能的三态门反相器。

可以直接调用。

用结构化描述三人多数表决器(利用了卡诺图化简)

module dsbjq_structure(

input a,

input b,

input c,

output f

);

//上述也可以写为

module dsbjq_structure(a,b,c,d);

input a;

input b;

input c;

output f;

wire ab,bc,ac;//内部信号

and U1(ab,a,b);//调用与门,a,b为输入信号,ab为输出信号,U1为例化名可认为是元件名

and U2(bc,b,c);

and U3(ac,a,c)

or U4(f,ab,bc,ac);//fab+bc+ac

endmodule2、数据流方式

//前面定义不变

assign f=a&b|a&c|b&c;

3、行为级描述方式(抽象级别最高,概括性最强)

module dsbjq_structure(

input a,

input b,

input c,

output reg f//定义为reg类型的

);

always@(a,b,c)//也可以写成always@(*)表示任意输入改变便改变

begin

case ({a,b,c})//位拼接abc变成3位二进制信号

3'b000:f=1'b0;

3'b001:f=1'b0;

3'b010:f=1'b0;

3'b011:f=1'b1; //两个人满足则输出f为1,像列真值表一样,无需去计算

……

3'b111:f=1'b1;

default:f=1'bx;//输出不确定

endcase

end

endmodule//上述就是行为描述4、混合描述

主要是行为描述,再穿插数据流和结构化描述

module dsbjq_structure(

input a,

input b,

input c,

output f

);

reg m1,m2,m3;

assign f=m1|m2|m3;//数据流描述

always@(a or b or c)//行为描述

begin

m1 = a&b;

m2 = b&c;

m3 = a&c;

end

endmodule最后

以上就是超帅抽屉最近收集整理的关于Verilog多种方式实现三人表决器的全部内容,更多相关Verilog多种方式实现三人表决器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复