在设计中 一般避免锁存器,锁存器不仅消耗资源,且更容易受到干扰,使得经常出现电路的仿真结果和在线调试结果不一致的情况。

https://cloud.tencent.com/developer/article/1530837

本文主要从编码和综合后的原理图出发,展现不同的编码风格和生成的原理图的区别:

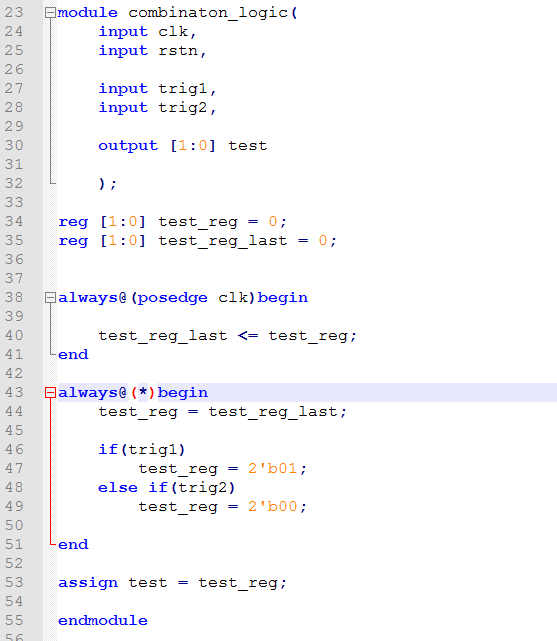

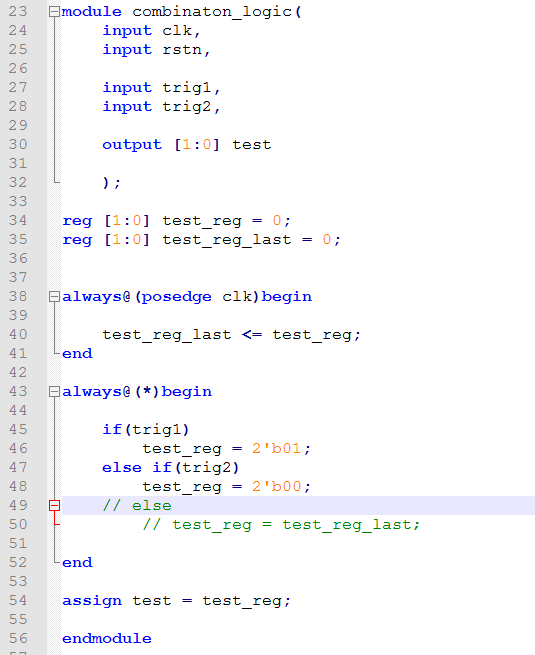

编码一:

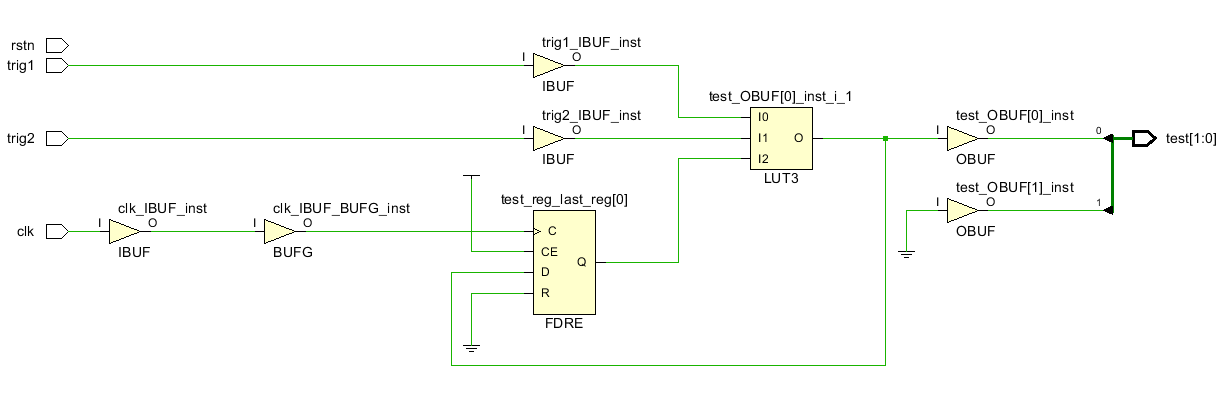

综合后的原理图如下,LUT3为3输入查找表,FDRE为触发器。此编码无触发器生成。

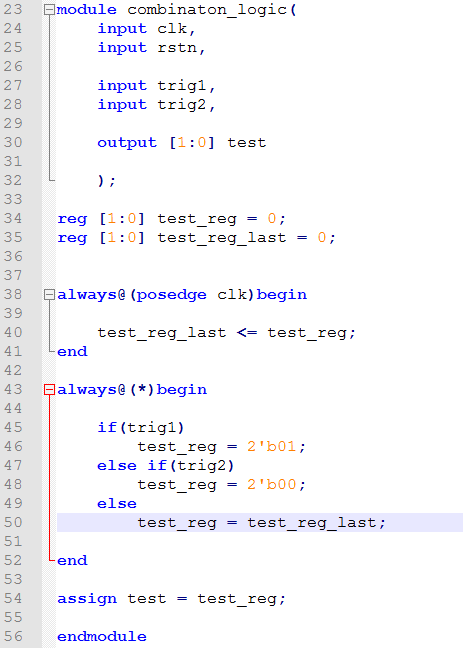

编码二:

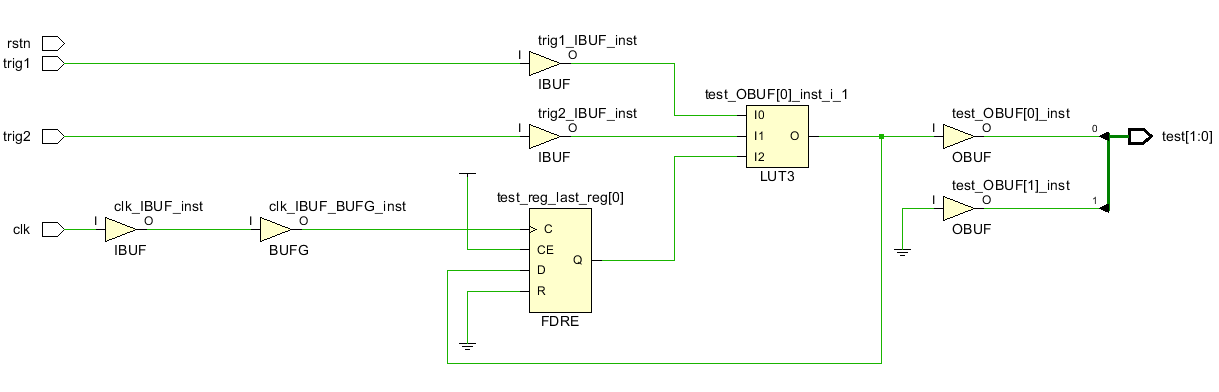

综合后的原理图:(同编码一)

编码三:

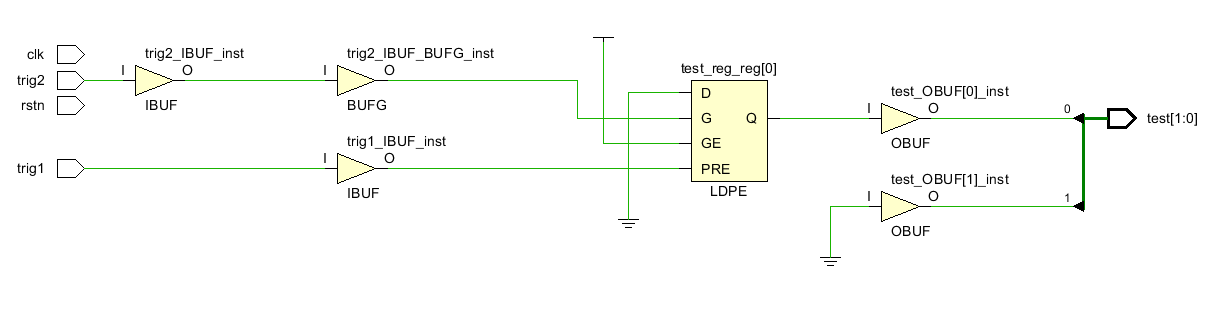

综合后的原理图,LDPE为锁存器。

编码一的代码风格相对于编码二更加友好,因为将默认条件下的代码写在最前面,防止忘记,这样可以有效防止锁存器的生成。

最后

以上就是仁爱蜻蜓最近收集整理的关于FPGA设计组合逻辑电路中的锁存器问题的全部内容,更多相关FPGA设计组合逻辑电路中内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复