1.竞争:

各信号到达目标位置的时延不同,到达终点的时间有先有后造成竞争。两个输入信 号同时向相反方向的逻辑电平跳变的现象。有竞争不一定有冒险。 冒险:由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险 解决办法:

⚫ 加滤波电容,消除毛刺影响。

⚫ 增加冗余项,消除逻辑冒险。

⚫ 改变设计,减少毛刺发生。

1)使用格雷码;

2)使用同步电路。

例如数字电路中常用格雷码计数器取代 2 进制计数器,因为 Gray Code 输出每次只有 一位跳变,消除了竞争冒险发生的条件。同步电路信号变化发生在时钟沿,只要毛刺 不在时钟沿被采样就会消除毛刺。

2.相同面积的 CMOS 与非门和或非门哪个更快 ?

与非门会更优

电子迁移率是空穴的 2 倍,为了上升延迟和下降延迟相同,PMOS 需要做成 NMOS 两倍 多大小。PMOS 的充电时间要大于 NMOS 的充电时间长。与非门的 PMOS 是并联的,相对于 串联 PMOS 管的或非门更快。

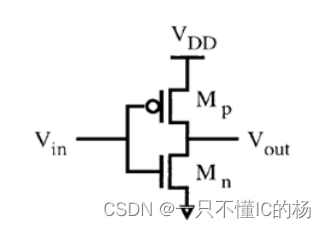

3.反相器知识

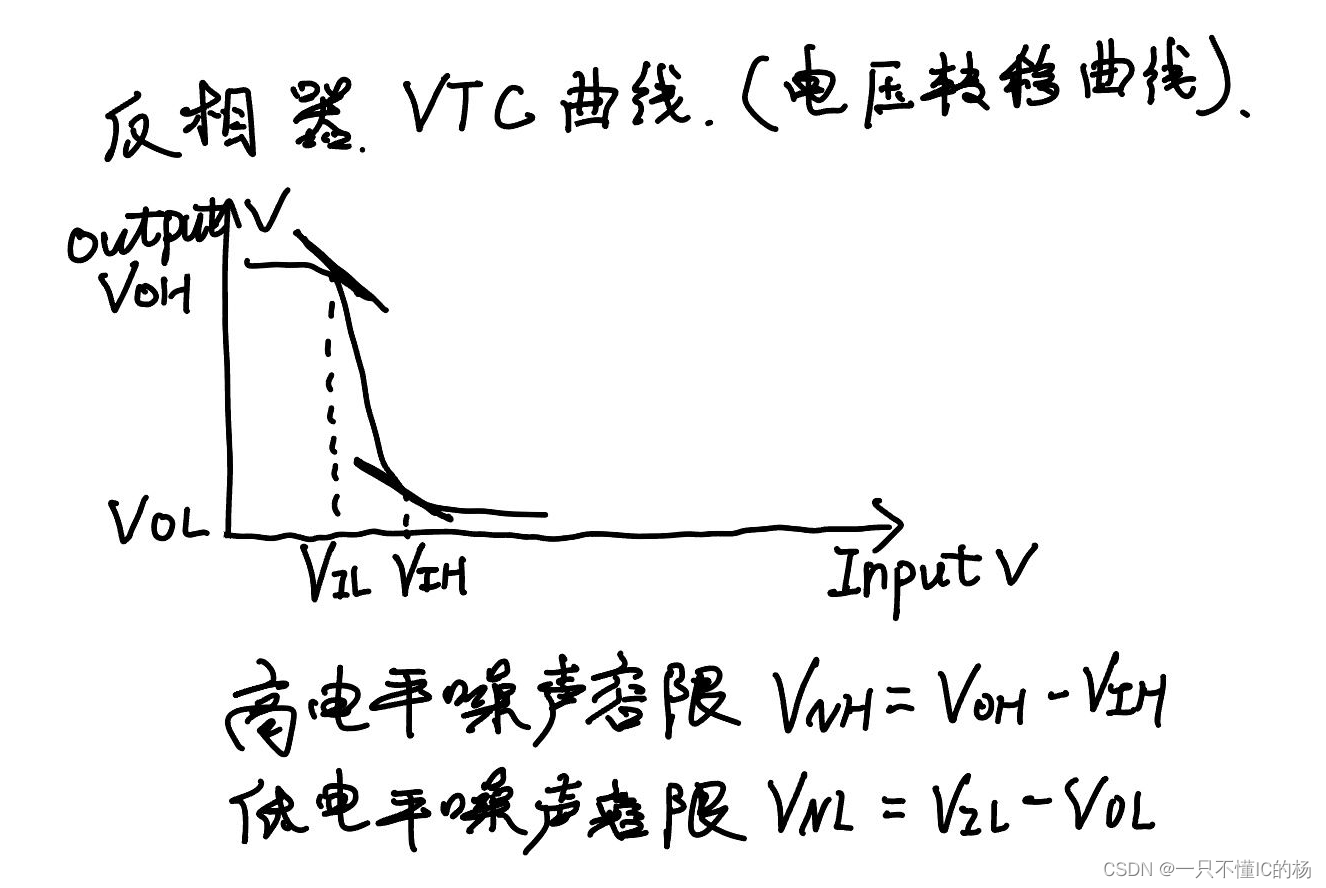

噪声容限定义:

前一极输出为最坏的情况下,为保证后一极正常工作,所允许的最大噪声 幅度 VIH:输入电压由高到低变化时,输出电压开始上升且传输特性曲线斜率为-1 的点。(仍能 维持输出为逻辑 “0” 的最小输入电压) VIL:输入电压由低到高变化时,输出电压开始下降且传输特性曲线斜率为-1 的点。(仍能 维持输出为逻辑 “1” 的最大输入电压)

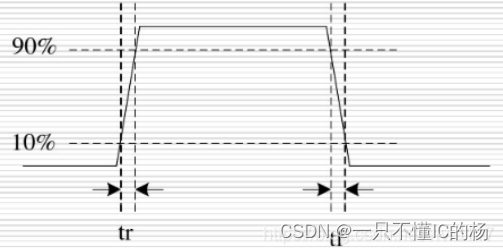

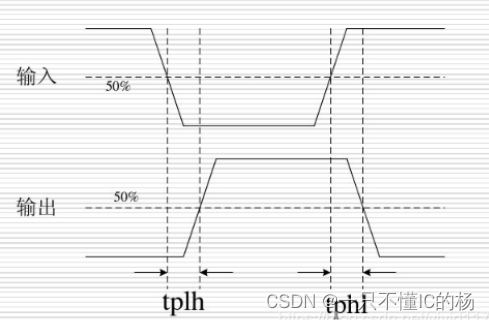

转换时间、传播延时

Transition Time(转换时间/过渡时间): 上升时间 tr:从 10%Vdd 上升到 90%Vdd 的时间, 下降时间 tf:从 90%Vdd 下降到 10%Vdd 的时间。

Propagation Delay(传播延时): 在输入信号变化到 50%Vdd 到输出信号变化到 50%Vdd 之间的时间。

4.同步电路、异步电路

同步电路和异步电路的区别在于电路触发是否与驱动时钟同步,从行为上讲,就是所有电路是否在同一时钟沿下同步地处理数据。不同时钟源的电路就是异步电路。

同步复位和异步复位电路是同步电路和异步电路中两个典型的逻辑单元。

在同步复位电路中,当复位信号有效时,必须要等到时钟沿有效时,才能处理复位信号相关逻辑行为(同一时 钟沿下同步处理数据);

而在异步复位电路中,当复位信号有效时,立即处理复位信号相关逻 辑行为。

数字逻辑设计的首要原则就是坚持做同步设计。

在数字逻辑中坚持同步设计是因为同步设 计对延迟和 layout 不敏感,只要时序收敛,一般就可以保证电路稳定工作。

如果时序收敛,则 所有组合逻辑可能产生的毛刺都会在下个时钟边沿到达之前 settle 掉。

时序收敛即输入数据与 时钟需要满足建立时间(setup time)和保持时间(hold time)。

对异步复位寄存器来说,异步复位信号需要满足恢复时间(recovery time)和去除时间 (removal time)才能有效进行复位操作和复位释放操作,防止输出亚稳态。

异步电路存在竞争冒险、延迟相关等一系列问题,这导致异步电路对半导体工艺参数变动和温度变化十分敏感。 布线方式改变也会对异步电路造成影响。

SOC 最好采用全局异步局部同步(GALS)的设计方法。

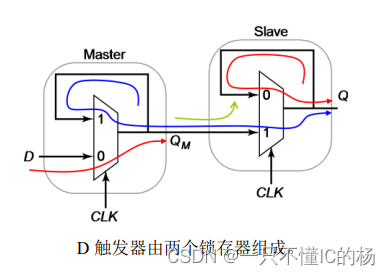

5.D 触发器与 Latch

➢ 锁存器对电平信号敏感,在输入脉冲的电平作用下改变状态。

➢ D 触发器对时钟边沿敏感,检测到上升沿或下降沿触发瞬间改变状态。

优点:锁存器集成度更高,占用面积小。

缺点:锁存器对毛刺敏感,ASIC 设计中 CPU 高速电路和 RAM 对面积要求高的电路才会用锁存器。一般不提倡使用锁存器。

锁存器的危害

组合逻辑语句不全导致电路产生锁存器。

(1) 对毛刺敏感。不能异步复位,上电后处于不确定的状态。

(2) Latch 会使静态时序分析变得复杂,不利于设计的可重用。

(3) FPGA 没有与锁存器直接对应的逻辑资源。FPGA 实现锁存器,会采用查找表 LUT, 消耗更多的资源。

避免锁存器的 RTL 设计:If-else 要写全,case 语句中包含 default

最后

以上就是跳跃硬币最近收集整理的关于数字电路笔记的全部内容,更多相关数字电路笔记内容请搜索靠谱客的其他文章。

发表评论 取消回复