带锁存器的时序逻辑综合

- 锁存器的无意综合

- 锁存器的有意综合

????声明:

????未经作者允许,禁止转载

????推荐一个IC、FPGA新手入门的好网站:????快 点 击 进 入 学 习 吧????

锁存器生成的方式有两种:有意的和无意的。无意综合出的锁存器只会浪费面积,所以知道什么时候该综合出锁存器就很有必要。

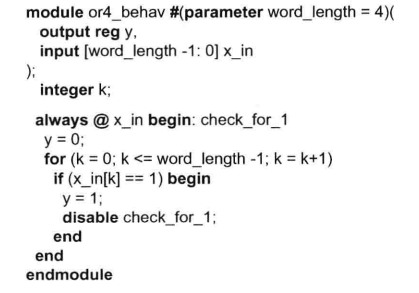

- 一个无反馈的组合原语网表可综合成无锁存的组合逻辑

- 描述组合逻辑的一组连续赋值中一定不能有反馈存在,因为将不可综合。

- 一个带反馈的条件操作符的连续赋值语句,(如左右表达式都有同一个变量)会综合出锁存器。这是一种有意的方法,如SRAM,这是可综合的。

锁存器的无意综合

这样一个例程的综合后,是没有计数器的,y也不是一个存储器,因为这是一个组合逻辑,y可以直接输出。

现在再分析一个例子

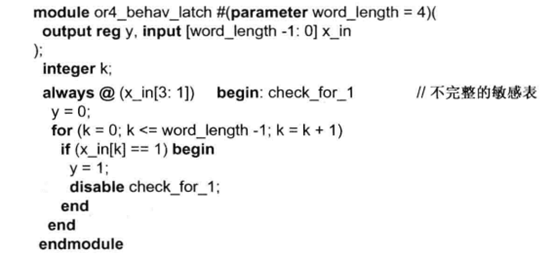

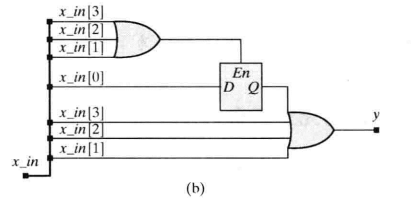

- 如果触发的敏感信号不完全,那么就会综合出带锁存器的电路,因为无法对不在触发事件里的信号进行直接操作,只能依靠锁存器锁存后操作。

所以所有用以实现组合逻辑的电平敏感行为电路的输入信号,都必须包含于事件控制表达式中,不然就是无意的生成锁存器。

未完整定义case和if语句也会产生预期外的锁存器。因为没有说明的情况下,输出就会需要寄存器来保持,这也意外的生成了寄存器。

锁存器的有意综合

有意综合出锁存器的时候,通常都是赋值有反馈的时候,或者就是为了暂存数据。

最后

以上就是暴躁过客最近收集整理的关于带锁存器的时序逻辑综合的全部内容,更多相关带锁存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复