锁存器(Latch)

锁存器是一种对脉冲电平敏感的双稳态电路,它具有0和1两种稳定状态,一旦状态被确定,就能自行保持,直到有外部特定输入脉冲电平作用在电路位置时,才有可能改变状态。

锁存器是电平触发的存储单元,数据存储的动作取决于使能信号的电平。锁存器不锁存信号时,输出端的信号随输入端变化,相当于通过一个缓存器一样;锁存器锁存信号时,输入端信号不起作用。

锁存器最大危害在于对毛刺敏感。在FPGA设计中要避免产生锁存器,锁存器的存在不利于实现同步操作,也会让静态时序分析变得复杂。

锁存器的数据存储动作取决于输入使能信号的电平值,仅当锁存器处于使能状态时,输出数据才会随着数据输入发生变化,否则处于锁存状态。

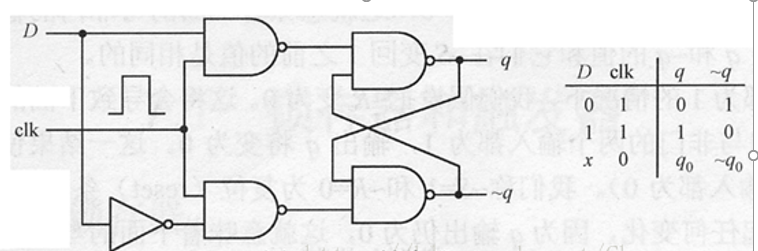

下面主要介绍D锁存器:

D锁存器只有当时钟信号为0时,才能进入存储状态。通过分析我们可以知道,D锁存器是一种电平触发。

module D_latch(clk,D,Q);

input clk,D;

output reg Q;

always @(clk,D) //注:这里的敏感信号为clk和D,因为D也引起Q的变化。当clk为高电平时,D的变化也引起输出Q的变化。

if(clk==1)

Q=D;

endmodule触发器(Flip-Flop,简称FF)

触发器是边沿敏感的存储单元,数据存储的动作由时钟的上升或下降沿触发。在时钟为低或高时,输出端信号保持状态不变。

在大规模CMOS集成电路,特别是可编程逻辑器件(如CPLD,FPGA)和专用集成电路(ASIC)中,D触发器得到普遍应用。

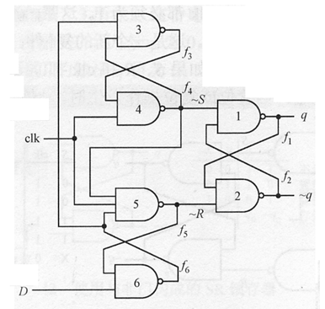

下面介绍D触发器:

这是一个正边缘触发的D触发器。

module D_flipflop(clk,D,Q); //触发器的英文为flipflop.

input clk,D;

output reg Q;

always @(posedge clk) //注:这里的敏感信号为clk,没有D

Q=D;

endmodule

含异步复位端的D触发器

module D_flipflop(D,clk,reset,Q);

input D,clk,reset;

output reg Q;

always @(negedge reset,posedge clk) /*不能忽略关键词negedge,因为敏感列表里不能既包含边沿触发信号又包含电平敏感型信号*/

if(!reset)

Q<=0;

else

Q<=D;

endmodule

含同步复位端的D触发器

module D_flipflop(D,clk,reset,Q);

input D,clk,reset;

output Q;

always @(posedge clk)

if(!reset)

Q<=0;

else

Q<=D;

endmodule寄存器

在实际的系统中,把用来存储一组二进制代码的同步时序逻辑电路称为寄存器,触发器有记忆功能,可以利用触发器构成寄存器,一个触发器只能存储一个二进制码元,把n个触发器的时钟端连接到一起构成一个存储n位二进制码元的寄存器。

寄存器和锁存器都可以存储数据,但他们的区别是寄存器时同步时钟控制,锁存器是电位信号控制。寄存器和锁存器具有不同的应用场合,取决于控制方式以及控制信号和数据信号之间的时间关系:若数据信号有效一定滞后于控制信号有效,则只能使用锁存器;若数据信号提前于控制信号到达并且要求同步操作,则可用寄存器来存放数据。

相关文章:

锁存器、触发器、寄存器和缓冲器的区别 https://www.cnblogs.com/wwping/articles/2261312.html

寄存器和锁存器的区别 https://blog.csdn.net/m0_37666899/article/details/77822611

深刻解析锁存器、触发器区别,以及verilog代码编写中如何避免产生锁存器 https://wenku.baidu.com/view/f0cecb5d6c175f0e7cd1378a.html

| Flip-Flop | Latch |

| 只有当控制信号从高变低或变低或变高(即仅对信号变化敏感)时, 电路状态才会改变。 | 一旦输入信号改变状态就改变(当然存在一些传播延迟)。 |

| 同步 | 异步 |

| 边沿触发意味着当时钟脉冲发生变化时电路的输出发生变化(可能是时钟脉冲的正边沿或负边沿)。 | 电平触发意味着电路的输出取决于使能信号的电平(1或0)。 |

| 由锁存器构建(FF类似于时钟锁存器)。 FF用作寄存器。 | 由逻辑门构建。 |

| 适用于时钟脉冲 | 适用于启用功能输入 |

| 有时钟信号 | 没有时钟信号 |

| 边缘敏感,即FF的内容仅在使能信号的上升沿或下降沿(通常是控制时钟信号)改变。 在时钟信号的上升沿或下降沿之后,即使输入改变,FF的内容也保持不变。 | 电平敏感,即当其输入发生变化时,锁存器的内容立即改变。输出在使能信号有效脉冲的持续时间内是敏感的,因此,仅在有效脉冲期间可以发送或接收数据。 |

| 输入的采样仅在时钟事件中完成,例如,上升沿,下降沿。 | 仅当使能信号开启时,才连续进行输入采样。 |

最后

以上就是傻傻大象最近收集整理的关于寄存器、锁存器、触发器的区别锁存器(Latch)触发器(Flip-Flop,简称FF)寄存器的全部内容,更多相关寄存器、锁存器、触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复