1.设计方法学

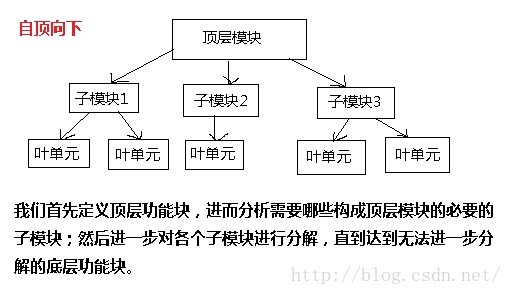

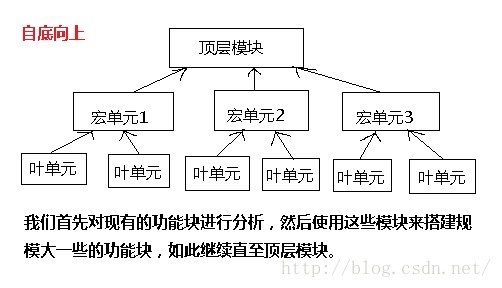

数字电路设计中有两种基本的设计方法:自底向上和自顶向下设计方方法。

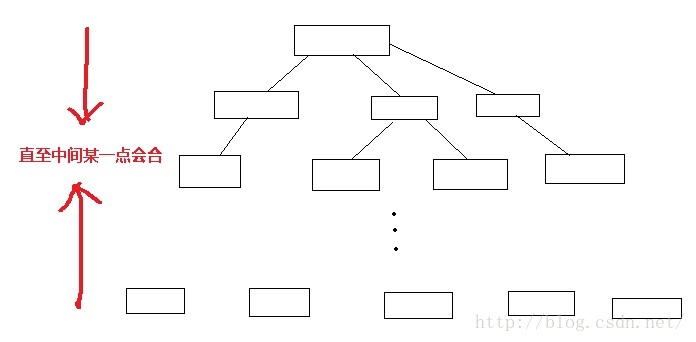

而在典型的设计中,这两种方法是混合使用的,设计人员首先根据电路的体系结构定义顶层模块。逻辑设计者确定如何根据功能将整个设计划分为子模块;与此同时,电路设计者对底层功能块电路进行优化设计,并进一步使用这些底层模块来搭建其高层模块。

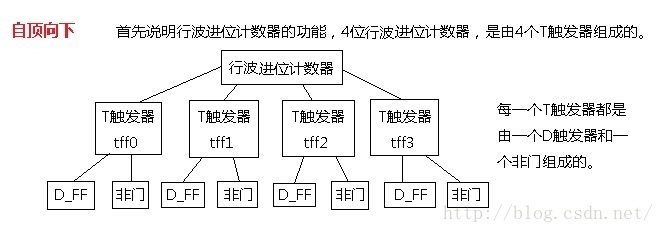

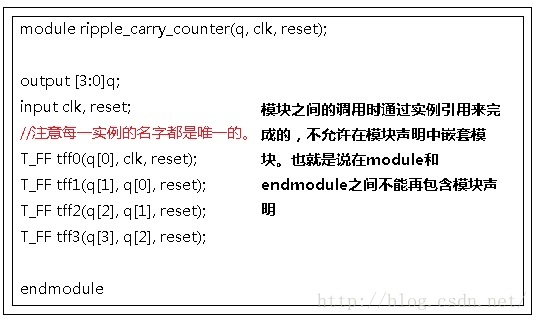

2.举个例子----四位行波进位计数器

3.模块

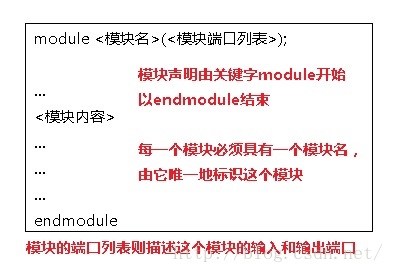

Verilog使用模块(module)的概念来代表一个基本的功能块,一个模块可以是一个元件,也可以是低层次模块的组合。

模块通过接口(输入和输出)被高层的模块调用,但隐藏了内部的实现细节。这样的话,设计者可以方便地对某一个模块进行修改,而不影响设计的其他部分。

根据设计需要,设计者在每个模块内部可以在4个抽象层次中进行描述,而模块对外显示的功能都是一样的。

抽象层次定义由高到低如下:

- 行为或算法级:设计者只注重其实现的算法,而不关心其具体的硬件实现细节。

- 数据流级:只关心数据是如何在各个寄存器之间的流动以及如何处理这些数据。

- 门级:从组成电路的逻辑门及其相互之间的互连关系的角度来设计模块。

- 开关级:通过使用开关、存储节点及其互连关系来设计模块。

Verilog允许设计者在一个模块中混合使用多个抽象层次。在数字电路设计中,术语寄存器传输级(RTL)描述在很多情况下是指能够被逻辑综合工具接受的行为级和数据流级的混合描述。

一般来说,抽象的层次越高,那么设计的灵活性和工艺无关性就越强;随着抽象层次的降低,灵活性和工艺无关性就越差,微小的调整可能会导致对设计的多处修改。这就类似于C语言与汇编语言,如果使用汇编语言,则需要针对特定的计算机,可移植性差。

4.模块实例

实例化(instantiation)与实例(instance):

当一个模块被调用的时候,verilog会根据模板创建一个唯一的模块对象,从模板创建对象的过程就叫做实例化,而创建的对象则被称为实例。

在上面的四位行波进位计数器中的例子可以看到,顶层模块根据T触发器的模块创建了4个具体的实例。然后每一个T触发器都实例化了一个D触发器和一个反相器。

5.逻辑仿真的构成

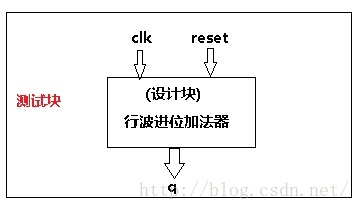

在设计完成之后,还必须对设计的正确性进行测试(test bench)。

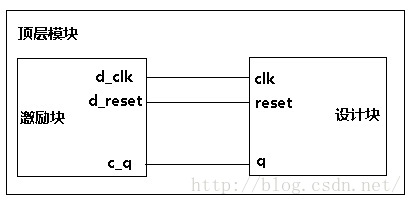

测试的设计有两种模式:

- 一种模式是在测试模块中调用并直接驱动设计块。

- 另一种模式是在一个虚拟的顶层模块中调用激励块和设计块。激励块和设计块之间通过接口进行交互。

最后

以上就是大胆山水最近收集整理的关于[verilog读书笔记]2.层次建模的全部内容,更多相关[verilog读书笔记]2内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[verilog读书笔记]2.层次建模](https://www.shuijiaxian.com/files_image/reation/bcimg11.png)

发表评论 取消回复