一、基本概念

-大小写:相关,关键字均为小写;

-注释:同C语言,

//为单行注释

/* 多行

注释

不允许再嵌套多行注释*/

-操作符:同C,分单目、双目、三目;

-数字声明:

-指明位数:

<size>'<base format><number>

-<size>表示数字位宽度,表示位宽的数字前面加“-“(减号)表示其是一个负数,减号不能放于基数与数字之间。

-基数格式有:十六进制('h或'H)、十进制('d或'D)、八进制('o或'O)、二进制('b或'B)

-数字包含:0-9、a-f

-不指明位数:

没有指定基数,默认为十进制数;没有指定位宽度,默认与仿真器和使用的计算机相关

-X与Z:

x或X:不确定值

z或Z:高阻值,“?”是z的另一种表示

e.g.:12'h13x 12位十六进制数,四位低位不确定;

-数值表示:左边为最高有效位,右边为最低有效位;

-实数:十进制表示或指数表示均合法;

-数扩展:若某数的最高位为0、x、z,则分别用其进行扩展,填充其余更高位;若某数最高位为1,则用0来进行扩展;

-下划线:可以出现在数字中,编译阶段会被忽略,"12'b1111_0011_0000"是合法的。

-字符串:双引号括起来,不能多行书写;Verilog中字符串当作一个单字节的ASCII字符队列。转移标识符同C。

-逻辑状态:

0:逻辑0、逻辑非、低电平

1:逻辑1、逻辑真、高电平

x:不确定的逻辑状态

z:高阻态

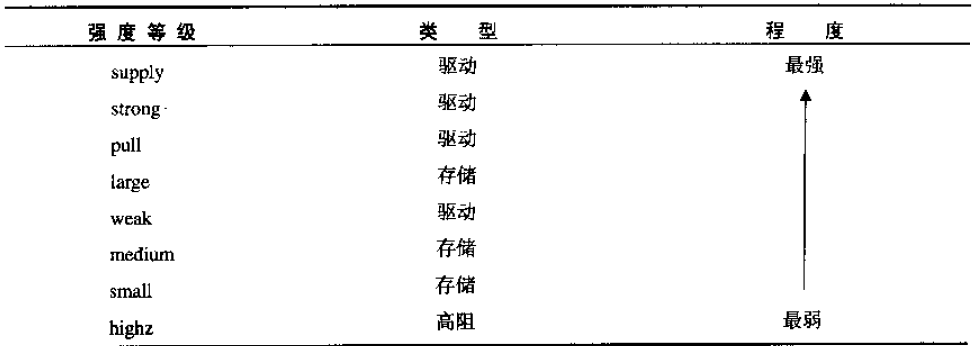

-强度值:

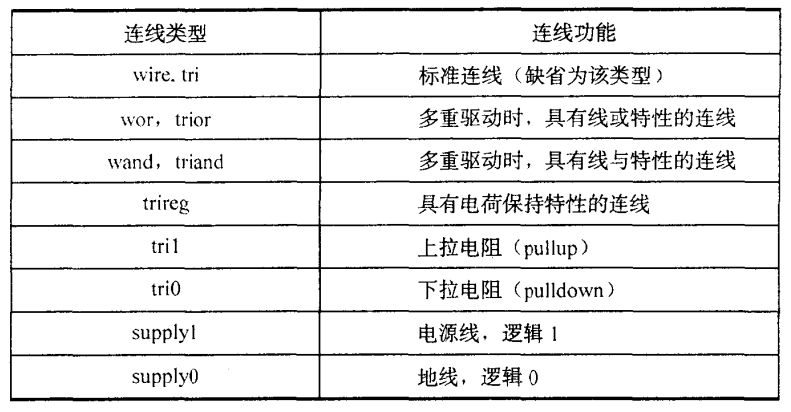

-线网(net):硬件单元之间的连接。包含一系列数据类型。线网由其连接器件的输出端连续驱动。

-寄存器(register):用来表示存储元件,保持原有数值直到被改写。仅表示一个保存数值的变量。不需要驱动源或时钟信号。使用关键字reg声明,默认值为x。也可以声明为带符号(signed)类型的变量。

e.g.:reg signed [63:0] m;//声明64位带符号值

-向量:通过[high#:low#]或[low#:high#]说明,括号中左边数总是表示向量的最高有效位。可以指定向量的某一位或若干个相邻位。

e.g.:wire [7:0] bus;

reg [0:40] virtual_addr;//最高有效位是第0位

Bus[2:0]//最低三位

virtual_addr[0:1]//两个最高位

-可变的向量域选择:

[<starting_bit>+:width]:从起始位置开始递增,位宽为width

[<starting_bit>-:width]:从起始位置开始递减,位宽为width

起始位可以是变量,但位宽必须是常量。

-整数:integer

-实数:real

-时间寄存器:time,通过调用系统函数$time可以得到当前仿真时间。

-数组:<数组名>[<下标>]

e.g.:integer count[0:7];

reg [4:0] port_id[0:7];

integer matrix[4:0][0:255];//二维数组

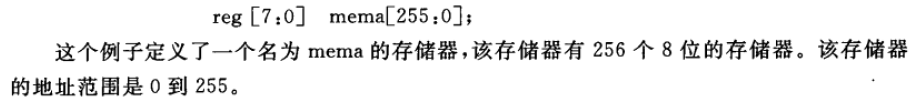

-存储器:使用寄存器的一位数组来表示存储器。

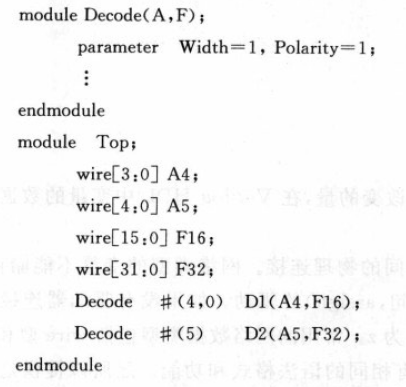

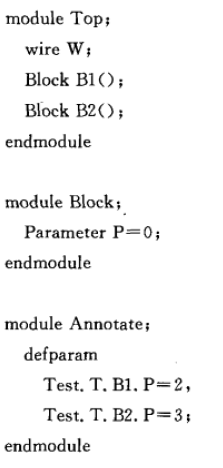

-参数:使用关键字parameter在模块内定义常数,不能像变量那样赋值,可以在编译阶段被重载,可以通过模块实例化或使用defparam语句改变参数值。使用localparam来定义局部参数,值不能改变,不能通过参数重载语句或通过有序参数列表或命名参数赋值来直接修改。

-通过模块实例化修改:

在模块实例化时可以改变参数值,#(5)只修改Width的值。

-通过defparam修改:

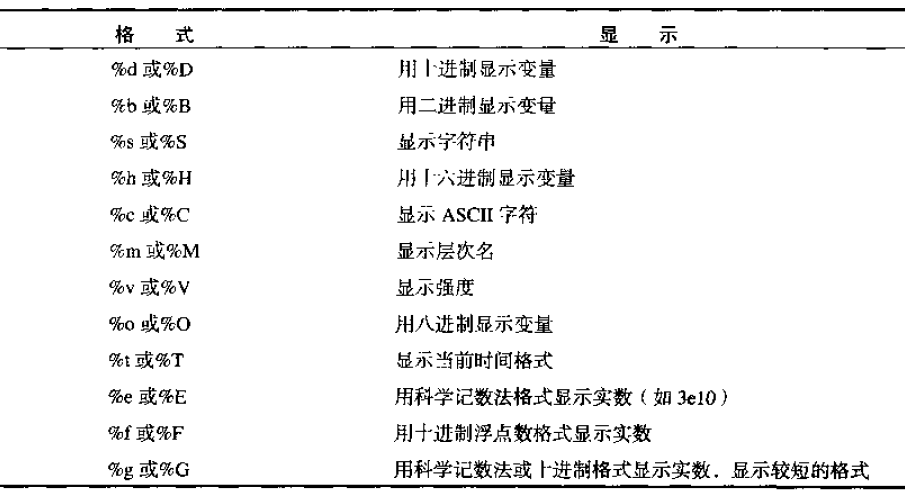

-系统任务(系统函数):常用的有:

显示信息:$display(p1,p2,p3,……);

格式类似printf

监视信息:$monitor(p1,p2,p3,……);

$monitoron;

$monitoroff;

格式类似printf,进行不间断监视,当发生变化时显示所有参数数值。

暂停结束仿真:$stop $finish

-编译指令: `<keyboard>(撇号是键盘左上角的波浪线的撇号`,不是单引号')

`define:用于定义文本宏;如定义全局变量,调用全局变量时也要加`撇号。

`include:用于将内含全局或公用定义的头文件包含在设计文件中。

二、层次建模

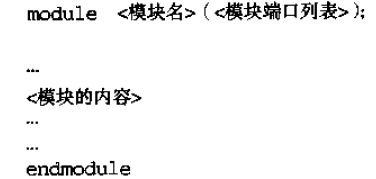

模块 (module):基本功能单元

Verilog使用模块的概念(module)来代表一个基本的功能块。模块通过接口(输入和输出)被高层的模块调用,但隐藏了內部的实现细节。

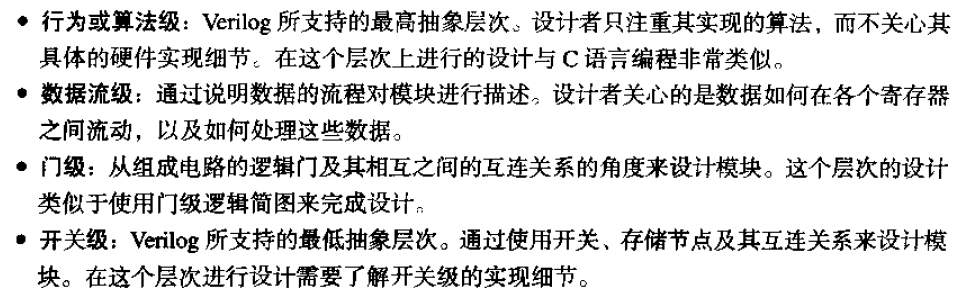

在每个模块内部可以在四个抽象层次中进行描述,而对外显示的功能都是一样的,仅与外部环境有关:

-允许在一个模块中有=混合使用多个抽象层级。

-RTL(寄存器传输级Register transfer level)描述在很多情况下是指能够被逻辑综合工具接受的行为级和数据流级的混合描述。

-一般来说抽象的层次越高,设计的灵活性和工艺无关性越强。

-不允许在模块声明中嵌套模块。

-在设计数字电路时采用自顶向下方法与自底向上方法的结合的方式。

当一个模块被调用时Verilog会根据模板创建一个唯一的模块对象。

-从模板创建对象的过程称为实例化,创建的对象称为实例。

逻辑仿真

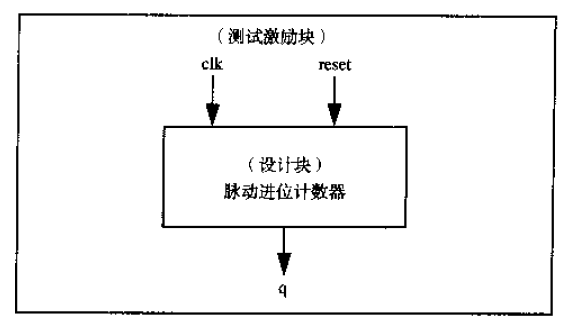

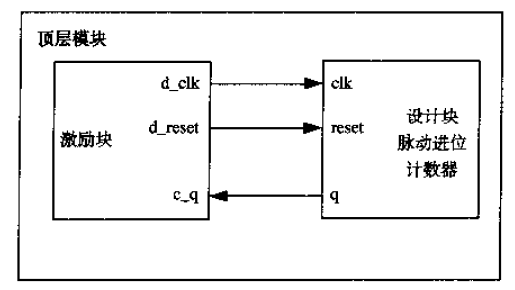

完成测试功能的块称为激励块,一般均称做测试台,同样可以使用Verilog来描述。有两种模式:

一种模式是在激励块中调用实例应用并直接驱动设计块:

一种是在虚拟的顶层模块中调用实例应用激励块和设计块,块之间通过接口进行交互:

最后

以上就是无辜黄蜂最近收集整理的关于verilog | 一、基本概念与层次建模一、基本概念二、层次建模的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复