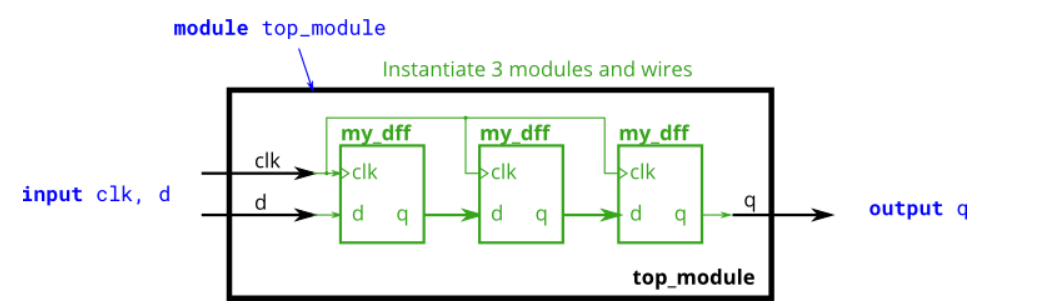

1 Three modules(Module shift)

作业:您将获得一个my_dff具有两个输入和一个输出的模块(实现 D 触发器)。实例化其中三个,然后将它们链接在一起以形成长度为 3 的移位寄存器。clk端口需要连接到所有实例。

提供给您的模块是: module my_dff ( input clk, input d, output q );

注意:要在模块内部进行连接,您可能需要先声明一些连线。 注意命名连线和模块实例时,它们的名字必须是唯一的。

module top_module ( input clk, input d, output q );

wire output1,output2;

my_dff instance1(.clk(clk),.d(d),.q(output1));

my_dff instance2(.clk(clk),.d(output1),.q(output2));

my_dff instance3(.clk(clk),.d(output2),.q(q));

endmodule

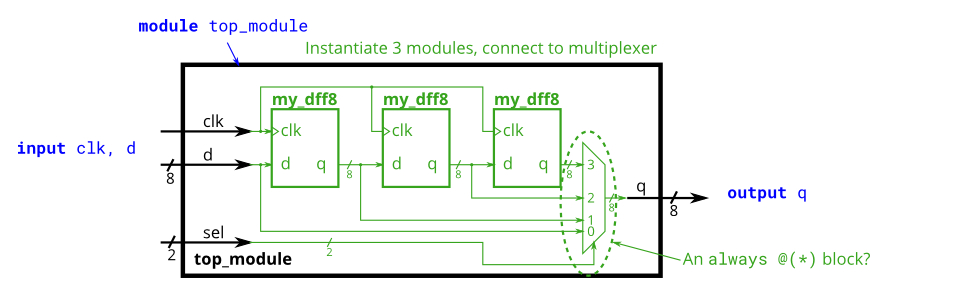

2 Modules and vectors(Module shift8)

作业:本练习是module_shift的扩展. 模块端口不再只是单个引脚,我们现在有带有矢量作为端口的模块,您将在其上连接线矢量而不是普通线。与 Verilog 中的其他任何地方一样,端口的向量长度不必与连接到它的电线匹配,但这会导致向量的零填充或截断。本练习不使用矢量长度不匹配的连接。

您将获得一个my_dff8具有两个输入和一个输出的模块(实现一组 8 个 D 触发器)。实例化其中的三个,然后将它们链接在一起以形成一个长度为 3 的 8 位宽移位寄存器。此外,创建一个 4 对 1 多路复用器(未提供),根据以下条件选择输出内容sel[1:0]: 输入值d,在第一个之后,在第二个之后,或者在第三个 D 触发器之后。(本质上,sel选择延迟输入的周期数,从零到三个时钟周期。)

提供给您的模块是: module my_dff8 ( input clk, input [7:0] d, output [7:0] q );

不提供多路复用器。一种可能的写法是在always一个case语句块中。

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0] output1,output2,output3;

my_dff8 instance1(.clk(clk),.d(d),.q(output1));

my_dff8 instance2(.clk(clk),.d(output1),.q(output2));

my_dff8 instance3(.clk(clk),.d(output2),.q(output3));

always @(*)

case(sel)

2'h0: q = d;

2'h1: q = output1;

2'h2: q = output2;

2'h3: q = output3;

endcase

endmodule

最后

以上就是威武大象最近收集整理的关于HDLBits之Verilog学习记录 Day7的全部内容,更多相关HDLBits之Verilog学习记录内容请搜索靠谱客的其他文章。

![[文档].艾米电子 - 触发器与锁存器,Verilog](https://www.shuijiaxian.com/files_image/reation/bcimg8.png)

发表评论 取消回复