文章目录

- 一、触发器

- 二、D-FF结构

- 三、亚稳态

- 四、建立时间和保持时间

- 五、时序分析

- 六、电路评估分析

- 七、单相时钟同步电路

一、触发器

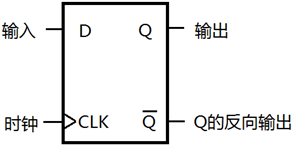

- 触发器(Flip Flop,FF)是一种只能存储1个bit的存储单元。FPGA逻辑单元内的D触发器(D-FF)就是一种在时钟上升沿(或下降沿)将输入信号的变化传输到输出端的边沿触发器。如下图D-FF在CLK上升沿将输入值传输到输出Q。

| D | CLK | Q | /Q |

|---|---|---|---|

| X | L | Qn | /Qn |

| L | 上升沿 | L | H |

| H | 上升沿 | H | L |

| X | H | Qn | /Qn |

| X | 下降沿 | Qn | /Qn |

二、D-FF结构

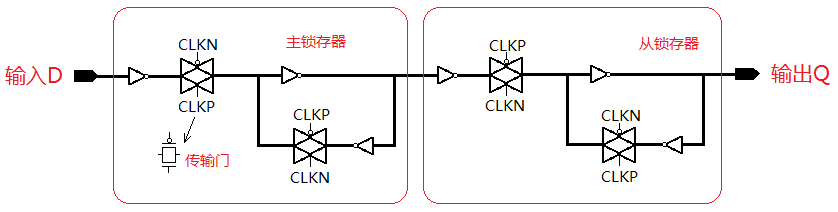

- CMOS工艺下D-FF(Double-Flip Flop)结构由传输门(起开关作用,随CLK变化切换开关)和两个反向器组成一个循环电路(锁存器,latch),再由前后两级锁存器按主从结构连接而成。

- 为了防止时钟信号变化时输入信号发生冒险(电平冲突),前级锁存器CLK相位应与输入信号电路CLK反向。

三、亚稳态

- 亚稳态(metastable)指在0和1之间的摇摆的中间电位。

四、建立时间和保持时间

- 建立时间和保持时间的作用都在于防止亚稳态。

- 建立时间(setup time)用于约束在时钟上升沿到来前输入D保持稳定的时间。(给输入D稳定的时间)

- 保持时间(hold time)用于防止在CLK=1时,输入D在传输门关闭前状态发生改变,从而使本应在下一周期读取的数据提前进入锁存器导致反相器环路震荡或产生亚稳态。(给传输门关闭的时间)

五、时序分析

- 硬件描述语言(Hardware Description Language,HDL)编写的RTL(Register Transfer Level,寄存器传输级)设计代码生成网表(逻辑门间的配线顺序)的过程称为逻辑综合。

六、电路评估分析

- 采用动态时序分析(Dynamic Timing Analysis)需要实时分析每个逻辑值,太过于耗时。所以FPGA的性能评估主要采用静态时序分析(Static Timing Analysis,STA)。

七、单相时钟同步电路

- FPGA主要采用同步电路设计,而同步电路又可使用STA进行时序分析和验证,验证速度快但所有FF必须同时接收到时钟信号。但实际上由于时钟信号驱动负荷(扇出数)、布线延迟会导致不能满足条件。这种时钟信号到达时间的错位成为时钟偏移(skew)。另外,由于时钟振荡器的变动或信号变形,时钟边沿会偏离平均位置,这种情况称为时钟抖动(jitter)。考虑到这些,FPGA已经提前实现了多层时钟树结构,并且通过驱动能力强的专用布线(global buffer)将时钟低偏移地连接到所有FF上。

参考书籍:《FPGA原理和结构》——田野英晴

最后

以上就是顺心刺猬最近收集整理的关于FPGA学习笔记(二)同步电路设计的全部内容,更多相关FPGA学习笔记(二)同步电路设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[文档].艾米电子 - 触发器与锁存器,Verilog](https://www.shuijiaxian.com/files_image/reation/bcimg8.png)

发表评论 取消回复