个人实验158页的图2.0、5.1、5.2、5.3。

一、实验名称:

1.四位移位寄存器的另一种代码;

2.一个n位移位寄存器;

3.递增计数器;

4.带并行载入端的递增计数器。

二、实验内容:

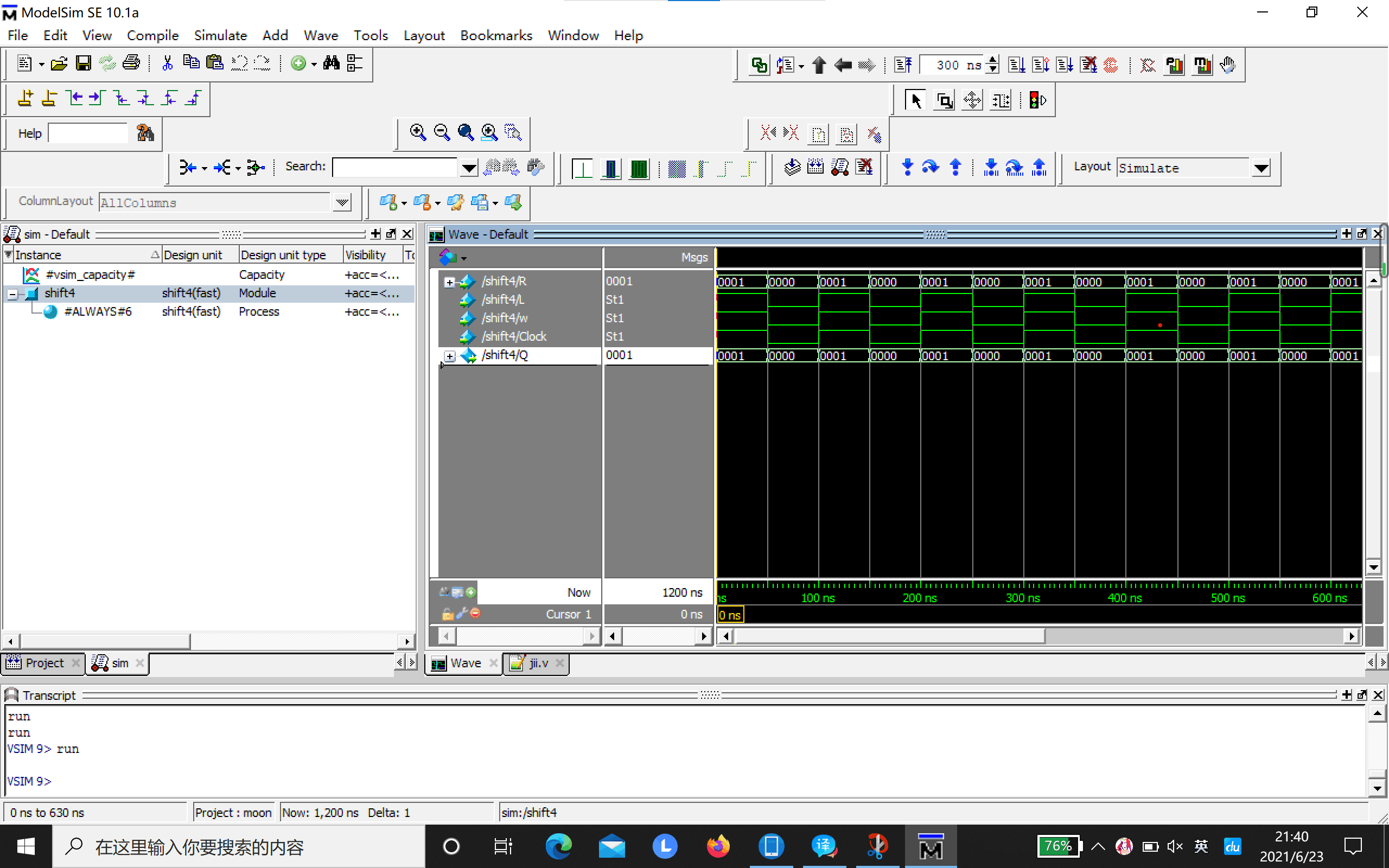

实验一:所有的操作都发生在时钟上升沿。如果L=1,4位数据R并行加载到寄存器;如果R=0,寄存器的内容向右移位,并且w输入端的值加载到最高位Q3。

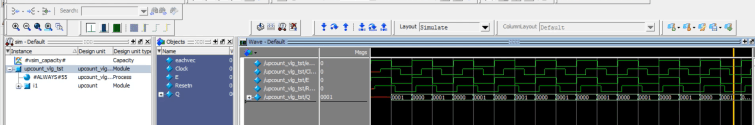

实验二:R和Q的位宽用n定义,描述移位操作的else分支语句用for循环语句实现,可适用于由任意多个触发器组成的移位操作。

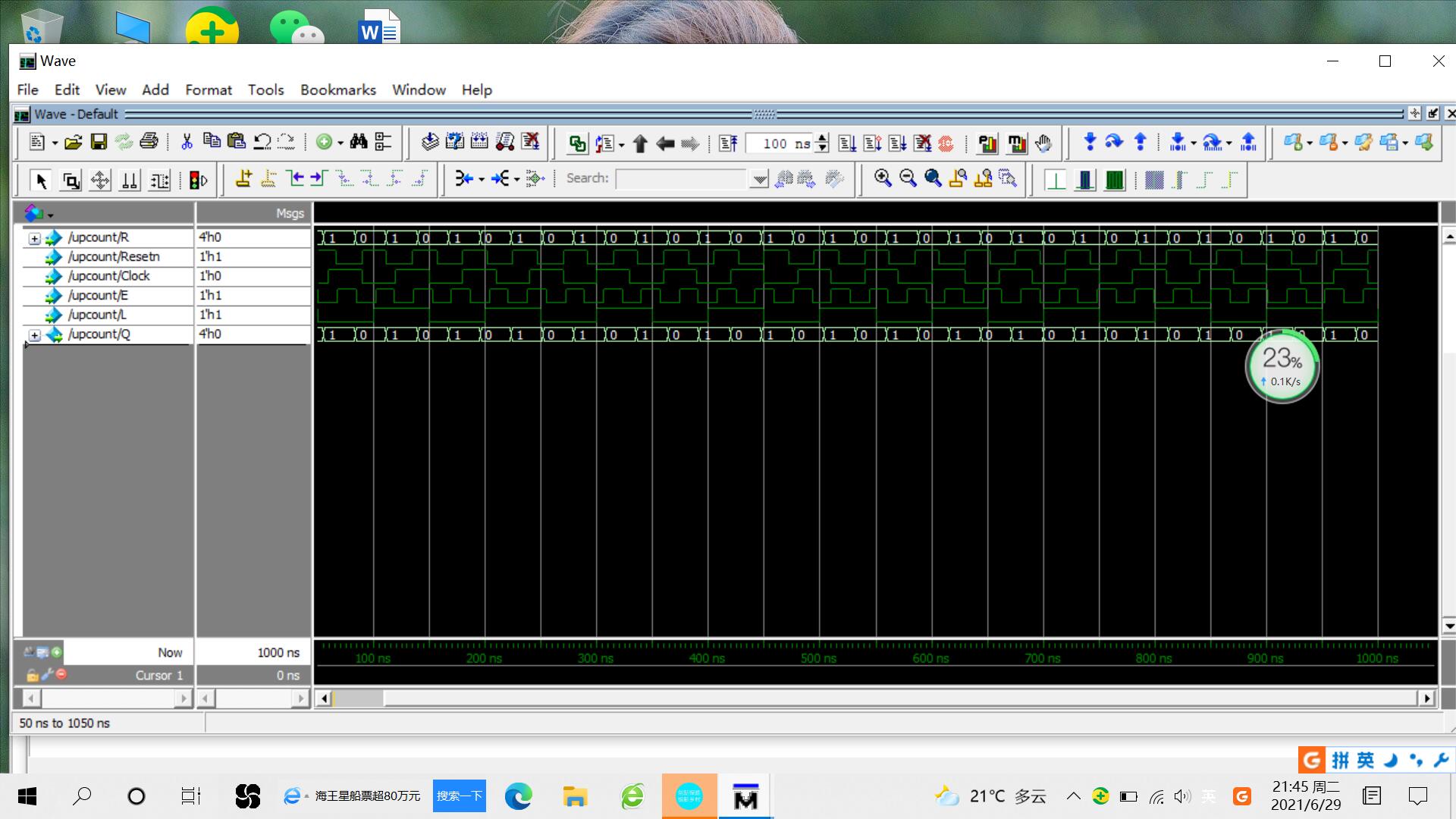

实验三:具有复位输入resetn 和使能输入E的4位递增计数器。计数器中触发器的输出用名位Q的向量表示。

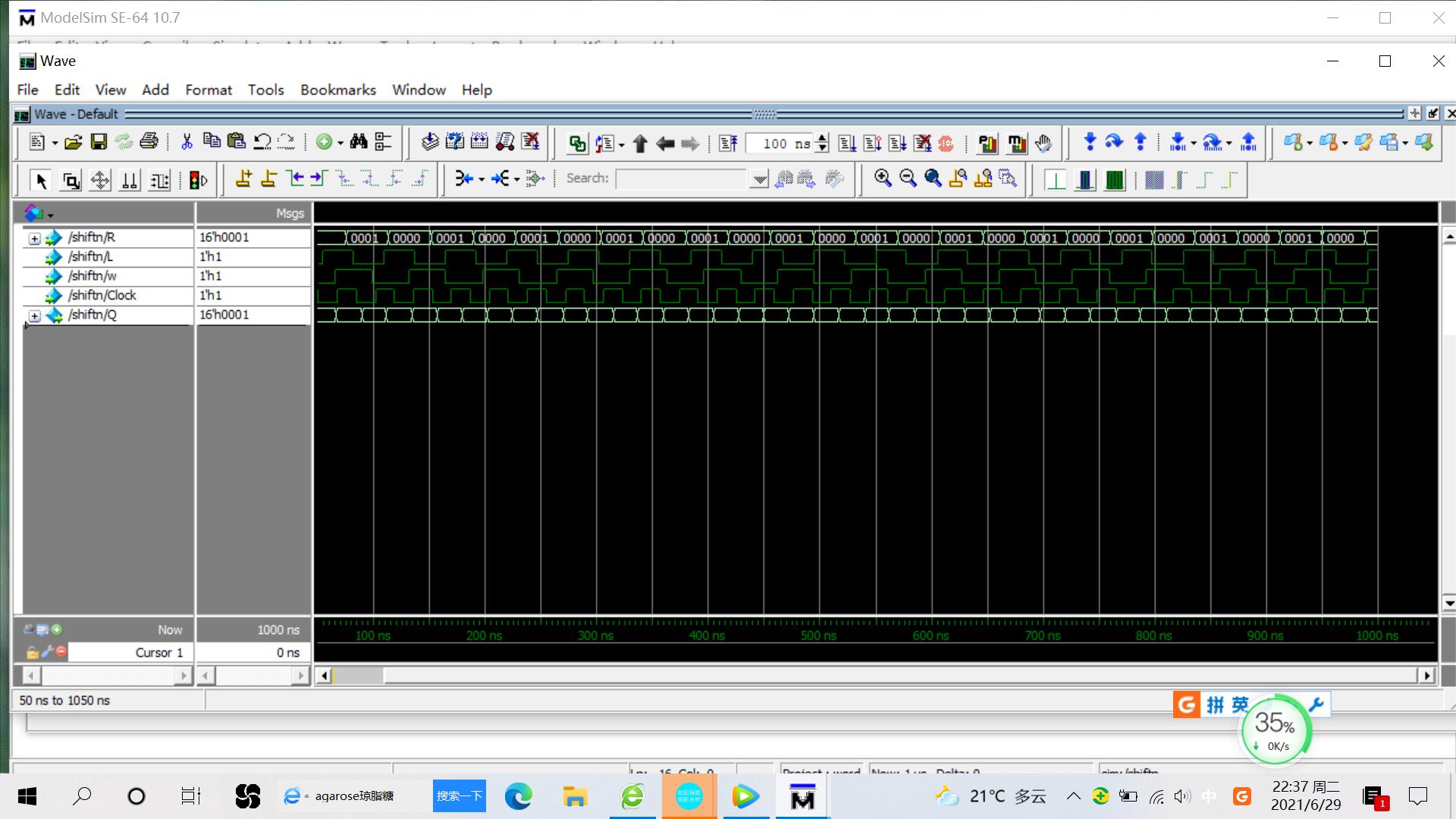

实验四:计数器除了输入端以外,还有一个并行加载输入端,并行加载输入端,并行数据由输入向量R提供。

三、实验截图:

1.

2.

3.

4.

四、实验代码:

1.module upcount (R, Resetn, Clock, E,L,Q);input [3:0] R;

input Resetn, Clock, E, L;

output reg [3:0] Q;

always @(negedge Resetn, posedge Clock)if (!Resetn)

Q<=0;

else if(L)

Q<= R;

else if(E)

Q<=Q+ 1;

endmodule

2.module shift4 (R,L,w,Clock,Q);

input [3:0]R;

input L,w,Clock;

output wire [3:0]Q;

muxdff Stage3(w,R[3],L,Clock,Q[3]);

muxdff Stage2(Q[3],R[2],L,Clock,Q[2]);

muxdff Stage1(Q[2],R[1],L,Clock,Q[1]);

muxdff Stage0(Q[1],R[0],L,Clock,Q[0]);

endmodule

3.module shiftn(R,L, w,Clock,Q;parameter n=16;

input [n-1:0]R;

input L w, Clock;

output reg [n -1:0] Q;integer k;

always @(posedge Clock)if(L)

Q<= R;

else

begin

for(k=0;k< n-1;k= k+1)Q[k]<二Q[k+1];

Q[n-1]<= w;

end

endmodule

4.module upcount(Resetn, Clock, E, Q);

input Resetn,Clock,E;

output reg [3:0] Q;

always @(negedge Resetn, posedge Clock)

if(!Resetn)

Q<= 0;

else if (E)

Q<=Q+1;

endmodule

五、实验视频:

1.【数字逻辑电路实验-哔哩哔哩】https://b23.tv/3KUdPw

2.【数字逻辑电路实验分析-哔哩哔哩】https://b23.tv/kSjN6U

3.【数字逻辑-哔哩哔哩】https://b23.tv/iaJjIy

最后

以上就是英勇手链最近收集整理的关于2021-06-30的全部内容,更多相关2021-06-30内容请搜索靠谱客的其他文章。

![[文档].艾米电子 - 触发器与锁存器,Verilog](https://www.shuijiaxian.com/files_image/reation/bcimg8.png)

发表评论 取消回复