文章目录

- 1. 综合脚本

1. 综合脚本

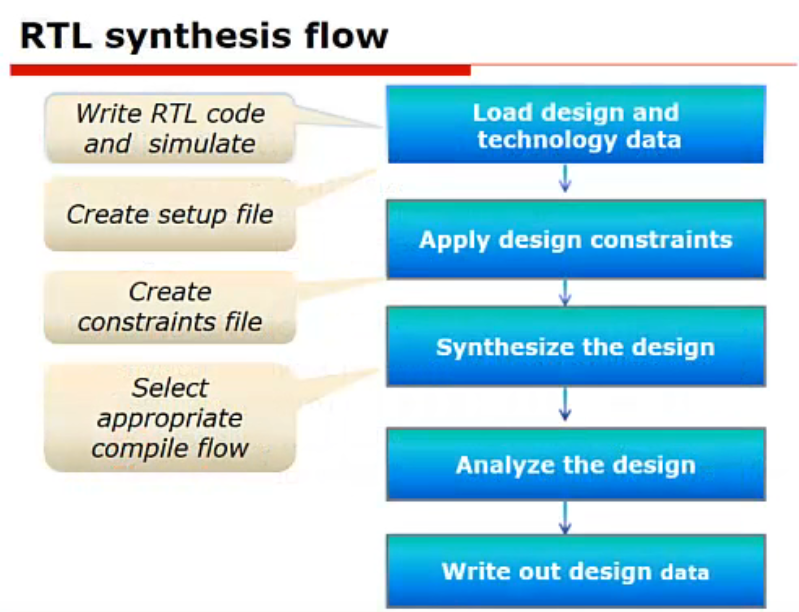

- 输入代码、约束、工艺库,DC输出网表

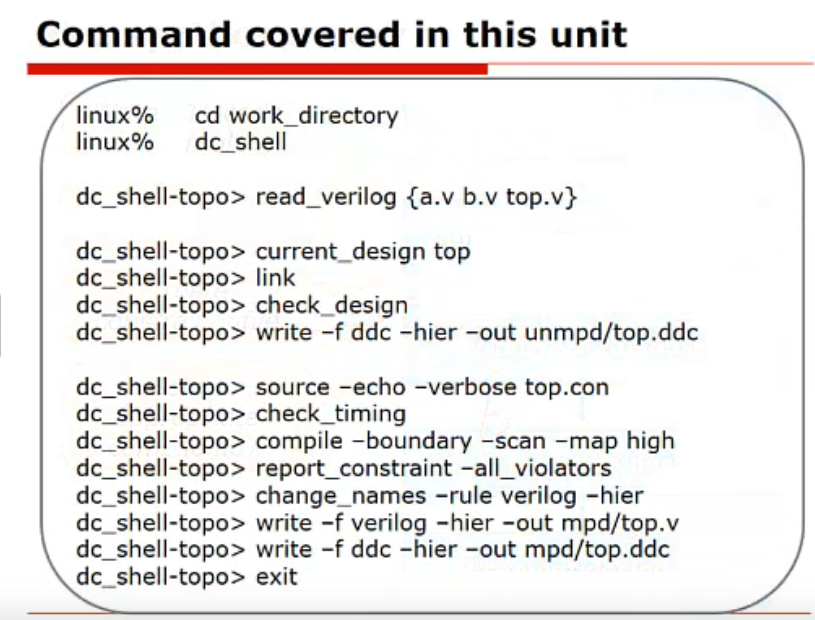

- 一些主干命令

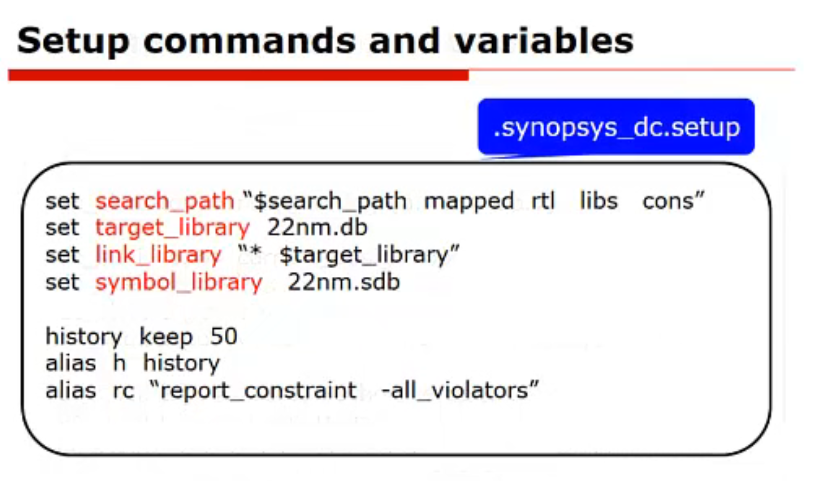

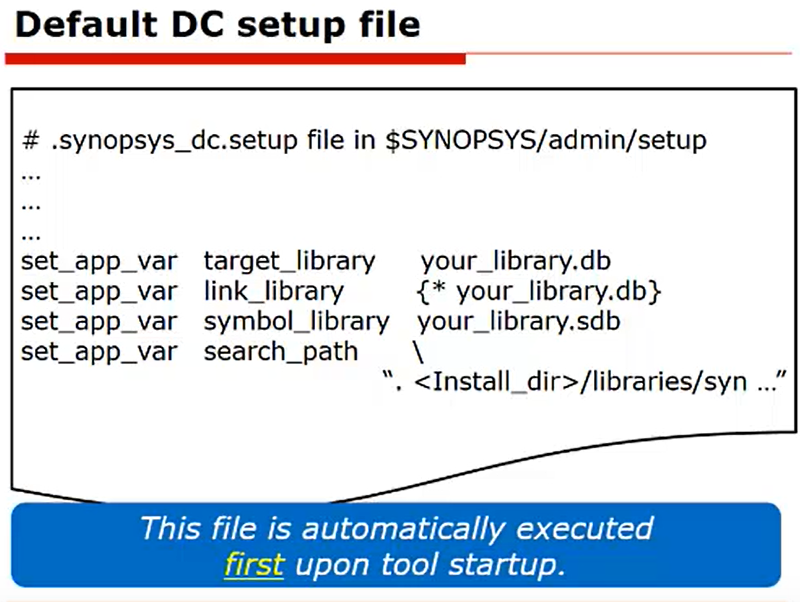

- .synopsys_dc.setup是DC自带的设置脚本名称

- 上图红色的变量是DC内部的

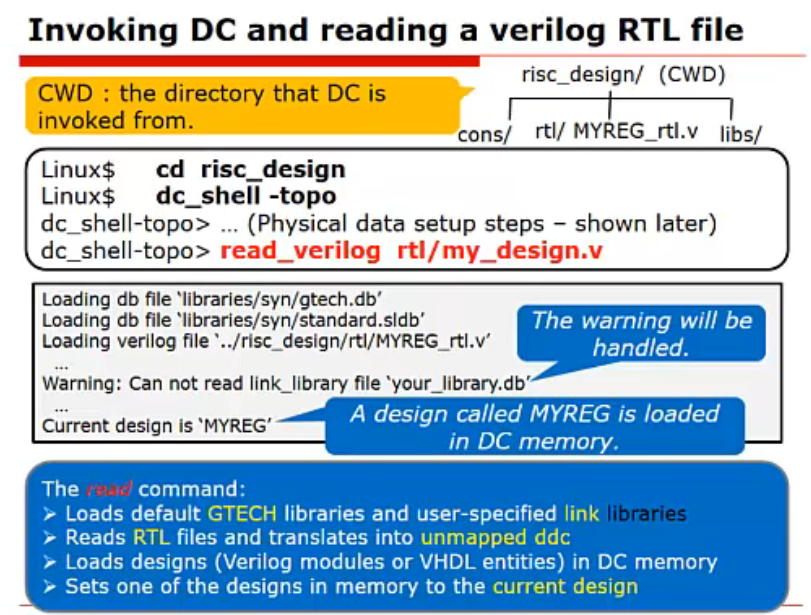

- 创建工程目录,一般约束、代码、库分3个目录

- 库文件一般有两种格式:lib给人看,db给工具看。lib也可编译产生db。

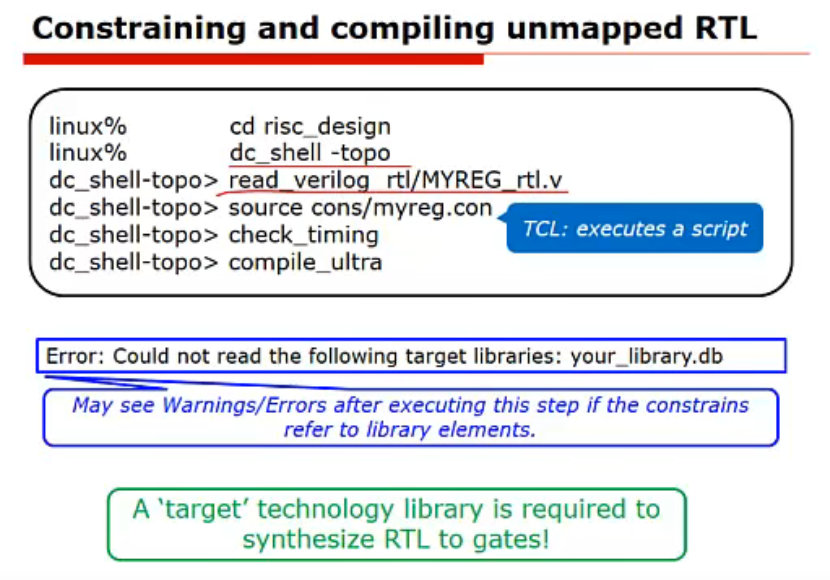

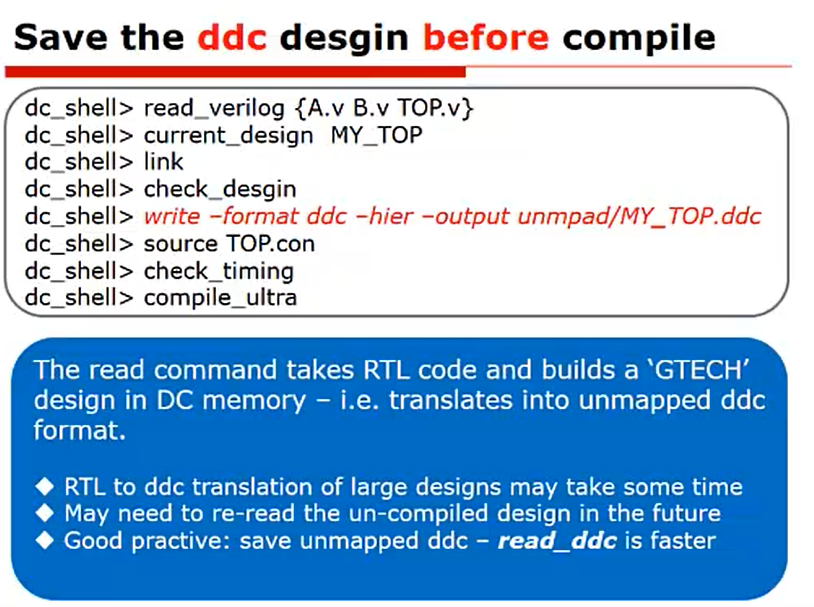

- read_verilog的功能有4点,如上图。GTECH是generic-tech通用库,无工艺特性,只有逻辑特性。

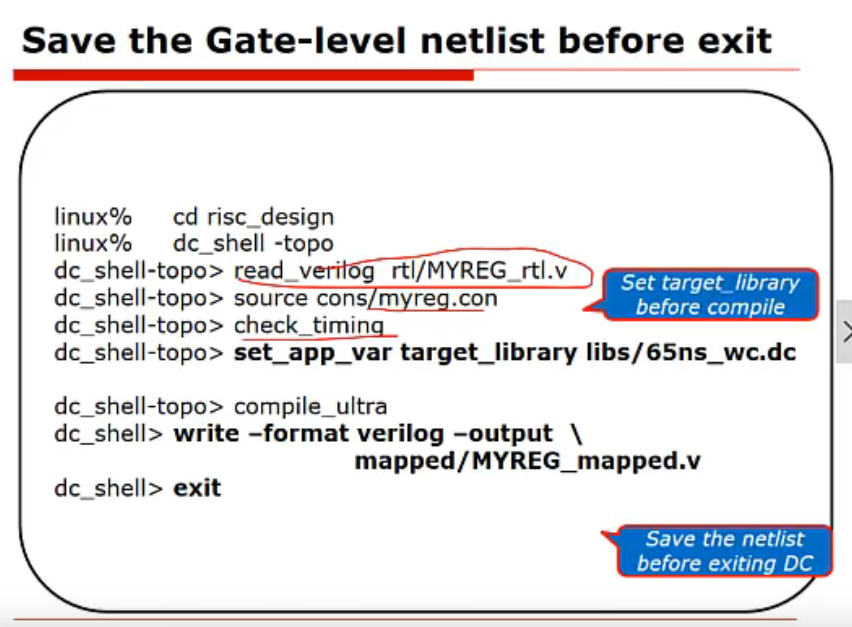

- source 约束脚本,应用我们的时序约束

- check_timing:检查是否存在未约束的路径,DC的综合是基于路径的,若存在没有约束的路径,那么DC综合结果就不可靠。

- compile_ultra:编译

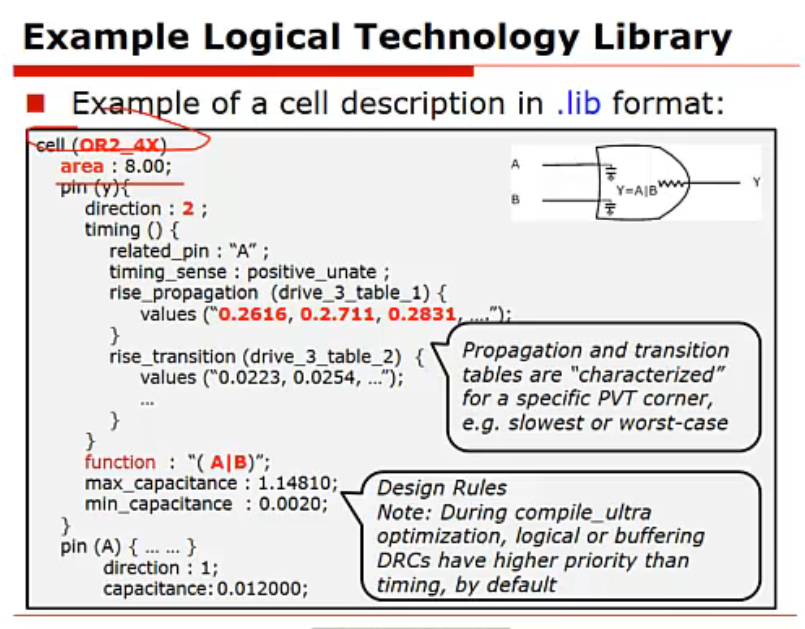

- 上升延迟:可能是逻辑单元的延迟

- 转换时间:电平从20%上升到80%的时间

- max_capacitance:Y输出端最大驱动的电容值,表示带负载能力

- Pin(A)的capacitance:表示A pin等效电容值

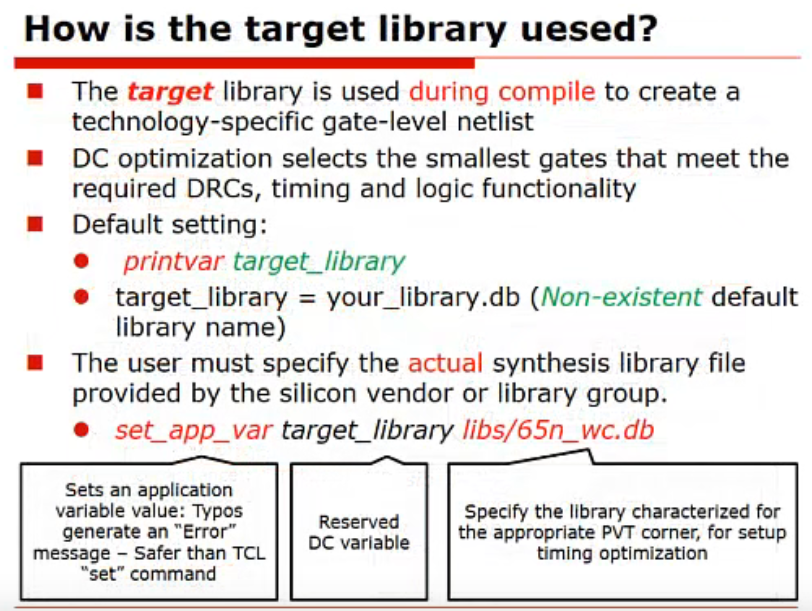

- target_lib:我们映射所需要的工艺库

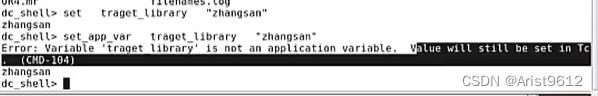

- set_app_var:比set更安全,设置工艺库等。只能设置DC自带的一些变量。比如target_library、link_lib、symbol_lib等。若设置的不是DC自带的就会报错

- set:可以设置DC自带的,也可以设置我们自定义的

- 上面是执行综合的几个重要步骤,有先后顺序关系

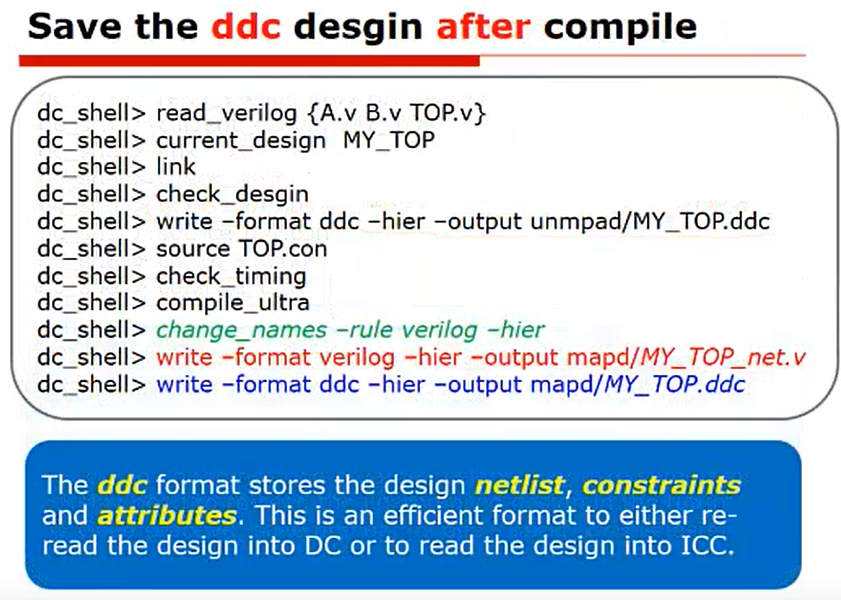

- 输出.v和.ddc文件,ddc=v+sdc,后仿真可用sdf包括延迟信息

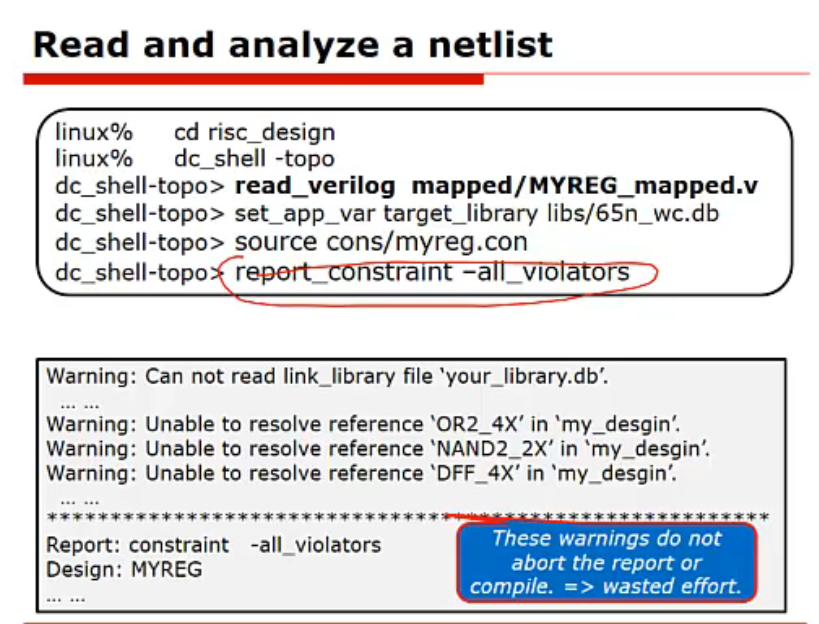

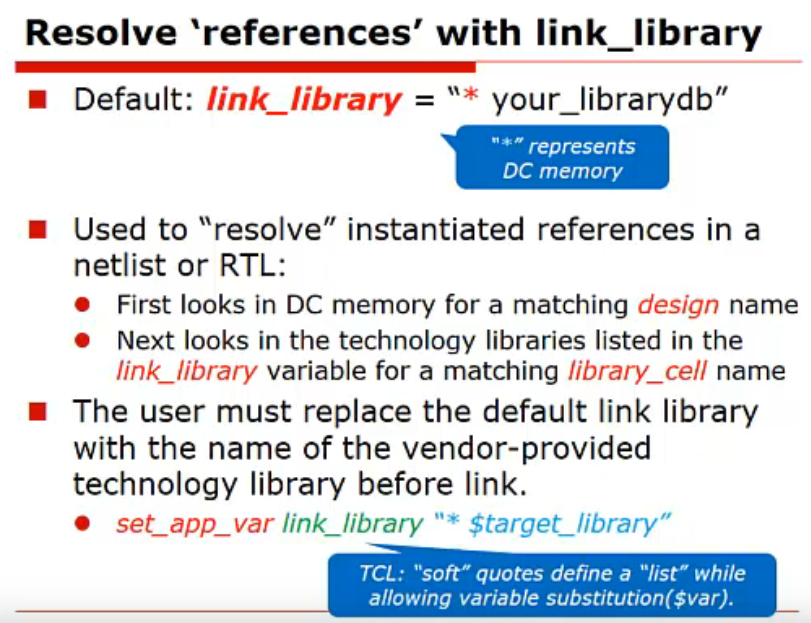

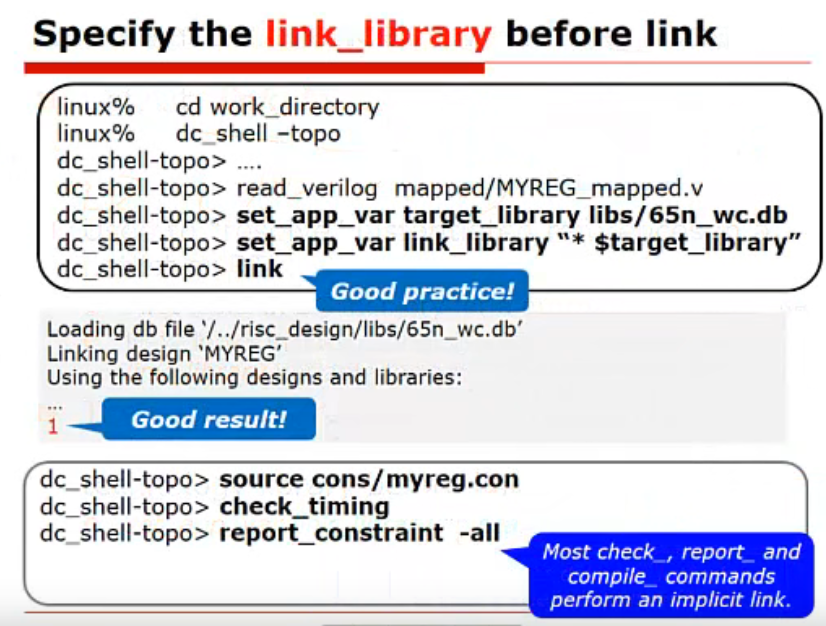

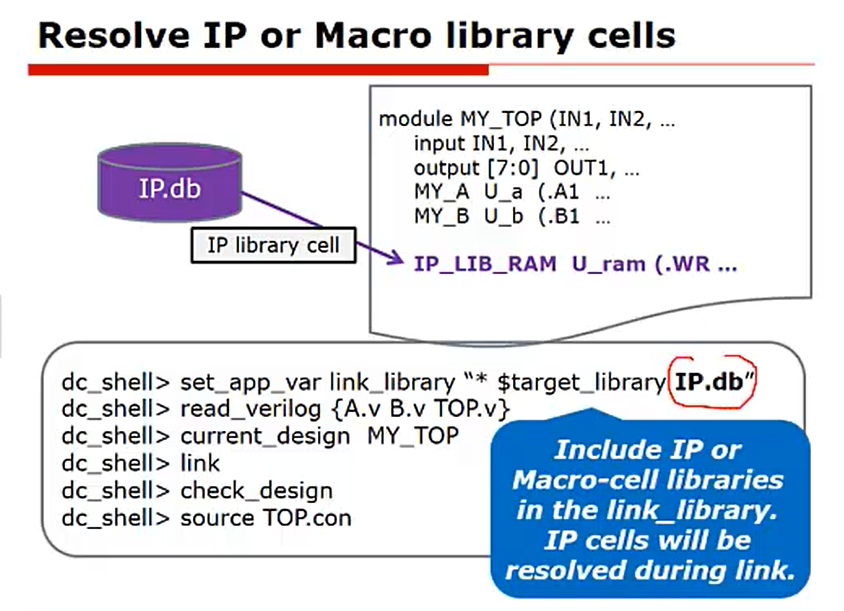

- link_lib:不仅包括工艺库即target_lib还包括IP,应该是link使用的全部器件的集合库

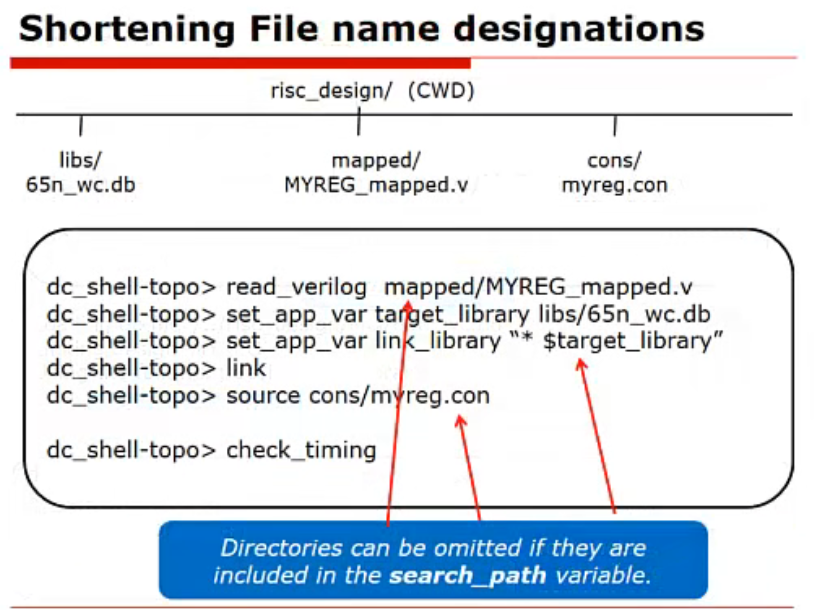

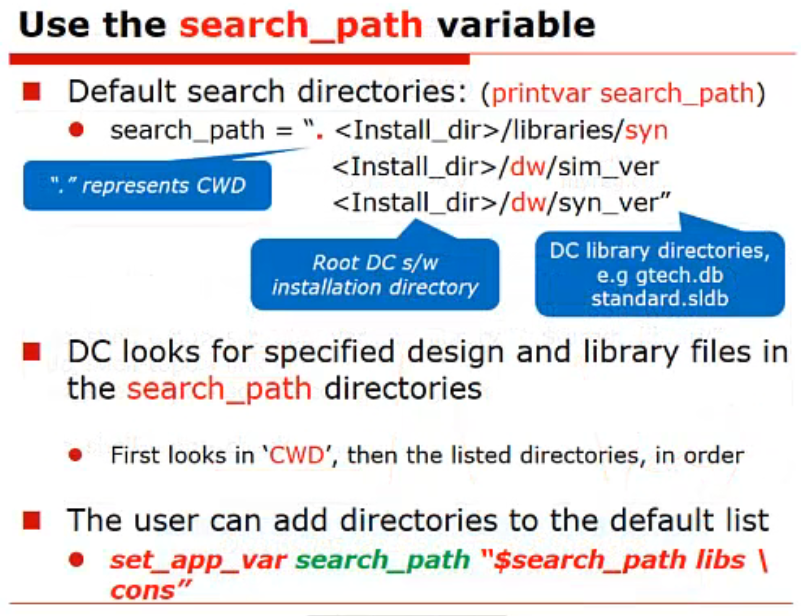

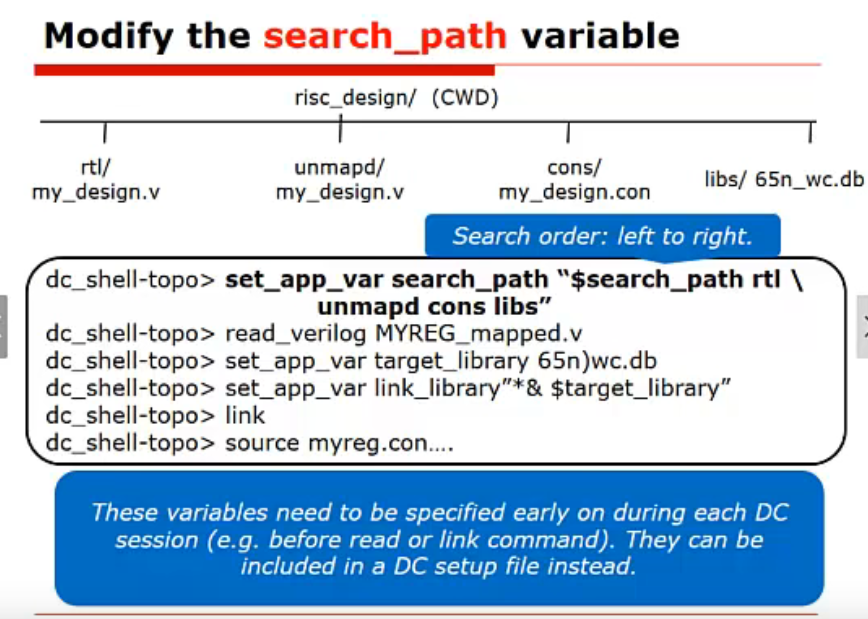

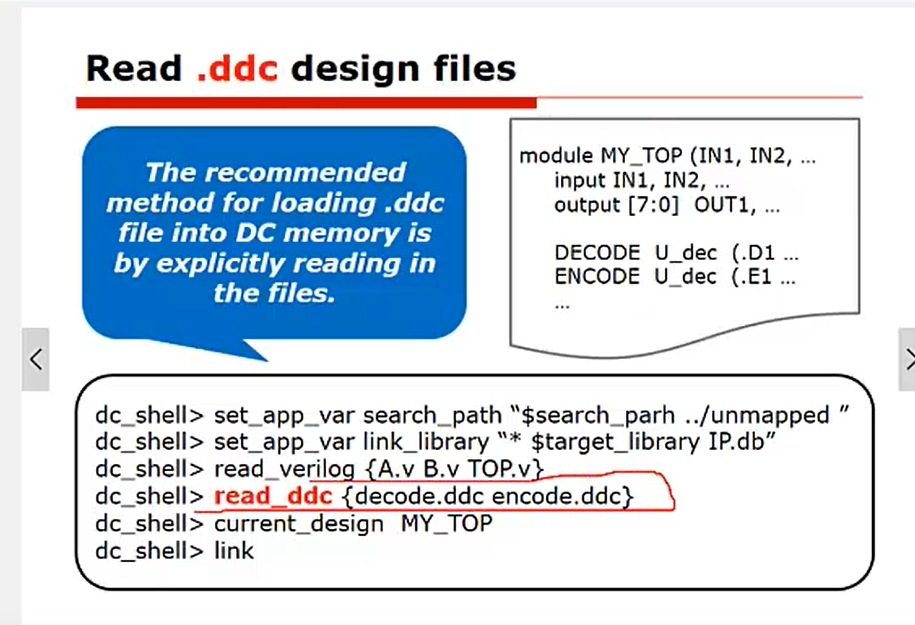

- search_path可以是一组地址,若我们在加载文件的时候没有指定路径,那DC就会在search_path中去找

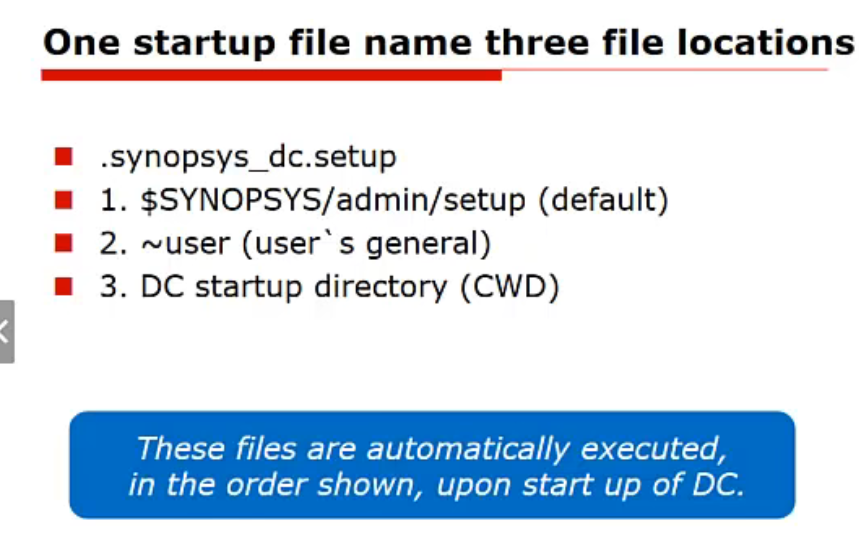

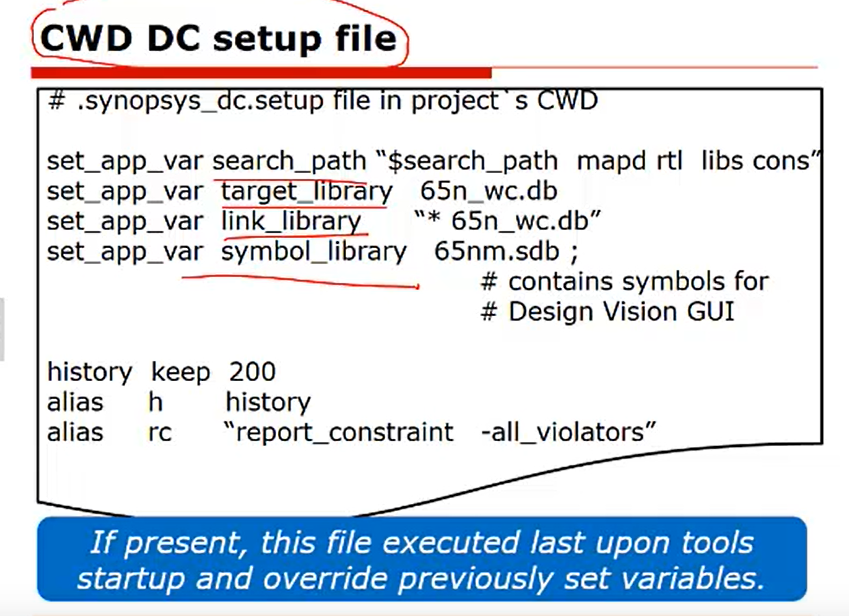

- 通常setup文件有3个位置,上图所示,优先级依次升高,分别是安装目录下,home目录下,项目的工作目录下。我们一般修改第三个

- 该文件名称是固有的,通常设置search_path、以及lib信息。DC启动时候会自动source

- 上图是setup文件的一个实例,link_library后的*代表当前DC运行所开辟的内存空间(可能主要是target_library),后面.db是另外加入的IP等,可以是.db、.ddc格式

- 也可以使用read_ddc加入IP的.ddc文件

- symbol_library添加cell的图形库

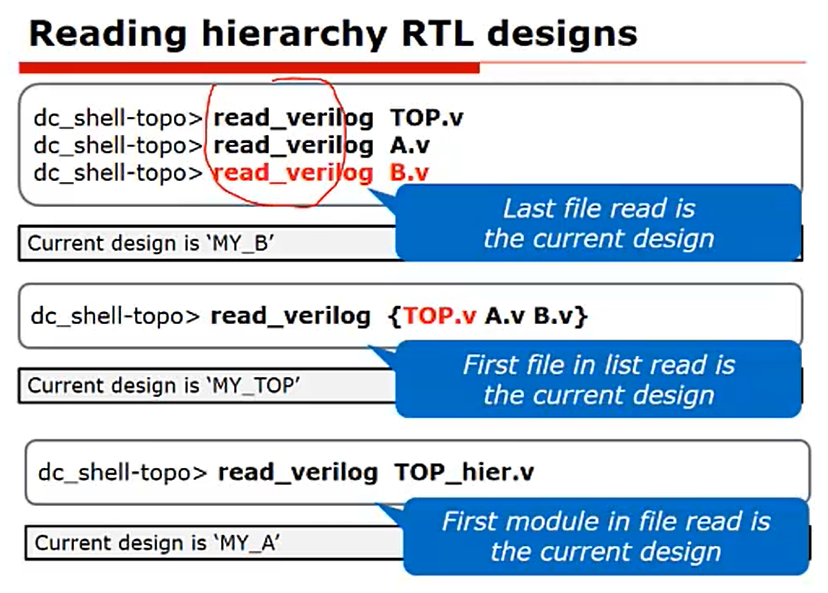

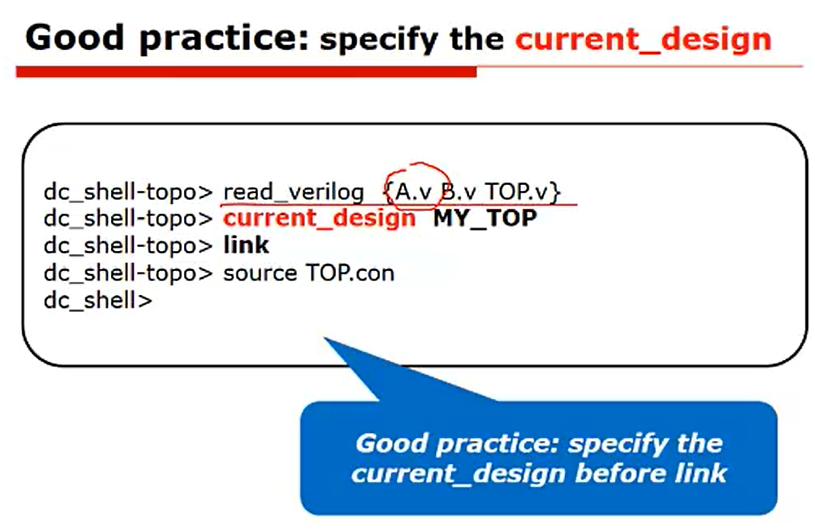

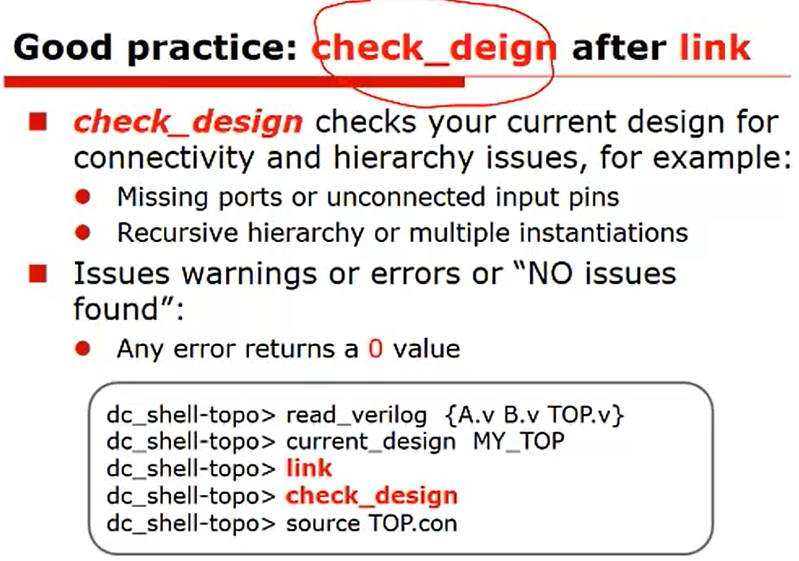

- 不同的read_verilog的加载方式会对应不同的顶层(current_design),但是一般我们是在link之前使用直接指定的方式

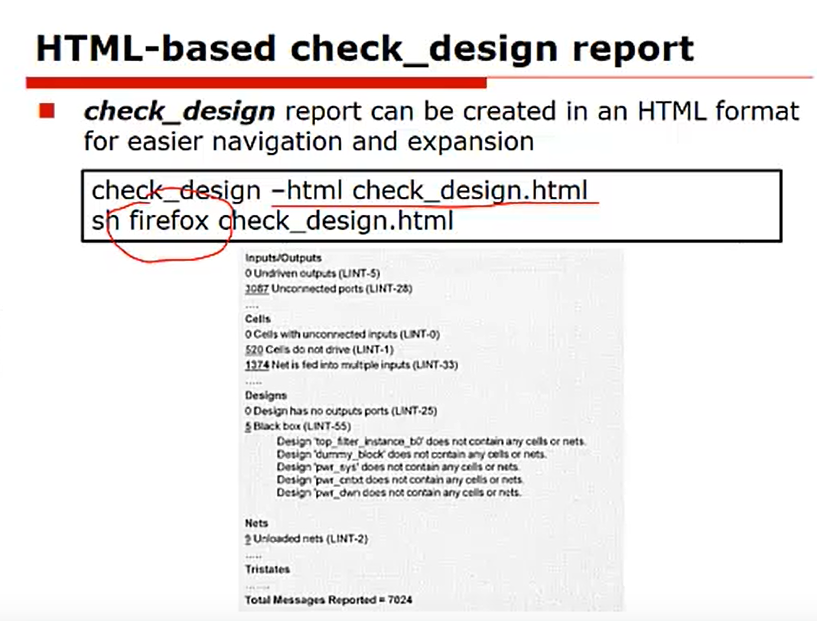

- check_design:检查设计中有没有port没链接或者层次例化方面的问题,返回值为1才可以进行后续操作。

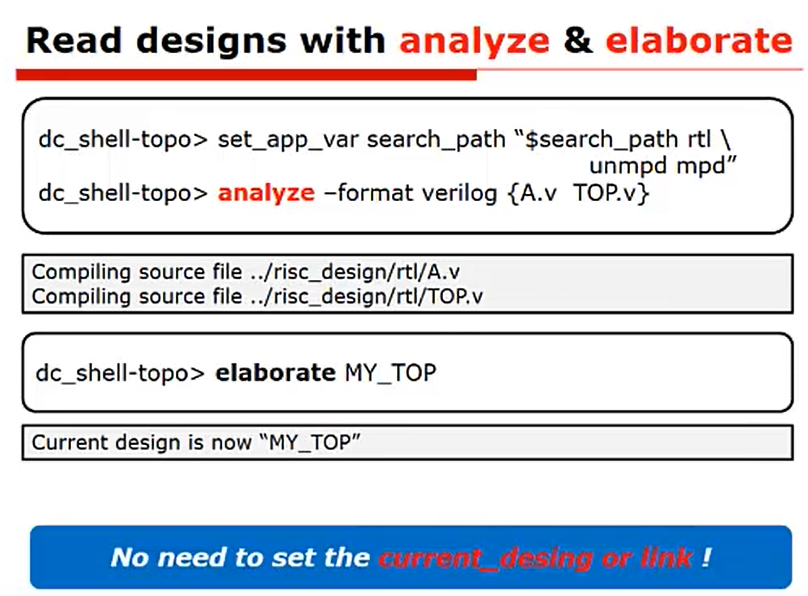

- analyze也可以load .v文件。

- -format sverilog可以加载systemverilog,但是DC仅可以综合sv的部分语法比如结构体,always_ff,always_comb等等

- elaborate可以指定顶层

- 使用这种方式读取.v不需要link

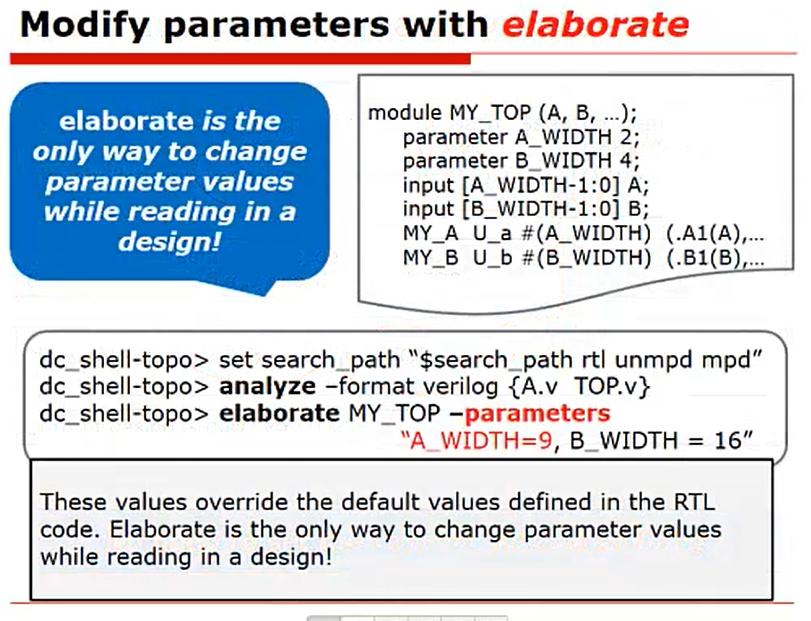

- elaborate还可以进一步地修改设计中的参数!

- DC翻译我们的.v文件也需要时间,因此可以在映射到GTECH库之后就保存一次ddc

- 综合完毕后也保存一般ddc,后端使用,只有Synopsys能识别。其他工具使用.v文件和.sdf文件进行后续流程

最后

以上就是舒服月光最近收集整理的关于DC入门(二)综合脚本1. 综合脚本的全部内容,更多相关DC入门(二)综合脚本1.内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复