在综合阶段,或者是preCTS之前,在sdc约束中往往会存在set_clock_transition。也常常会听到所谓的ideal clock,本章节比较详细的讨论相关transition相关内容。

1. Input transition

关于input transition取自

由于前面章节介绍可以知道,对于一个cell的delay计算,取决于这个cell的input trans和output load,那么对于直连端口处的cell,比如input 端口处的cell,它的input端是个port,那它的input trans如何定义呢?对于output口处的cell,它的load是个port,那这个port的外部负载是多大呢?应该怎么表示呢?这就涉及到本小节内容:

对于input:

可以通过set_drive/set_drive_cell/set_input_transition的方式对端口处的input slew进行设置

● set_drive : 表示端口处的驱动能力,默认没有设置的时候,认为端口处的驱动能力无限强,slew为0。

set_drive 1 [all_inputs] 表示所有的输入端口电阻为1,当电阻为0时候表示驱动能力无限强

● set_drive_cell : 用具体的cell来代替port口的外部逻辑驱动。具体的驱动能力由该cell的真实的lib值决定。

set_driving_cell -lib_cell INV3 -library slow [get_ports INPB]

● set_input_trans : 直接用trans值来表示驱动能力,在芯片设计中,也常常用这种方法。

set_input_transition 0.85 [get_ports PAD1]

————————————————

因此可以看到,input transition主要用于端口的输入trans,而这个input trans会影响到后面一级cell的delay值,在STA阶段,是可以看到的。

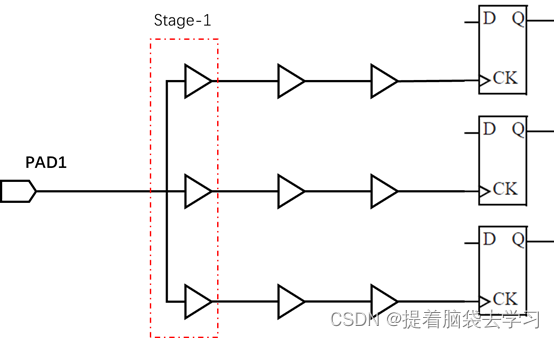

如下图所示,假如我们有如下设定,那么图中第一级的三个buffer的输入均为0.85

create_clock -name CLK1 –period 10 [get_ports PAD1]

set_input_transition 0.85 [get_ports PAD1]

2. Clock transition

依然参考上面所示图形状,如果我们有如下设定

set_clock_transition –rise –max 1.5 [get_clocks CLK1]

set_clock_transition –rise –min 1.5 [get_clocks CLK1]

set_clock_transition –fall –max 1.5 [get_clocks CLK1]

set_clock_transition –fall –max 1.5 [get_clocks CLK1]

可以看到对CLK1可以分别设置4中类型的transition。那么这个transitioin就会在整个clock network上面传递,上图中不止stage-1中的buffer的input trans是1.5,就连后面reg的CK的input transition也是1.5。

为什么要设置这个clock transition,主要是为了CTS前的timing check。因为在CTS之前,所有的clock 是ideal的,所以相关的clock tree的trans其实都是假的。直接用clock trans显然更加方便一些,因为在CTS之前,其实是不用clock propagate的,这个时候检查会很快,因为所有的clock tree都设定好了transition。

而在CTS之后,每一个cell其实都有了真实的RC值,这个时候需要通过clock propagate的方式,对每一级的transition进行传递和计算。这个时候set_clock_transition会无效。相关命令如下所示。它会导致整个CLK1的network都按照propagated的方式进行delay和trans的计算。

set_propagated_clock [get_clcoks CLK1]

3. Max transition

关于max_transition,从字面意思很容易理解,其实就是最大transition,也就是我们对于design中所有的pin设定的一个最大的值,如果超过了这个值,那么可能得到的delay就不准确了。一般情况下,lib里都会有一个default的max_transition,描述默认的最大trans值。而针对每一个pin也会有专门的max trans值的描述。Max_transition的设定,对于lib来说,主要是因为我们的二维查找表的trans有一个最大最小值,如果超过了这个范围,通过外插法去获取delay值将会不准确。

default_max_transition : 1.33333

Pin (I1){

Direction : “input”;

Releated_group_pin : VCCK;

Releated_power_pin :VDDK

Max_transition : 1.3333;

…

}

Pin (CK){

Clock : “true” ;

Direction : “input”;

Releated_group_pin : VCCK;

Releated_power_pin :VDDK

Max_transition : 0.6222;

…

}

在STA中如果没有特殊的max_transition设定,那么会自动拿lib中的trans进行check,而如果有特殊的需求,可以专门进行设定:

set_max_transition 1.2 [current_design]

set_max_transition 0.5 [all_clocks ] –clock_path

最后

以上就是忧虑发卡最近收集整理的关于Constraints --- transition(clock transition、input transition、max transition)的全部内容,更多相关Constraints内容请搜索靠谱客的其他文章。

发表评论 取消回复