时钟树综合干货分享

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

在今天主题分享之前,发一个社区的招聘信息。吾爱 IC 社区正式对外招聘讲师 啦。想不想跟小编一起工作,想不想在业余时间赚点 money?想不想在这个平台上实现名利双收?优秀的讲师有机会成为我们的合作伙伴 ,将来副业收入会远高于主业收入 (即便你目前年薪百万)。

如果你擅长以下任何一个细分领域 (或掌握的比较好),并且喜欢做内容分享这块,欢迎就以下任何一个方向制作一只视频,并发送到小编的邮箱。这只视频仅用于讲师资格筛选,不做它用,并保证不公开讲师的任何信息。

通过筛选后我们可以洽谈合作事项。

小编邮箱:vlsidesign2021@163.com (微信:ic-backend2018)

-

逻辑综合

-

DFT

-

布局布线 APR

-

静态时序分析

-

物理验证(DRC,ERC & LVS 等)

-

IR Drop & EM

-

ESD

-

Perl,tcl

另外,太多小伙伴咨询社区 IC 训练营的事情,今天这里统一回复下。目前第二期 IC 训练营已经开展过半 了,中途不招生。如果感兴趣可以关注第三期 IC 训练营。

第一期很多 0 基础学员已经收到若干个口头 offer 了!祝贺他们!

吾爱 IC 社区第二期训练营报名开始啦!

吾爱 IC 训练营两周小结 (数字 IC 后端实现)

正在准备校招的同学,可以好好看看下面这个 500 题。95% 校招笔试面试题都在这里面了,看完理论部分一定没问题。实践部分可以通过参加训练营的方式来提高实际项目的项目技能。

数字 IC 后端笔试 500 题出炉!(附答案)

下面进入今天的主题。分享下时钟树综合相关的主题。

开篇问题: 我们能否不做 clock tree synthesis,而是把 clock 信号直接当做 signal 来绕线?

CTS 前应该做哪些检查?

-

此时应该做完标准单元的摆放,而且确保标准单元是 legal 的。

-

placement 的 congestion map 和 cell density map 比较合理

-

Timing 可以接受

什么是 clock skew?

skew 是指任意两个寄存器时钟到达时间的差值。以下图为例,寄存器 A 和寄存器 B 的 latency 差值就是这两个寄存器的 skew。如果这个 skew 越小,我们就说这两个寄存器做的比较 balance,反之则说 clock tree 不 balance。

clock skew 产生的几大原因

-

Wire interconnect length

-

Capacitive loading mismatch

-

Material imperfections

-

Temperature variations

-

Differences in input capacitance on the clock inputs

那什么是 global skew 和 local skew 呢?

所有寄存器或 sink 之间的 clock latency 差值的最大值即为 global skew。因此如果两个寄存器之间没有 timing path(即不打交道),那么这个 skew 其实我们也不太关心。

所有有 timing path 的所有寄存器中任意两个寄存器或 sink 的 clock latency 差值即为 local skew。显然从 timing 的角度,我们是希望这个 local skew 越小越好。

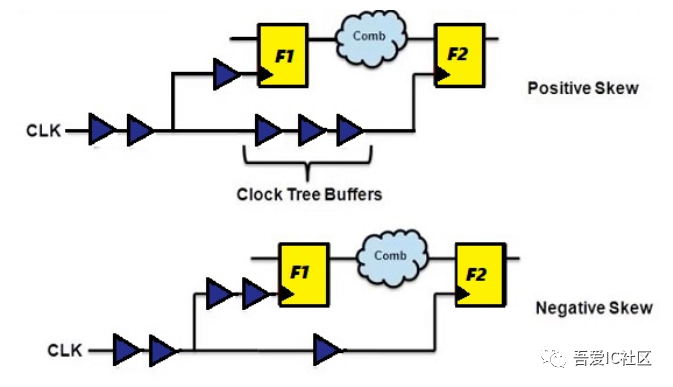

postive skew

当 capture clock 比 launch clock 来的晚或者说 capture clock 长度大于 launch clock 长度时,我们称这个 clock skew 是 postive skew。如下图所示。反之则为 negative skew。

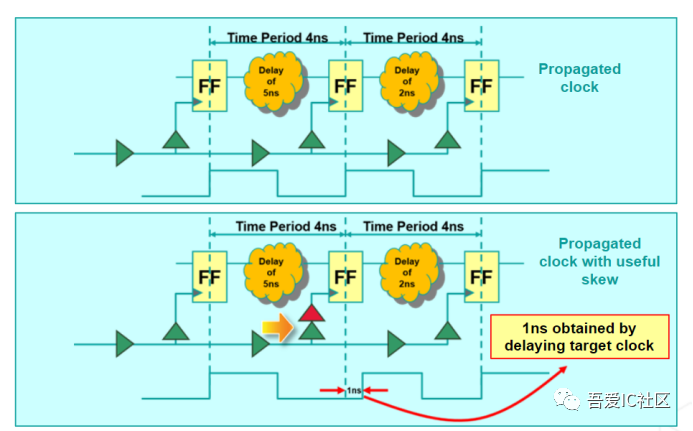

Useful skew

以下图电路为例,如果第一级 FF1/Q 到第二级 FF2/D 的 timing path 上存在 setup violation,那么我们可以把 FF2 的 clock tree latency 人为垫长(或告诉工具 FF2 的 tree 需要做的更长点)来解决这个 setup violation。这种做法的前提是第二级到第三级的 timing path 有足够的 timing margin。

这种就是利用 clock skew 即把 FF1 和 FF2 的 skew 做的更大点来实现的。此时因为这个 skew 是对 timing 是有利的,所以我们称之为 useful skew。

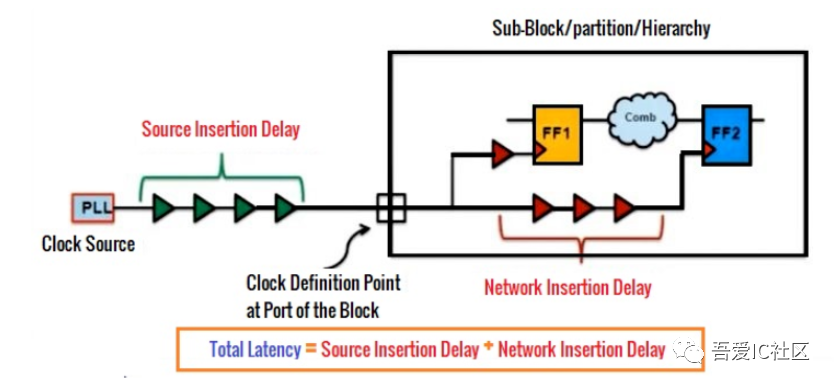

Clock Tree Latency (Insertion Delay)

对于 block 来说,以这次训练营的项目 Cortexa7core 为例,这里的 Clock Definition Point 就是 block 的时钟定义 port。从整芯片来看,这个时钟是芯片中的 PLL 进行倍频再做分频后才到达芯片子功能模块的。

数字 IC 后端时钟树综合专题(OCC 电路案例分享)

ARM Cortex-A7 时钟树综合实战分析

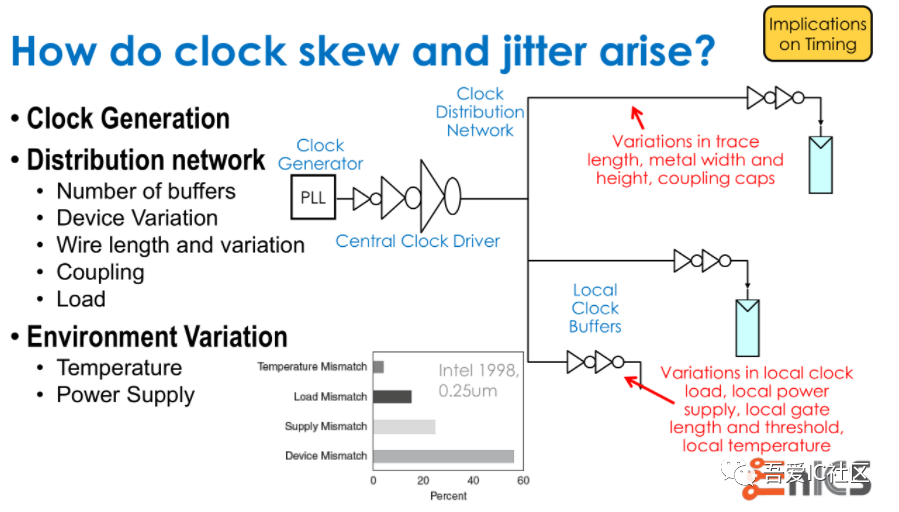

Clock Skew 和 Jitter 产生的原因

clock skew 主要是因为时钟 root 点到每个 sink 的距离不一致而导致它们的 clock tree latency 不一致。

-

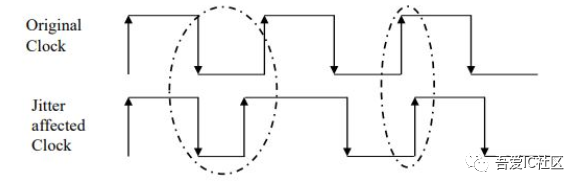

Jitter is the short-term variations of a signal with respect to its ideal position in time

-

The two major components of Jitter are random Jitter and deterministic Jitter

-

Factors causing Jitter includes imperfections in Clock oscillator, supply voltage variations, Temperature variations, Crosstalk

一个时钟信号如果要走很长的路才到它要去的地方,是很容易有 jitter 的。jitter 的产生及分析可以说是非常复杂的。有兴趣深入研究的同学可以下载几份 paper 来研读下。

CTS 前应该设置好哪些东西?

-

设置好 size only 和 dont touch

-

设置好 target clock tree latency 和 target clock skew

-

设置好长 tree 用的 clock inverter list

-

设置好 clock gating 的 list

-

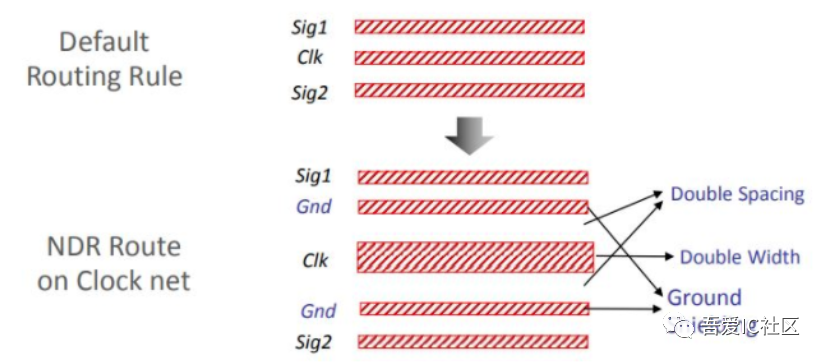

设置好 CTS NDR(Non-Default Rule)

-

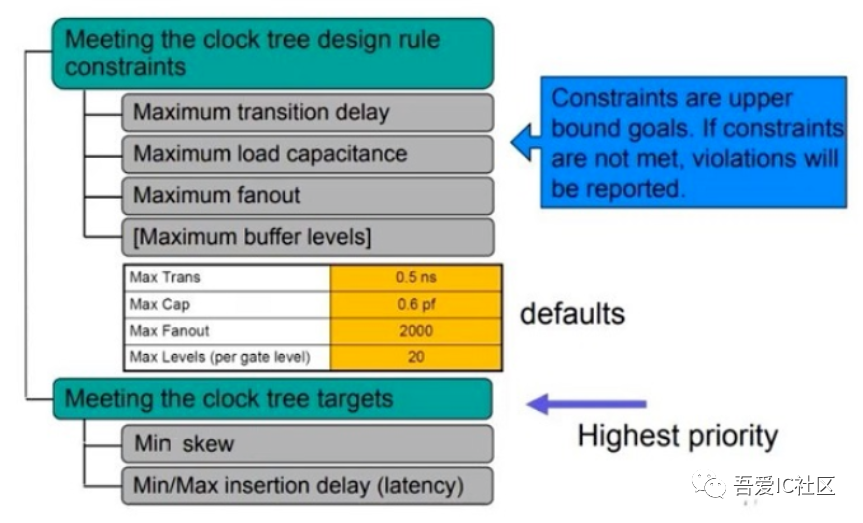

设置好 clock transition,clock max fanout 等约束

-

设置好 clock net rouing 的 layer(使用中高层绕线)

-

设置好 clock exception(比如 floating pin ,ignore pin ,exclude pin)

设置 NDR 的好处

-

改善 crosstalk,确保时钟质量

-

改善 EM

-

减少 clock tree latency

Clock Tree Exceptions

这里涉及长时钟树经常要用到的几种概念,特别是下面几种 pin,必须理解掌握。

-

Non-Stop pin

-

Exclude pin

-

Float pin

-

Stop pin

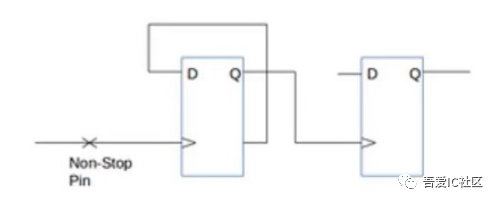

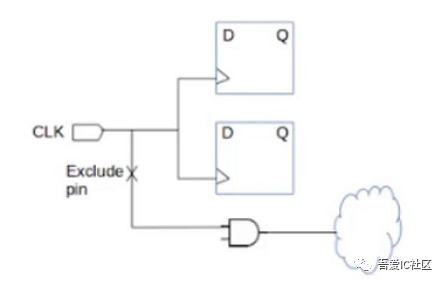

Non-stop pin

Non-stop pin 其实就是它的字面意思,即不是时钟的终点。上图中的例子前面那颗寄存器的输出产生一个分频时钟,这颗寄存器的 CK 默认就是 non-stop pin,后面那颗寄存器就是传统的 sink 点,即时钟树的一个终点。

常见的 non-stop pin 有以下几种类型

-

分频时钟寄存器的 CK

-

Clock Gating 的 CK

Exclude pin

Exclude pin 说的直白点就是它不是时钟的一部分,即不是真实的时钟信号,如上图中的 Exclude pin 所示的那个点。

常见的 exclude pin 有以下这些类型

-

Non clock input pin of sequential cell

-

Mux 的选择端 S

-

三态门的使能端

-

output port (这种默认就是 exclude pin)

这类 pin 工具不会去做 balance,只修分支上的 drv,即 max transition,max fanout 等。

而且工具为了把 exclude pin 后面的与正常的 clock tree 区分开来,会在 exclude pin 前额外插一颗 clock buffer 来隔开。

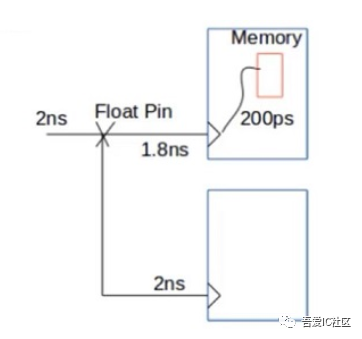

Float pin

什么时候要设置 floating pin 呢?工具默认是会把同一个 clock 下带的 sink 做平。如果一个设计如上图所示,一个时钟 root 既有到寄存器的,也有到 Memory 的,而且 memory 内部有 200ps 的 tree(这里的 memory 也可以理解成为一个子模块),那么我们就得告诉工具时钟从 root 长到 Memory 的 CK 要比其他寄存器做短 200ps,这样才能保证 flatten 后看到的实际 tree 的长度是差不多的。

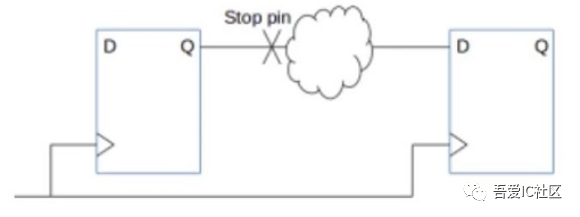

Stop pin

Stop pins 就是时钟树的终点。常见的有寄存器的 CK,memory 的 CK 以及 IP 的 CLK。

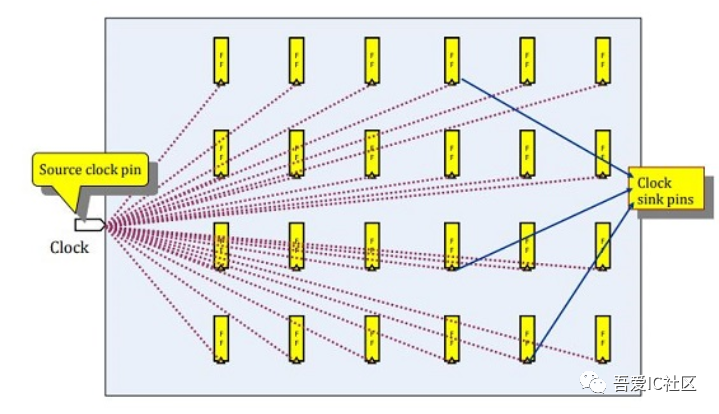

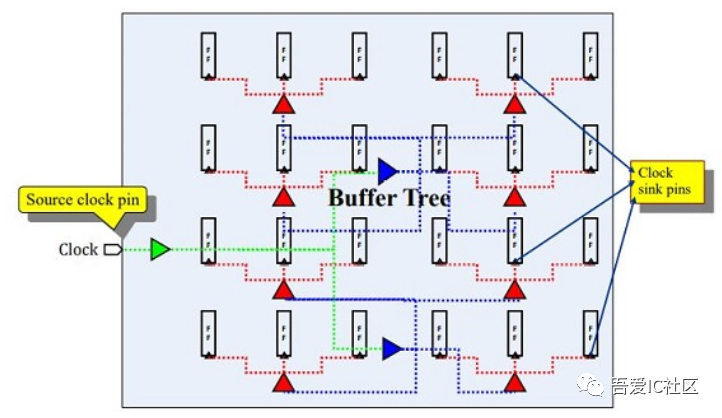

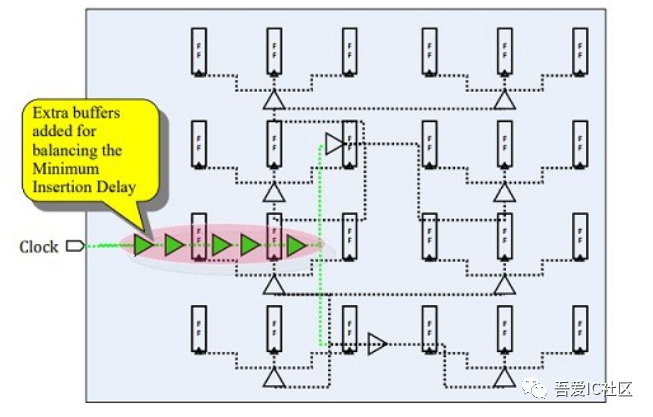

时钟树综合前后变化

- Before CTS all Clock Pins are driven by a single Clock Source

- After CTS the buffer tree is built to balance the loads and minimize the skew

- After CTS a “delay line” is added to meet the minimum Insertion Delay (ID)

CTS 的目标

时钟树综合的目标很明确。在实现 clock insertion delay 和 clock skew 最小化的同时还得把 DRV 控制在一个合理范围内。

时钟树质量分析

- 报告 clock tree latency 长度和 clock skew

这个从 log 可以从 log 获取,也可以报出来看看。还不懂如何看 log 的请查阅之前的主题分享。

- 检查时钟树是否合理

利用之前分享的高亮时钟 path 的方法来查看是否有 “兜圈” 的情况。

也可以用 report_clock_tree_structure 或 report_ccopt_clock_tree_structure 来报出时钟树的信息。

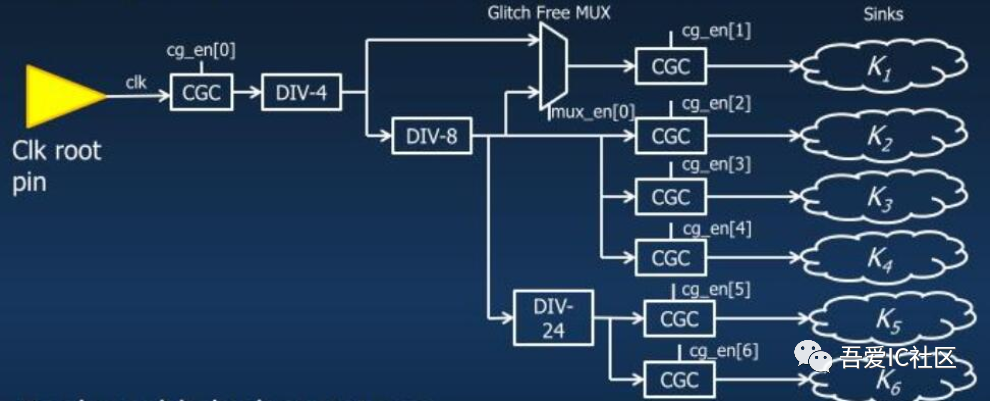

【思考题】 下图为一个常见的时钟结构图,图中 CGC 代表 clock gating,DIV*代表分频器。长时钟树前在各个分频器的输出端都定义了 generated_clock。且 K1 与其他 sink 都有交互,即有 timing path。

1)对于这样的时钟结构,我们应该如何做时钟树?

2)如果在 Glitch Free Mux 电路中的 mux 的一端设置 floating pin,请问这种做法是否正确?这种做法有何利弊?

3)能否在每个 CGC 后面分别定义一个时钟?为什么?如果这样做,要如何确保各路 CGC 输出到 sink 点是等长的?如果不等长,会有什么问题?

好了,今天的内容分享就到这里。另外,因为公众号更改推送规则,小编分享的每篇干货不一定能及时推送给各位。为了避免错过精彩内容,请关注星标公众号,点击 “在看”,点赞并分享到朋友圈,让推送算法知道你是社区的老铁,这样就不会错过任何精彩内容了。

如果你想和小编有更进一步的沟通交流的机会,欢迎加入小编知识星球,让我们一起学习成长,共同进步。相信在这里能让你成就一个更完美的自己 。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 *** *):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

定期将项目中碰到的问题以案例的形式做技术分享

-

基于 90nm 项目案例实现教程(ICC 和 Innovus 配套教程)

-

数字 IC 行业百科全书

吾爱 IC 社区 知识星球星主为公众号” 吾爱 IC 社区” 号主,从事数字 ic 后端设计实现工作近十年,拥有55nm,40nm,28nm,22nm,14nm 等先进工艺节点成功流片经验,成功tapeout 过三十多颗芯片 。

这里是一个数字 IC 设计实现高度垂直细分领域的知识社群,是数字 IC 设计实现领域中最大,最高端的知识交流和分享的社区,这里聚集了无数数字 ic 前端设计,后端实现,模拟 layout 工程师们。

在这里大家可以多建立连接,多交流,多拓展人脉圈,甚至可以组织线下活动。在这里你可以就数字 ic 后端设计实现领域的相关问题进行提问,也可以就职业发展规划问题进行咨询,也可以把困扰你的问题拿出来一起讨论交流。对于提问的问题尽量做到有问必答,如遇到不懂的,也会通过查阅资料或者请教专家来解答问题。在这里鼓励大家积极发表主题,提问,从而促进整个知识社群的良性循环。每个月小编会针对活跃用户进行打赏。

最重要的是在这里,能够借助这个知识社群,短期内实现年薪百万的梦想!不管你信不信,反正已经进来的朋友肯定是相信的!相遇是一种缘分,相识更是一种难能可贵的情分!如若有缘你我一定会相遇相识!知识星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有1084 位星球成员,感谢这 1084位 童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标 。

欢迎关注 “吾爱 IC 社区 ”

微信号:ic-backend2018

https://mp.weixin.qq.com/s/HryO1XxSBcAdoLoi5pUMTw

最后

以上就是文静诺言最近收集整理的关于时钟树综合知识分享时钟树综合干货分享的全部内容,更多相关时钟树综合知识分享时钟树综合干货分享内容请搜索靠谱客的其他文章。

发表评论 取消回复