今天主要来探讨一下时钟之间的三个关系:logically exclusive、physically exclusive 以及-asynchronous。

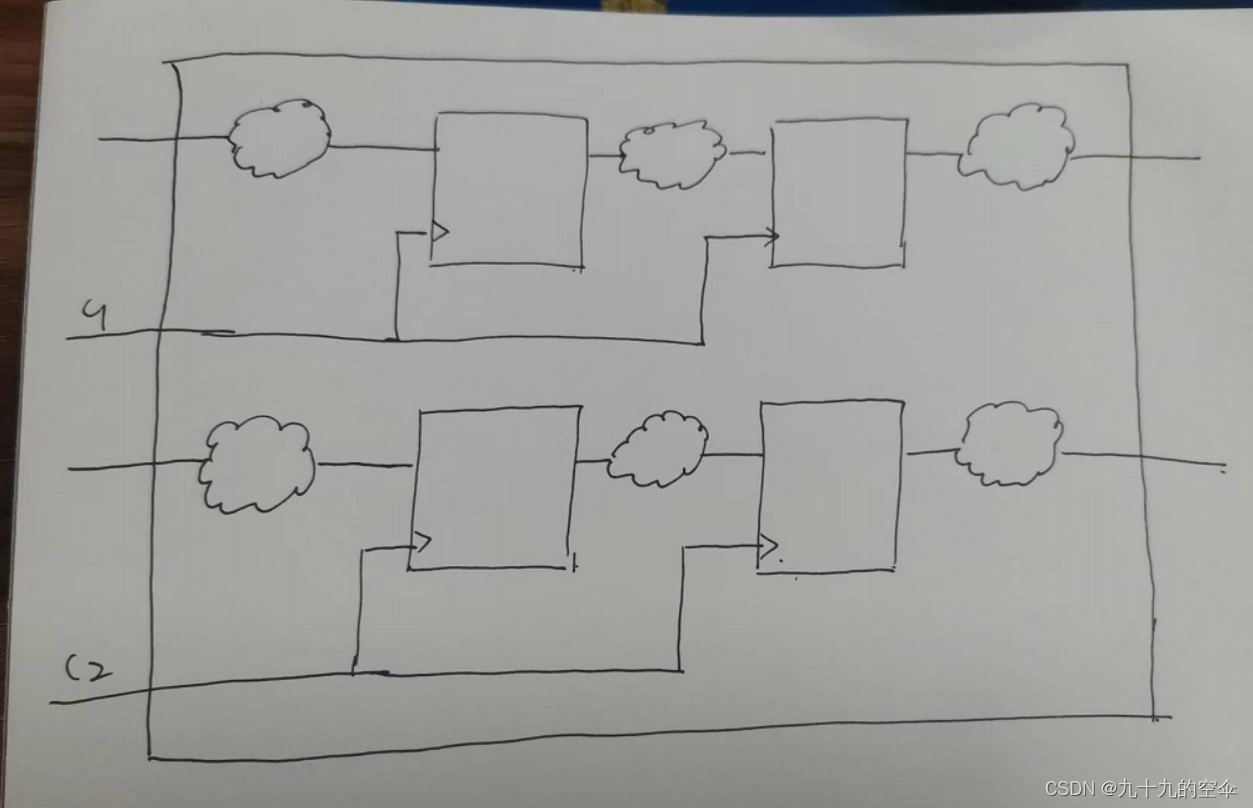

1.如果两个时钟C1和C2是logically exclusive的,这意味着这两个时钟共存于设计中,但是彼此之间没有任何交流。”共存在设计中“的意思是某一时刻这两个时钟信号都是存在的;”彼此之间没有任何交流“的意思是:不存在任何时序路径,其起点是由C1驱动的,而其终点是由C2驱动的,也不存在任何路径,其起点是由C2驱动的,而其终点是由C1驱动的。

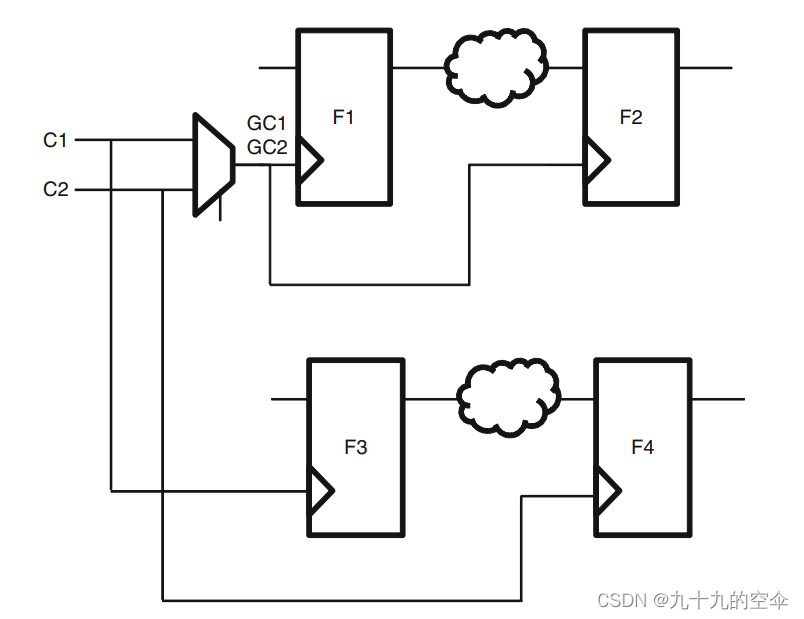

如上图所示C1和C2是典型的logically exclusive,他们共存于设计中,而且时钟信号同时都有,但他们没有任何交互。

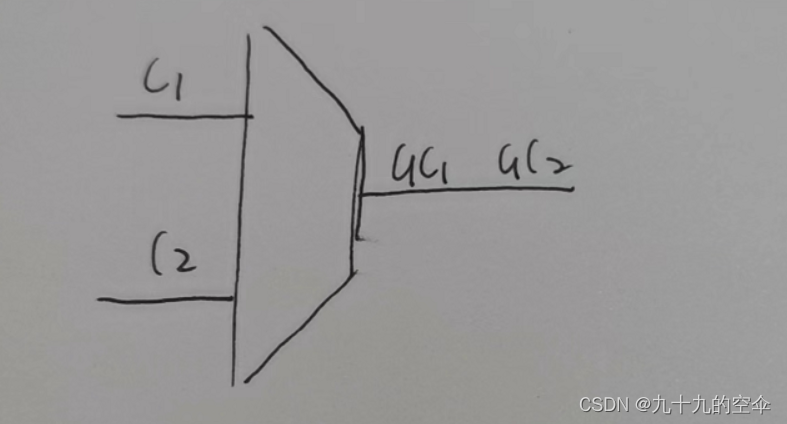

2.如果两个时钟C1和C2是physically exclusive的,那说明这两个时钟信号是不能共存于整个设计中的,最典型的例子就是两个时钟信号通过一个MUX输出。

如图,MUX的输出Z可能一会是C1的时钟信号,一会是C2的时钟信号,但无论如何,Z端的输出不可能同时是C1和C2,因此在Z端所定义的两个生成时钟GC1和GC2是physically exclusive的。

3.asynchronous

如果两个时钟是异步的,那么就定义为asynchronous,”异步“是指时钟之间没有固定的相位关系。

其次,就共同点而言,这三种关系都会让时序分析工具停止对相关时序路径的分析,因此都会忽略掉相关的时序违例,仅就这个角度看,无论是logically exclusive、physically exclusive还是asynchronous,其效果都是一样的。

但是这三种关系仍然有区别,除了上文123所述的本质区别外,logically exclusive、physically exclusive和asynchronous在对cross talk的处理上是不一样的,但仅就我个人经验而看,cross talk不是不是前端开发人员该考虑的问题,故不深入讨论,有兴趣的朋友可以去看本文最下方给出的参考文献。

下面给出几种典型电路以及正确的时钟定义。

a) 对于logically exclusive的处理:

如果上图C1和C2是logically 的,那么推荐的约束命令如下:

图中C1端口经过走线到达MUX的输入端A,之所以要在A处定义生成时钟,是为了使约束命令向后兼容代码。如下图所示,如果在后续版本的代码中,C1时钟和C2时钟的logically exclusive关系消失。而同时我们一开始就定义C1和C2是logically exclusive的,那么此时就会错误地省去某些时序路径的时序分析从而埋下隐患。

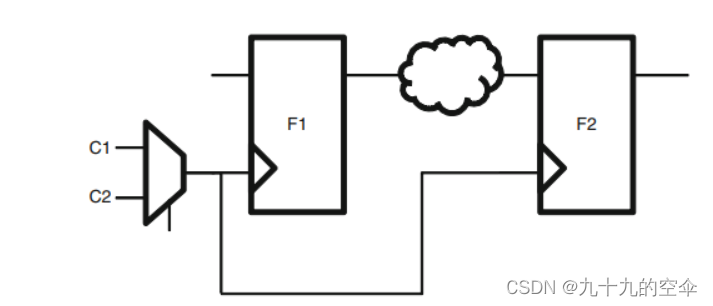

b)physically exclusive

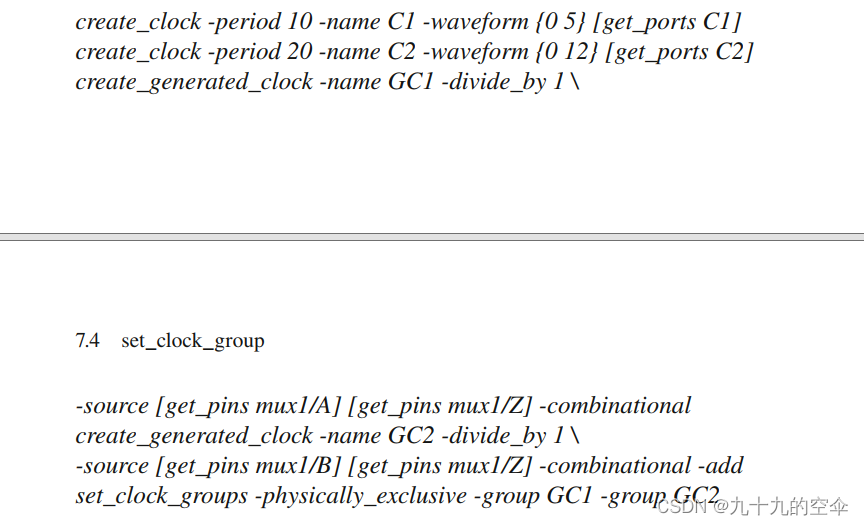

对于上图所示的 GC1和GC2,他们是physically exclusive的。对于GC1和GC2的正确处理如下

这里GC1和GC2由于其source object都是 mux1/Z,即他们的物理位置是一样的,因此要在最后加入-add,否则后面的命令将覆盖前面的命令,导致只有GC2被定义。而-combinational 的意思是生成时钟的源-source所指定的位置到生成时钟的source object之间是纯组合逻辑。(mux1/A到mux1/Z之间是纯组合逻辑)。

所以捏,综合上述a)b)两点,对于如上图所示电路我们的约束应该为:

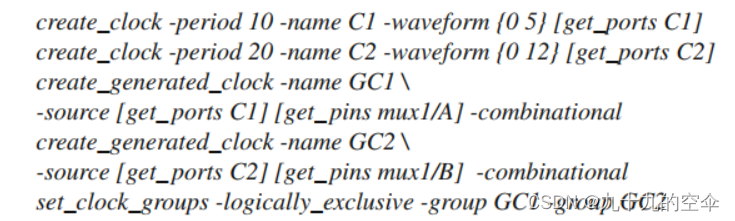

create_clock -period 10 -name C1 [get_ports C1]

create_clock -period 20 -name C2 [get_ports C2]

create_generated_clock -name GC1 -source [get_ports C1] [get_pins mux1/A] -combinational

create_generated_clock -name GC2 -source [get_ports C2] [get_pins mux1/B] -combinational

set_clock_groups -logically_exclusive -group GC1 -group GC2

create_generated_clock -name muxGC1 -source [get_pins mux1/A] -divide_by 1

[get_pins mux1/Z] -combinational

create_generated_clock -name muxGC2 -source [get_pins mux1/B] -divide_by 1

[get_pins mux1/Z] -combinational -add

set_clock_groups -physically_exclusive -group muxGC1 -group muxGC2

最后

以上就是幽默月亮最近收集整理的关于STA:logically exclusive与physically exclusive的全部内容,更多相关STA:logically内容请搜索靠谱客的其他文章。

发表评论 取消回复