一、介绍

1>综合工具是Synopsys公司的Design Compiler

2>DC功能是把RTL级的代码转化为门级网表

3>综合包括转译(Translation)、优化(Optimization)、映射(Mapping)三个过程。

在转译过程中,软件自动将源代码翻译成每条语句所对应的功能模块以及模块之间的拓扑结构,这一过程是在综合器内部生成电路的布尔函数的表达,不做任何的逻辑重组和优化。

在优化过程中,基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对转译结果作逻辑优化和重组。

在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库中搜索符合条件的单元来构成实际电路。如果在综合时,链接了厂家的库文件,则门级电路使用的器件是厂家库文件中提供的器件。

二、相关知识

1.set_dont_touch

在当前设计中的单元格、网、引用和设计以及库单元格上设置dont_touch属性,以防止在优化过程中修改或替换这些对象

使得DC在综合的时候不会给时钟网络加入BUFFER以满足skew的要求:set_dont_touch_network [get_clocks clk]

2.compile_ultra

对当前的设计进行高质量的编译,以获得更高质量的结果

3.create_colck

定义时钟周期和时钟源(port或pin)、时钟的占空比、时钟名等,create_colck –period 10 [get_port clk]

4.设定时钟的uncertainty、latency和transition,其中uncertainty是用来模拟时钟的skew和jitter,latency设定时钟的延迟,transition设定时钟的转换时间。

5.source latency

实际的时钟源到时钟定义点的传播延迟,而network latency是指设计内部从时钟定义点到触发器时钟端的延迟。

6.set_clock_uncertainty

定义时钟扭斜信息,时钟的抖动(jitter)可扭斜(skew)组成:set_clock_uncertainty 0.6 [get_clocks CLK]

7.set_clock_transition

定义时钟的转换时间,set_clock_transition 0.45 [get_clocks CLK]

8.create_generated_clock

创建产生的时钟,如时钟经过分频后的时钟,指定源时钟的名字和端口,分频数(倍频数),生成时钟的端口:create_generated_clock –source clk2x –divied_by2 [get_pins clk]

9.set_disable_timing

是用来设置 timing arc,表示打断这条时序弧,不去计算这段时序弧的 delay,并且所有经过这段时序弧的 path 都会被打断(要慎用)。

10.set_input_delay

相对于时钟的信号输入的到达时间,它用在输入端口,指定在时钟沿后数据稳定所需的时间。

11.set_output_delay

在输出端口定义在时钟边沿来到之前数据有效所需时间。

12.set_false_path

设定路径使得DC不对其进行时序分析。

13.set_max_delay和set_min_delay

设定setup和hold约束的最大/最小延迟。

14.set_muticycle_path

设定多周期路径。

15.set_disable_timing

是用来设置 timing arc,表示打断这条时序弧,不去计算这段时序弧的 delay,并且所有经过这段时序弧的 path 都会被打断(要慎用)。

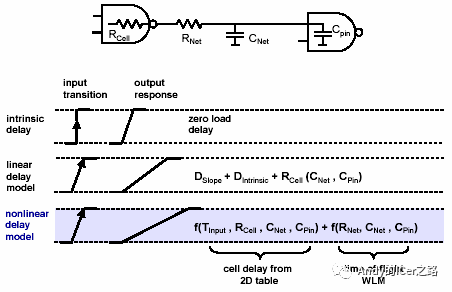

16.单元延时

线性模型由三部分组成:Dslope表示单元输入信号的延时、Dintrinsic表示单元的固有延时、Rcell(Cnet,Cpin)表示输出的管脚电容和连线电容对单元的附加延时。

非线性模型是DC计算单元延时的主要模型。它分为两部分:单元的输入延时(transition time)和输出负载的函数。线性模型不同的是,它是通过查找表的方式得到的。

三、重点

1.工具使用版本是否正确

2.确定单位---由lib库决定

3.模拟的A2A信号、PG、数字部分直接调用STD的需要设置set_dont_touch

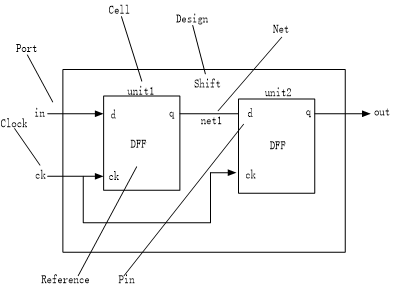

4.约束对象

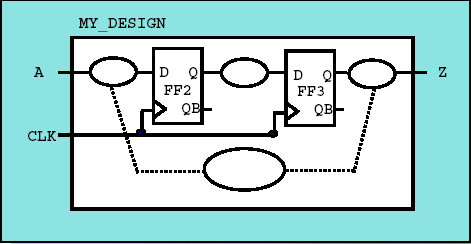

5.时序分析path

其中共有4条path,分别为:

1>输入端口A -> FF2的D端;

2>FF2的CK端-> FF3的D端;

3>FF3的CK端-> 输出端口Z;

4>输入端口A -> 输出端口Z。

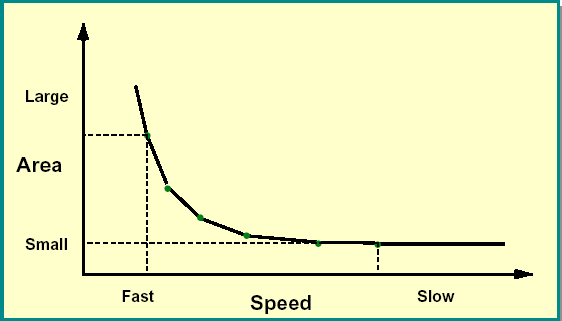

6.综合的速度和面积的关系

7.DCT

extraction=topographical

DCT是指带物理拓扑信息的综合。T就是英文拓扑的首字母。

相对于用wire_load模型估算的综合,DCT出的结果会比较接近后端place之后看的到。

----综合的结果会相对来说更好

8.加上以下设定后:

set auto_insert_level_shifters_on_clocks all

clock net上低功耗CELL可以正常插入了。

参考资料: https://mp.weixin.qq.com/s/EJkbtq5IxL054EdDFoAtzA

最后

以上就是受伤酒窝最近收集整理的关于MCU学习笔记_DC的全部内容,更多相关MCU学习笔记_DC内容请搜索靠谱客的其他文章。

发表评论 取消回复