set_clock_transition和set_input_transition的主要区别是:

1.set_clock_transition所指定的transition value会apply到整个clock network上,而不是在不同的点重新去计算.

2.set_input_transition只会作用于指定的port,对于这个port的logic cone上的其他点,transition value会根据前一级进行计算。

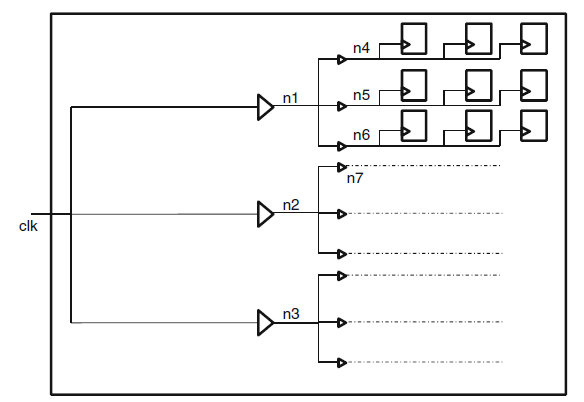

以下图为例,如果是使用set_clock_transition在clk port指定transition time,那么所有的clk network point都会使用同样的transition time(包括flop的CLK pin),如n1/n2/n2/n4/n5/n6…

如果使用set_input_transition在clk port指定transition time,那么在每个clk network point都会重新计算transition time,包括flop的CLK pin。

一个建议是:

在CTS前,因为clk的负载很多,去计算transition time的话会非常差,而且没有实际的clk tree结构,这样的计算并没有意义,所以使用set_clock_transition;

在CTS后,有了实际的clk tree结构,使用set_input_transition,在每个clk network point计算实际的transition time。

文章首发于个人微信公众号:IC小白

欢迎关注~

最后

以上就是潇洒樱桃最近收集整理的关于SDC设计约束——set_input_transition和set_clock_transition的区别的全部内容,更多相关SDC设计约束——set_input_transition和set_clock_transition内容请搜索靠谱客的其他文章。

![静态时序分析简明教程(四)]时钟常规约束](https://www.shuijiaxian.com/files_image/reation/bcimg27.png)

发表评论 取消回复