绪论

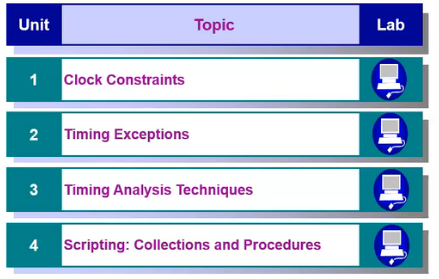

目录:

第一到第四课比较重要

第一课

STA原理

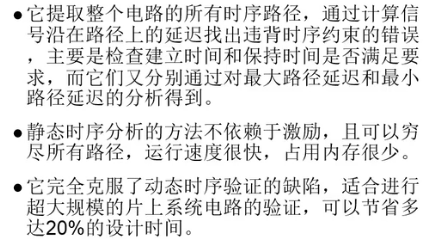

静态时序分析是一种穷尽分析方法,用以衡量电路性能。

-

STA主要有三个步骤:

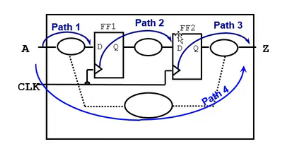

1.设计被分解为时序路径(timing path)

2.计算所有路径的延时(delay)

3.检查路径的延时是否能满足约束条件 -

第一步: 四种路径:

1.输入端口到ff输入口

2.ff的时钟端口到ff输入口

3.ff的时钟端口到输出端口

4.输入端口到输出端口

-

第二步:两种计算

1.post-layout:从版图的寄生参数中算出,可以通过sdf文件直接导入到pt当中

2.pre-layout:从technology library当中查表算出,模型并不完全准确 -

第三步:约束

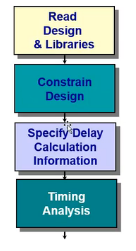

STA流程

- 第一步:Read design & libraries

读入.db文件,verilog网表,读入vhdl文件,读入库,分别对应以下命令:

read_db

read_verilog

read_vhdl,read_edif

lappend link_path Your_tech_lib.db

- 第二步:Constrain design

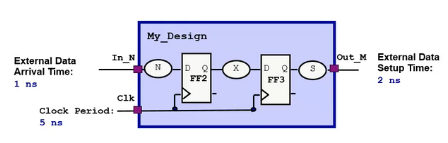

根据上图写出的约束如下所示:

create_clock -period 5 [get_ports CLK]

set_input_delay 1 -max -clock Clk [get_ports In_N]

set_output_delay 2 -max -clock Clk [get_ports Out_M]

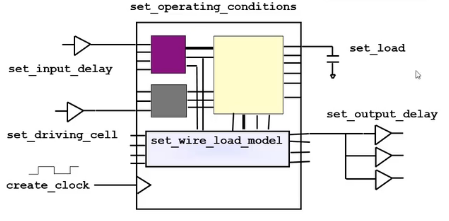

其它约束:

- 第三步:specify delay calculation information

读入已有版图的网表延迟,读入已有版图的寄生参数,对应以下命令:

read_sdf

read_parasitics

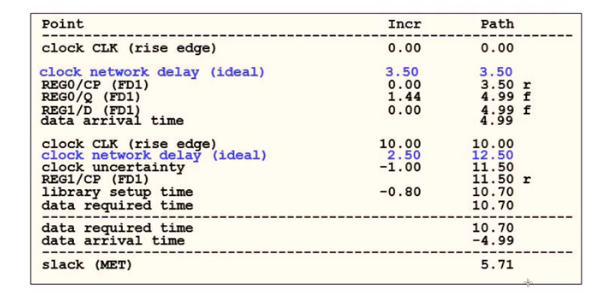

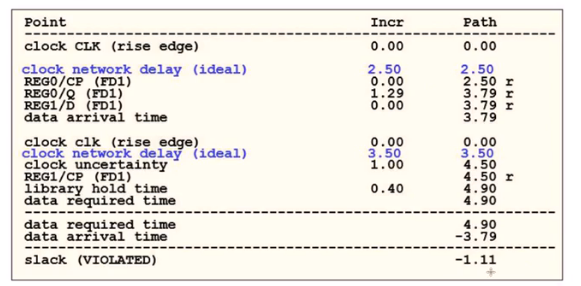

Timing reports

报告中的path type是max就是setup check,是min就是hold check。

第二课

Pre-layout constraint

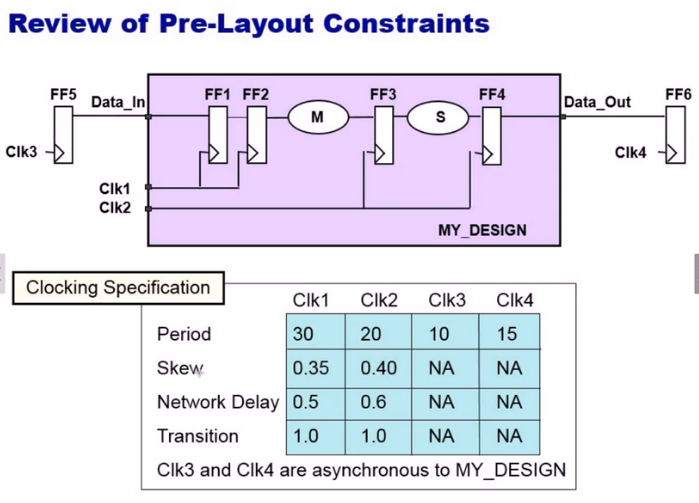

以下面电路作为例子:

设置的约束如下所示:

create_clock -period 30 [get_ports Clk1]

create_clock -period 20 [get_ports Clk2]

create_clock -period 10 -name Clk3

create_clock -period 15 -name Clk4 #Clk3和Clk4在模块外,因此要额外注明

set_clock_uncertainty 0.35 [get_clocks Clk1]

set_clock_uncertainty 0.4 [get_clocks Clk2]

set_clock_transition 1.0 [get_clocks "Clk1 Clk2"]

set_clock_latency 0.5 [get_clocks Clk1]

set_clock_latency 0.6 [get_clocks Clk2]

set_input_delay 0.0 -clock Clk3 [get_ports Data_In]

set_output_delay 0.0 -clock Clk4 [get_ports Data_Out] #疑问,如果延迟为0为什么要设置约束?

set_false_path -from [get_clocks Clk3] -to [get_clocks Clk1]

set_false_path -from [get_clocks Clk2] -to [get_clocks Clk4]

uncertainty约束包括skwe,jitter和毛刺,在pre-layout可以不考虑毛刺或者部分约束。

-

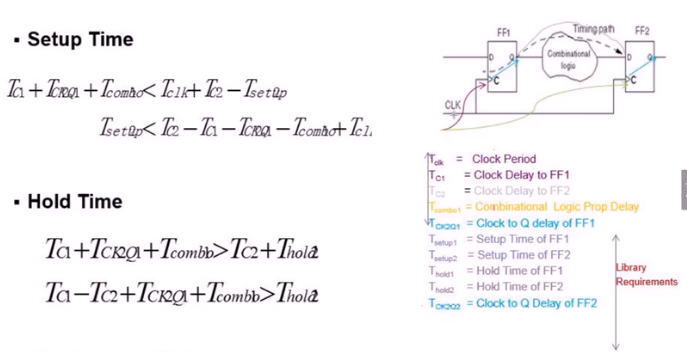

setup/hold的计算方法

由于Clk1和Clk2周期不同,在计算setup/hold time时所取的边沿也要进行调整。 -

如何检查时钟约束的添加情况?

report_clock -attributes -skew #根据约束的属性列出

check_timing

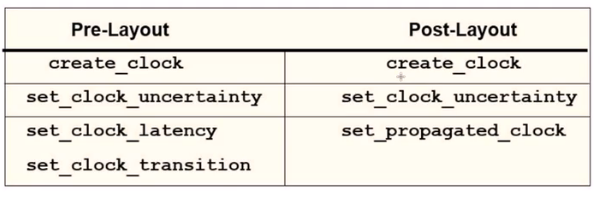

Post-layout constraint

时钟延时的设置变化为下面的命令:

set_propagated_clock

#具体示例如下:

read_sdf top.sdf

set_propagated_clock [all_clocks]

report_timing -path full_clock #clk到reg之间的延时也会被列出来

- pre-layout vs post-layout

Clock Source Latency

电路的延时除了network latency以外还有source latency,设置的命令如下:

#set_clock_latency 0.54 [get_clocks CLK] Pre-layout

set_propagated_clock [all_clocks] #Post-layout

set_input_delay -source_latency_included -max 1.4 #Post-layout

Q:要如何设置比较准确的source latency?

A:使用-early和-late选项

set_clock_latency 2.5 -source -early [get_clocks CLK]

set_clock_latency 3.5 -source -late [get_clocks CLK]

setup time的检查中,最大延时算入信号路径,最小延时算入时钟路径。

holdtime的检查中,最大延时算入时钟路径,最小延时算入信号路径

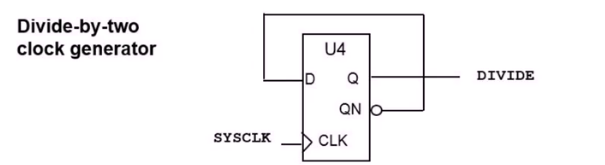

Generated Clocks

对于在电路内部生成的时钟也要额外的命令去设置,才能让PT识别:

create_clock -per 10 [get_ports SYSCLK]

create_generated_clock -name DIVIDE

-source [get_pins U4/CLK] -divide_by 2 [get_pins U4/Q]

Keep Clocks “Clean”

- minimum pulse width

PT可以检查FF上的最小时钟宽度是否满足要求,当时钟树定义完毕并在计算完时钟路径的延时后,执行对最小时钟宽度的检查。

set_min_pulse_width -high 1.5 [all_clocks]

set_min_pulse_width -low 1.0 [all_clocks]

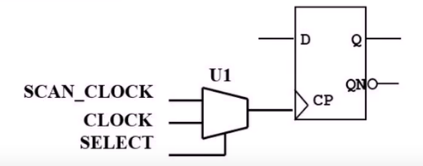

- gating clock

为了防止gating clock出现毛刺,可以利用约束检查gating信号相对于时钟信号的setup和hold time

设置后PT会根据电路的逻辑自动判断出门控时钟信号,但是在一些复杂的单元之中需要手动设置。

create_clock -period 10 [get_ports CLOCK]

set_clock_analysis 0 [get_ports SCAN_CLOCK]

set_clock_gating_check -high -setup 0.5 -hold 0.4 [get_cells U1]

report_clock_gating_check

***注意:约束通过后不产生毛刺的前提是已经规划好了gating信号到来的时间。

Post-layout Analysis

- OCV

on-chip variation,PT会根据芯片的PVT环境分析不同情况下的延时。

OCV分析需要有后端实现后的sdf文件

read_sdf -analysis_type on_chip_variation TOP.sdf

最后

以上就是唠叨绿草最近收集整理的关于PT静态时序分析 第一课 第二课的全部内容,更多相关PT静态时序分析内容请搜索靠谱客的其他文章。

发表评论 取消回复