实验1:

设计代码【design code】:

module MUX_8_to_1(

input [1:0] d0,d1,d2,d3,d4,d5,d6,d7,

input [2:0] select,

output reg[1:0] d_out

);

always@(*) // * 代表所有信号

begin

case(select) //利用case语句,后面需要default: d_out<=2'bz

3'b000: d_out<=d0;

3'b001: d_out<=d1;

3'b010: d_out<=d2;

3'b011: d_out<=d3;

3'b100: d_out<=d4;

3'b101: d_out<=d5;

3'b110: d_out<=d6;

3'b111: d_out<=d7;

default: d_out<=2'bz;

endcase

end

endmodule

仿真代码【testbench】:

module MUX_8_to_1_tb( );

reg [1:0] d[7:0];

reg [2:0] select;

wire [1:0] d_out;

integer i; //寄存器,可以变化

MUX_8_to_1 MUX_8_to_1_test( // 调用模块名 实例名

.d0(d[0]),

.d1(d[1]),

.d2(d[2]),

.d3(d[3]),

.d4(d[4]),

.d5(d[5]),

.d6(d[6]),

.d7(d[7]),

.select(select),

.d_out(d_out)

);

initial

begin

for(i=0;i<8;i=i+1)

begin

d[i]=0;

end

select = 3'bz;

#10;

for(i=0;i<8;i=i+1)

begin

select =i;

d[i] = #1 1;

d[i] = #2 2;

d[i] = #3 3;

#3;

#1;

end

$finish;

end

endmodule

实验2:

转载:关于generate用法的总结【Verilog】

设计代码【design code】:

module MUX_4_to_1(

input [1:0] d0,d1,d2,d3,d4,d5,d6,d7,

input [2:0] select,

output [1:0] d_out

);

wire [1:0] tmp[7:0]; //2位的8个元素的数组

wire [1:0] d [7:0];

assign d[0]=d0;

assign d[1]=d1;

assign d[2]=d2;

assign d[3]=d3;

assign d[4]=d4;

assign d[5]=d5;

assign d[6]=d6;

assign d[7]=d7;

genvar i;

generate

for(i=0;i<8;i=i+1)

begin

assign tmp[i]=(select==i)?d[i]:3'b0;//选择d[i],或默认000

end

endgenerate

assign d_out = tmp[0]+tmp[1]+tmp[2]+tmp[3]+tmp[4]+tmp[5]+tmp[6]+tmp[7];

endmodule

测试代码【testbench】

module MUX_4_to_1_test();

reg [1:0] d[7:0];

reg [2:0] select;

wire [1:0] d_out;

integer i;

MUX_4_to_1 MUX_4_to_1_test(

.d0(d[0]),

.d1(d[1]),

.d2(d[2]),

.d3(d[3]),

.d4(d[4]),

.d5(d[5]),

.d6(d[6]),

.d7(d[7]),

.select(select),

.d_out(d_out)

);

initial

begin

for(i=0;i<8;i=i+1)

begin

d[i]=0;

end

select = 3'bz;

#10;

for(i=0;i<8;i=i+1)

begin

select =i; //10 [0] 19-20[1] [d_out=d[1]=0]

d[i] = #1 1; //11-12[d[0]=1=d_out]

d[i] = #1 2; //12-15[d[0]=2=d_out]

d[i] = #3 3; //15-19[d[0]=3=d_out]

#3;

#1;

end

$finish;

end

endmodule

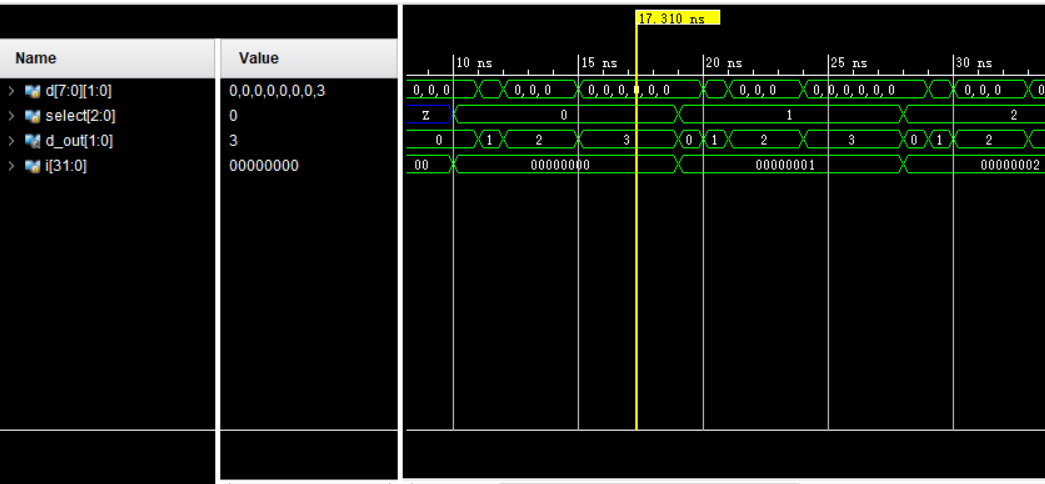

仿真结果图:

最后

以上就是整齐白猫最近收集整理的关于ASIC作业(1):任务1与任务2的全部内容,更多相关ASIC作业(1)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复