HDL (Hardware Description Language),硬件描述语言。是一种以计算机程序语言来描述硬件电路的语言。设计电路时,如果不借助EDA工具,那仅仅电路绘图就是难以想象的工作量。

而HDL语言的发展中,最终Verilog和VHDL两种成为了主流。Verilog基于C语言开发,基本语法和C语言基本没有差别,学习过C/C++的人可以很容易上手。重要的是思维模式的转变,在写Verilog时,更重要的是脑海中有代码背后实际的电路器件和结构,这样才能真正的用好FPGA。

以下以二选一多路器选择器,利用Verilog描述该器件功能,然后使用Vivado软件对HDL语言所描述的电路综合、逻辑仿真等后续过程。

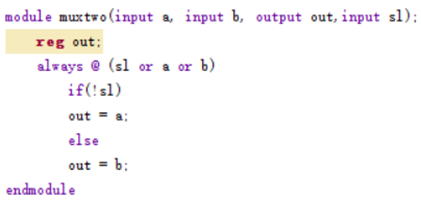

1. Verilog程序语言描述

Verilog HDL描述二选一多路的逻辑功能,2个输入端a和b,1个输出端out,一个片选信号sl。当sl为低电平时,输出信号为a路;当sl为高电平时,输出信号为b路。

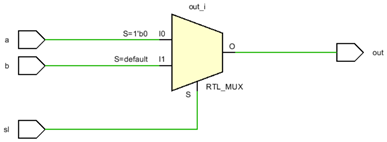

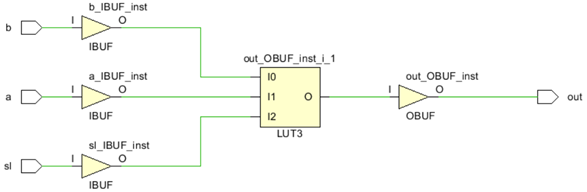

2. RTL Elaboration

经过Vivado软件转化后,会将软件描述转化为RTL级描述,如下图所示。

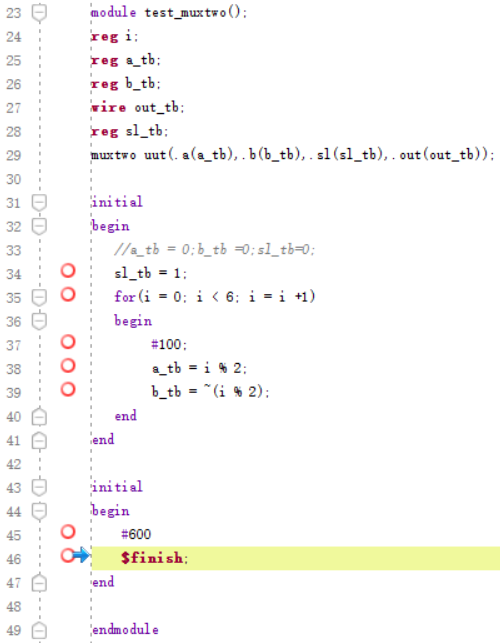

3. Testbench 文件

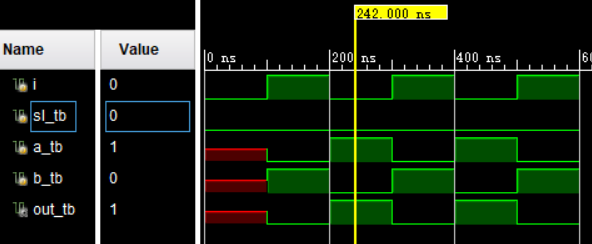

编写testbench测试文件,验证电路静态逻辑的正确性。

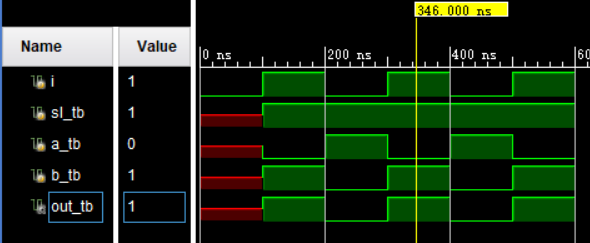

逻辑仿真结果,sl = 1,out = b;

逻辑仿真结果,sl = 1,out = a;

4. Synthesis Diagram

RTL级电路综合后,会给出门级电路,此时就可以配置FPGA相应的IO引脚,将门级逻辑电路映射到FPGA的物理引脚上。

Vivado软件的具体使用及工程新建,可参考Xilinx Vivado数字设计权威指南的第四章。

相关学习资料推荐:

[1] Verilog语言:Verilog数字系统设计教程,夏宇闻 编著。

[2] Vivado软件:Xilinx Vivado数字设计权威指南,何宾 编著。

[3] 数字电路及Vivado软件课程:EDA原理及应用,何宾 主讲。

https://www.icourse163.org/course/BUCT-1003369008

最后

以上就是漂亮诺言最近收集整理的关于FPGA入门_2.Verilog语言和Vivado软件对电路的不同层次描述的全部内容,更多相关FPGA入门_2.Verilog语言和Vivado软件对电路内容请搜索靠谱客的其他文章。

发表评论 取消回复