目录写在前面

正文内容简述ASIC设计流程,并列举出各部分用到的工具?

简述FPGA的开发流程?

名词解释

数制转换

什么是竞争和冒险?如何消除?

2分频描述

简述建立时间和保持时间,画图表示?

简述触发器和锁存器之间的差别?

计算最小周期?

什么是Clock Jitter和Clock Skew,这两者有什么区别?

什么是亚稳态,产生的原因,如何消除?

同步与异步?

谈谈对Retiming技术的理解

什么是高阻态?

集成时钟门控单元(Integrated Clock Gating Cell)

更多参考资料

CSDN博客

写在前面

本文其实就是整合了一下去年秋招时总结的笔试题或者各大平台的练习题,只不过去年由于边笔试面试边总结,比较粗糙,这里再次整理润色一下,前人栽树,方便后人乘凉! 注:个人微信公众号、简书、知乎也正在不断发布文章哦!个人微信公众号: FPGA LAB;

简书地址:Reborn_Lee - 简书www.jianshu.com

知乎地址:知乎用户www.zhihu.com

本文内容选自:FPGA笔试题解析(一)_RebornLee-CSDN博客_fpga笔试题blog.csdn.net FPGA笔试题解析(二)_RebornLee-CSDN博客_用d触发器带同步高置数和异步高复位端的二分频的电路blog.csdn.net

FPGA笔试题解析(二)_RebornLee-CSDN博客_用d触发器带同步高置数和异步高复位端的二分频的电路blog.csdn.net FPGA笔试题解析(三)_RebornLee-CSDN博客_阿里fpga笔试blog.csdn.net

FPGA笔试题解析(三)_RebornLee-CSDN博客_阿里fpga笔试blog.csdn.net FPGA笔试题解析(四)_RebornLee-CSDN博客_fpga笔试blog.csdn.net

FPGA笔试题解析(四)_RebornLee-CSDN博客_fpga笔试blog.csdn.net

注:由于微信公众号不能添加外链接,可以选择阅读原文或者直接进入我的CSDN博客阅读,以获得更优的阅读体验!

正文内容

简述ASIC设计流程,并列举出各部分用到的工具?

说实话,半路出家,没弄过ASIC,但是经常遇到ASIC与FPGA开发做比较的题目,不得不主动了解下ASIC设计流程:

百度对ASIC的解释(了解):

ASIC全称: Application Specific Integrated Circuit,是一种为专门目的而设计的集成电路。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

FPGA是ASIC的近亲,一般通过原理图、VHDL对数字系统建模,运用EDA软件仿真、综合,生成基于一些标准库的网络表,配置到芯片即可使用。它与ASIC的区别是用户不需要介入芯片的布局布线和工艺问题,而且可以随时改变其逻辑功能,使用灵活。

ASIC设计流程

这篇文章中给出的流程可供参考:详解ASIC设计流程_RebornLee-CSDN博客_asic流程工程师blog.csdn.net

流程图:

即:需求(Requirements)

技术指标(Specifications)

架构(Architecture)

数字设计(Digital Design)

验证(Verification)

逻辑综合(Logic Synthesis)

逻辑对等(Logic Equivalence)

布局和布线(Placement and Routing)

验证 (Validation)

具体含义,请转往地址:

同时还可以参考如下流程图:

还有:

大致流程都差不多,你能自己说出大概即可,没必要面面俱到!

简述FPGA的开发流程?

FPGA的开发流程可以从FPGA的开发工具ISE或者Vivado上看出, 例如ISE:

如Vivado:

总结出来的大概流程为:

想要更详细一点的流程可以参考这个:

此图对应的文档为:Best-FPGA-Development-Practices-2014-02-20-嵌入式文档类资源-CSDN下载download.csdn.net

从ISE以及Vivado开发工具上可以看出的过程有:RTL代码的编写,可以使用原理图、Verilog HDL以及VHDL来开发,

之后可以进行功能仿真,验证设计是否正确,是否符合逻辑,

之后就可以进行综合,将RTL代码映射到基本逻辑门单元,触发器上。

之后进行实现,实现包括三个步骤:翻译,映射以及布局布线。

这三者完成了什么工作,请跳转到:XIlinxFPGA开发基本流程(一)(总介绍)_RebornLee-CSDN博客_fpga开发blog.csdn.net

这是在ISE中有的套路,在Vivado开发工具中可没这么复杂,vivado生成的网表格式是一致的,没有ISE那么多,那么杂。 最后生成bit流文件,烧写(编程)进FPGA即可。

名词解释

ROM:Read Only Memory,只读存储器,手机、计算机等设备的存储器,但现在的所说的ROM不只是Read Only了,也是可以写入的。

RAM:Random Access Memory,随机存取存储器,手机、计算机的运行内存。

SRAM:Static Random-Access Memory,静态随机存取存储器,只要供电数据就会保持,但断电数据就会消失,也被称为Volatile Memory

DRAM:Dynamic Random Access Memory,动态随机存储器,主要原理是利用电容存储电荷的多少来代表一个bit是0还是1,由于晶体管的漏电电流现象,电容会放电,所以要周期性的给电容充电,叫刷新。SRAM不需要刷新也会保持数据丢失,但是两者断电后数据都会消失,称为Volatile Memory

SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器,同步写入和读出数据的DRAM。

EEPROM:Electrically Erasable Programmable Read Only Memory,电可擦除可编程只读存储器,

DDR:Double Data Synchronous Dynamic Random Access Memory,双倍速率同步动态随机存储器,双倍速率传输的SDRAM,在时钟的上升沿和下降沿都可以进行数据传输。我们电脑的内存条都是DDR芯片。

FLASH: Flash Memory,闪存,非易失性固态存储,如制成内存卡或U盘。

关于这部分,我以前也有总结过:RAM简记_RebornLee-CSDN博客_born简记blog.csdn.net

ROM简记_RebornLee-CSDN博客_born简记blog.csdn.net

IP核之软核、硬核、固核简记_RebornLee-CSDN博客_ip软核blog.csdn.net

数制转换R进制数转换为十进制数:按权展开,相加

十进制数转化为R进制数:整数部分,除R取余法,除到商为0为止。小数部分,乘R取整法,乘到积为0为止。

二进制数转化八进制数:三位一组,整数部分左边补0,小数部分右边补0。反之亦然。

二进制数转化十六进制数:四位一组,整数部分左边补0,小数部分右边补0。反之亦然。

什么是竞争和冒险?如何消除?

之前写过类似的系列文章,参考自《FPGA之道》:【FPGA】组合逻辑中的竞争与险象问题(二)_RebornLee-CSDN博客_fpga逻辑竞争问题解决方法blog.csdn.net

如果在某一个时刻,从组合逻辑的某一个输入端到其输出端存在两条以上的电信号通路时,就称该组合逻辑在当前状态下针对这个输入端存在竞争。

举例:

当B=1、C=1时,电路可以化简为:

输入为A先于not(A)A非到达或门,因此,如果初始令A为1,则NOT(A)为0,之后A变化为0,则由于A先到或门,导致有一小段零脉冲出现在输出中,这是非预期的。

信号由于经由不同路径传输达到某一汇合点的时间有先有后的现象,就称之为竞争,由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险,FPGA设计中最简单的避免方法是尽量使用时序逻辑同步输入输出。

在FPGA中消除险象的方法:

后向消除中最具有代表性的方法就是时序采样法,在消除险象的各种方法中,时序采样法的使用最为广泛。可以说,只要你描述的是一个时序逻辑,你就已经有意或无意的使用了时序采样法来消除险象。

时序采样法几乎是万能的,因为对于任何一个组合逻辑来说,其输入与输出之间总存在一个最大延迟的路径。设这个最大的路径延迟为T,如果其输入在0时刻变化一次后就保持不变,那么T时刻后,其输出肯定会稳定到新输入应该对应的输出上,而在0到T时刻之间,该组合逻辑的输出可能会出现一系列不稳定现象。

因此,如果该组合逻辑是同步逻辑的一部分,那么我们只需要适当选择周期大于T的信号作为时钟就可以绕过0到T这段有问题的时刻,而采样到T时刻以后的稳定且正确的输出。并且由于每次组合逻辑的输入改变后都会在接下来至少T时刻以上的时间保持不变,因此也能保证输出具有足够的时间达到稳定。 由此可见,时序采样法的最大优点就是根本不关心组合逻辑的内容,因此适用面非常广。

2分频描述

用D触发器实现带同步高置数和异步高复位端的二分频的电路,画出逻辑电路,Verilog描述!

module freq_div2(

input clk,

input rst,

input set,

output reg Q

);

always @(posedge clk or posedge rst)begin

if(rst == 1'b1)

Q <= 1'b0;

else if(set == 1'b1)

Q <= 1'b1;

else

Q <= ~Q;

end

endmodule

用Quartus生成RTL电路图:

尝试过用ISE生成,可是ISE唯一一点让我不满意的就是这个图的生成,看起来很让人眼花缭乱,不简洁:

当然,生成的原理图是一模一样的,只是元件风格问题。Quartus更接近于手写。

为了比较也是拼了,Vivado生成的原理图也比较简洁:

简述建立时间和保持时间,画图表示?

建立时间Tsu(setup):触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

保持时间Th(hold):触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。

这个题目问的还是太简单了,不过面试仍可能就是这么问!

我总结了和建立时间以及保持时间有关的笔试题,供大家参考,请跳转到如下链接:IC/FPGA笔试/面试题分析(七)建立时间和保持时间类型考题汇总分析_RebornLee-CSDN博客_建立时间t.cn

简述触发器和锁存器之间的差别?

锁存器对电平信号敏感,在输入脉冲的电平作用下改变状态。

D触发器对时钟边沿敏感,检测到上升沿或下降沿触发瞬间改变状态。 下面链接搜集了互联网上关于触发器和锁存器的区别说法:锁存器和触发器的区别_RebornLee-CSDN博客_锁存器和触发器区别t.cn

计算最小周期?

Tco:寄存器更新延迟,clock output delay,时钟触发到数据输出的最大延迟时间

最小时钟周期:Tmin = Tco + Tdata + Tsu - Tskew。最快频率Fmax = 1/Tmin

Tskew = Tclkd – Tclks。

什么是Clock Jitter和Clock Skew,这两者有什么区别?

时钟抖动(Clock Jitter):时钟抖动是时钟源和时钟信号环境的特征。可以将其定义为“时钟沿与理想位置的偏差”。 时钟抖动通常由时钟发生器电路,噪声,电源变化,附近电路的干扰等引起。抖动是为时序收敛指定的设计余量的一个影响因素。

如下图:

蓝色的时钟表示理想情况下的时钟,红色的线表示抖动时钟边沿可以出现的问题。

时钟抖动可以带来很多问题,例如:

这里为了延伸阅读,提供一个关于时钟抖动问题的文档:

如果没有,则代表被和谐,可联系我(公众号:FPGA LAB或者CSDN : 李锐博恩)

时钟偏移(Clock Skew):或者称为时钟偏斜,是由于布线长度及负载不同引起的,导致同一个时钟信号到达相邻两个时序单元的时间不一致。

如下图:

选看作为由于时钟偏斜而导致的电路故障操作的示例,请考虑上图所示的串行输入移位寄存器的前两级。 这两个沿边沿触发的DFF都是从相同的时钟源馈送的,但是Ck + t d到达FF2的时钟输入的时间相对于FF1时钟输入的时钟输入Ck延迟了td。输入数据 data 至FF1 在Ck的上升沿之后的时间 t f 传输到其输出Q 1。 Q 1也是输入到FF2的数据,如果 t d> t f,则在Ck + t d的上升沿之后的时间tf处将输入数据传输到FF2的输出。在接收到单个时钟脉冲时,输入数据已通过移位寄存器的两级传输。由于在移位寄存器的每一级之间没有组合逻辑,因此很明显,时钟偏移问题在移位寄存器的设计和操作中特别重要。 如果td < tf,恐怕第二级触发器对数据的采样就会出现错误。

区别:Jitter是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。Skew是由不同布线长度导致的不同路径的时钟上升沿到来的延时不同。

更多内容跳转下面链接以及文章末尾更多参考资料链接:

什么是亚稳态,产生的原因,如何消除?

这个问题的详细介绍在博文:【FPGA】稳态与亚稳态小结_RebornLee-CSDN博客_亚稳态blog.csdn.net

篇幅过大,给出简洁解释:

如果触发器的输入电压采样时间过短,即时序不够,则触发器需要花很长时间来实现输出逻辑达到标准电平,也就是说,电路处于中间态的时间变长,使得电路“反应”迟钝,这就是“亚稳态”。(例如输入信号在时钟有效沿的建立时间和保持时间之间改变了,导致不满足触发器的建立时间或保持时间,导致输出有一段时间的不稳定态,就是亚稳态。)

消除:两级或多级寄存器同步。理论上亚稳态不能完全消除,只能降低,一般采用两级触发器同步就可以大大降低亚稳态发生的概率,再加多级触发器改善不大。

但注意双触发器作为同步器只能用在单比特数据的传递中。对于多比特数据的操作一般使用异步FiFO。

异步FIFO见链接:FPGA基础知识极简教程(4)从FIFO设计讲起之异步FIFO篇_RebornLee-CSDN博客blog.csdn.net

参考代码:

reg data_mid;

reg data_out;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

data_mid <= 1'b0;

data_out <= 1'b0;

end

else begin

data_mid <= data_in;

data_out <= data_mid;

end

end

同步与异步?

同步复位和异步复位的区别?

同步复位是时钟边沿触发时判断是否有效,和时钟有关。异步复位是复位信号有效和时钟无关。

如异步复位:

同步复位:

有关更详细的复位策略介绍可见下链接:Reset Design Strategym.eet.com

或者:

复位策略download.csdn.net

如不能下载,则代表被和谐。可以联系我个人微信公众号FPGA LAB或者CSDN : 李锐博恩获得。

同步逻辑和异步逻辑的区别

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系

同步电路和异步电路区别

同步电路有统一的时钟源,经过PLL分频后的时钟驱动的模块,因为是一个统一的时钟源驱动,所以还是同步电路。异步电路没有统一的时钟源。

谈谈对Retiming技术的理解

Retiming就是重新调整时序,例如电路中遇到复杂的组合逻辑,延迟过大,电路时序不满足,这个时候采用流水线技术,在组合逻辑中插入寄存器加流水线,进行操作,面积换速度思想。

例如,可以改变寄存器的位置来减小最小时钟周期:

有关retiming的学问还很多,进一步了解可以跳转链接:retimingpeople.ece.umn.edu

注:打不开就算了吧!

什么是高阻态?

高阻态:

电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,可以理解为断路,不被任何东西所驱动,也不驱动任何东西。

之前写过和高阻态相关的博文:【FPGA】总线实现形式之三态门_RebornLee-CSDN博客_fpga三态门blog.csdn.net

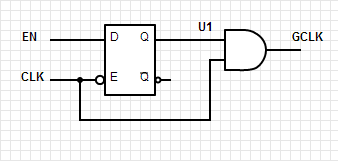

集成时钟门控单元(Integrated Clock Gating Cell)

门控时钟之前也写过相关博文:【FPGA】门控时钟专题_RebornLee-CSDN博客_fpga门控时钟blog.csdn.net

时钟门控是一种通过时钟使能信号关闭模块时钟来降低时钟功耗的常用技术。时钟门控功能仅需要一个AND或OR门。 考虑你正在使用带时钟的AND门。 高EN边沿可能随时出现,可能与时钟边沿不一致。 在这种情况下,AND门的输出将比时钟占空比的时间短1。 您最终会在时钟信号中出现毛刺。

为避免这种情况,使用了一种特殊的时钟门控单元,它使EN与时钟边沿同步。 这些叫集成时钟门控单元或ICG。

通常有两种类型的实现方式:

而如下链接给出的方法:Integrated Clock Gating Cellvlsi.pro

与门实现方式:

或门实现方式:

最后总结一句,使用门控时钟,可以降低功耗,因为只有在En有效范围内提供时钟。

更多参考资料

CSDN博客

各大搜索引擎还可以直接搜索李锐博恩关注我。

最后

以上就是专一酸奶最近收集整理的关于vivado 亚稳态_FPGA/ASIC笔试面试题集锦(1)知识点高频复现练习题的全部内容,更多相关vivado内容请搜索靠谱客的其他文章。

发表评论 取消回复