一、 实验目的

1.掌握基本门电路的实际应用;

2.掌握基本门多余端的处理方法;

3.验证所设计电路的逻辑功能;

4.判断、观察组合逻辑电路险象并消除险象的方法;

二、 主要仪器设备及软件

硬件:逻辑分析仪、函数发生器、数字信号发生器

软件:Multisim 14.0

三、 实验任务

1.与非门逻辑功能测试,测试74LS00与非门的逻辑功能。

2.数字锁逻辑电路,用与非门设计一数字逻辑锁电路,该锁有3个按钮A、B、C,当A、B、C同时按下,或只有A和B同时按下或只有A或B按下时开锁,如果不符合上述条件应发出警报。

3.冒险及其消除方法

(1)试用示波器来判断是否存在逻辑险象、险象的类型及出现的条件。

(2)在输出端加接滤波电容,观察毛刺的变化情况。

(3)用修改逻辑设计的方法来消除所出现的险象。

四、 设计过程与实验结果

1.与非门逻辑功能测试

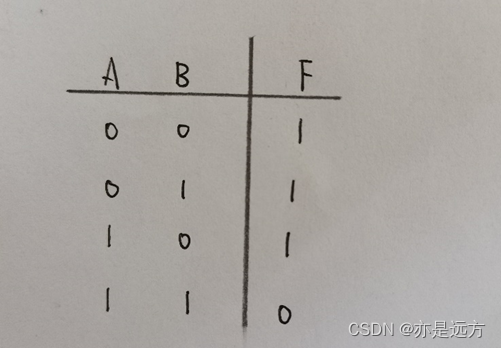

分析与非门的真值表如下所示:

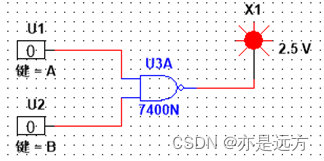

仿真测试电路图如图2所示。

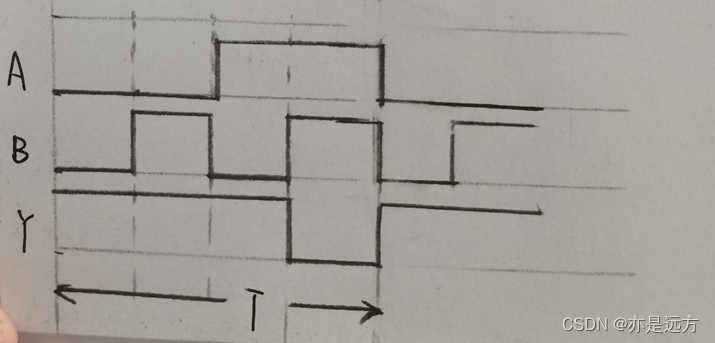

与非门仿真波形图

实验结果:当A、B全为1时,F输出为0,指示灯不亮。其他情况,F输出1,指示灯亮。即“有0出0,无0出1”。

2.数字锁

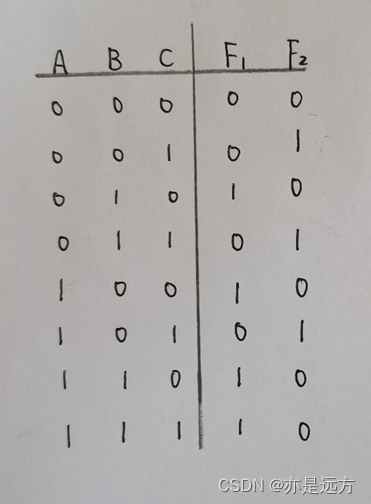

A、B、C为三个输入端,F1为开锁,F2为报警。分析如下:

逻辑真值表

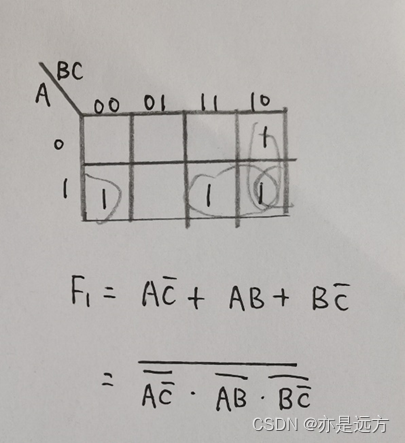

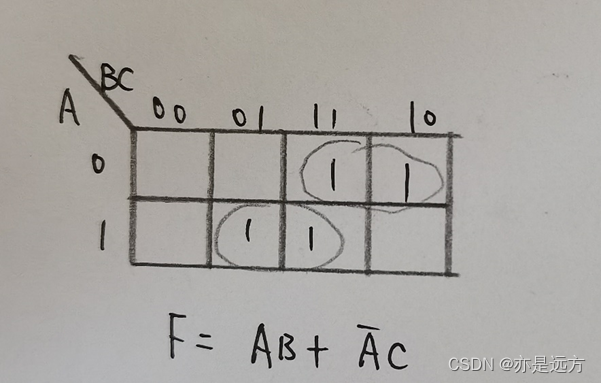

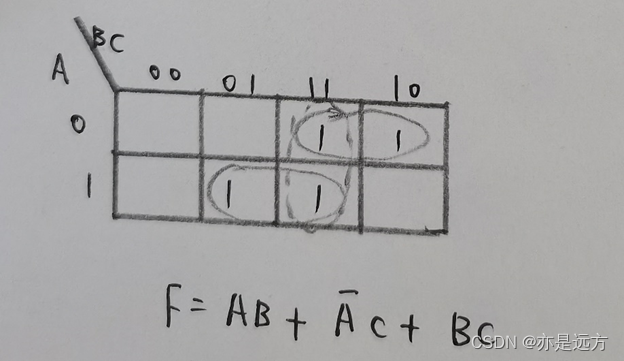

卡诺图化简

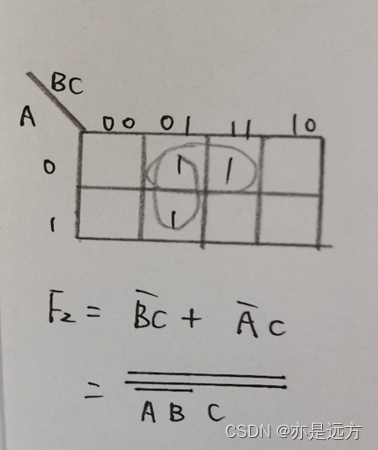

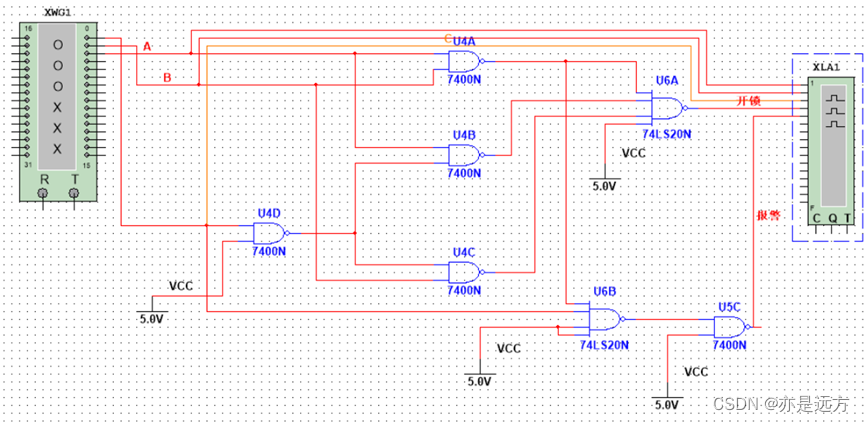

电路图

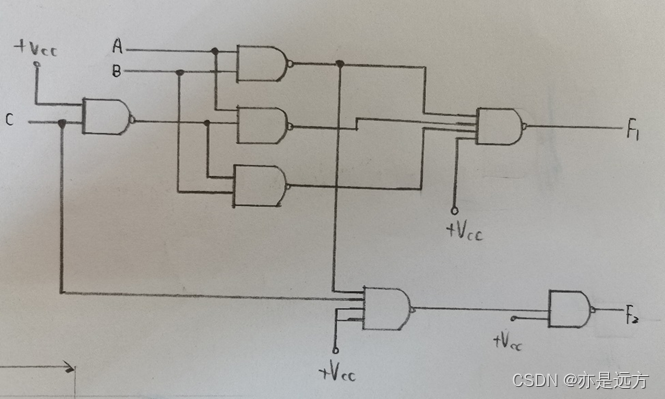

仿真实验图如图所示:

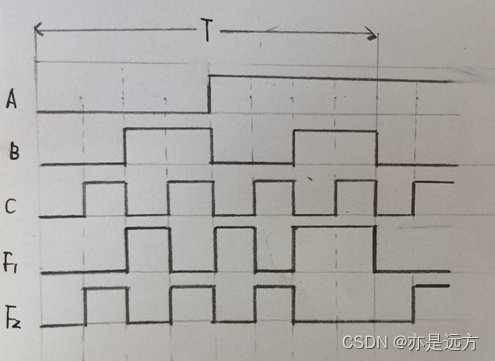

键盘按键A、B、C可控制三个输入端。调整三个输入端ABC从000至111,观察F1,F2的现象。实验测试结果如下:

| A | B | C | F1 | F2 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 |

实验结果:结果与真值表一致。

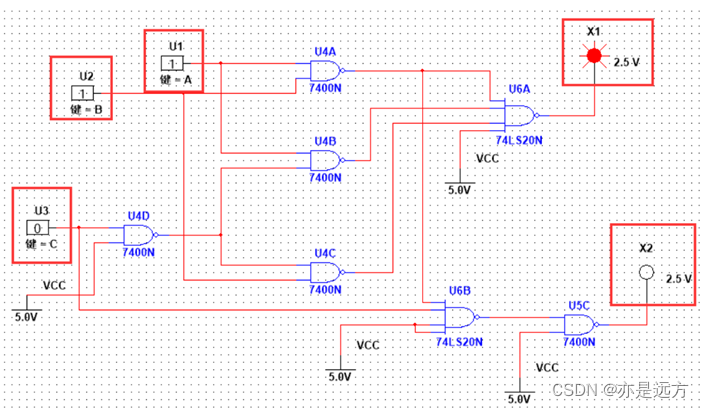

数字锁动态仿真实验图如下:

使用字发生器和逻辑分析仪,设计逻辑锁电路。

逻辑分析仪所示的波形图如下:

实验结果:波形表示与真值表一致,该数字锁设计成功。

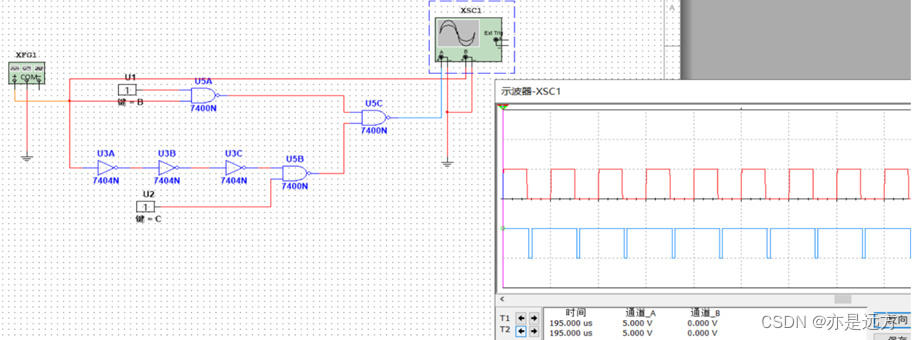

3.冒险及其消除

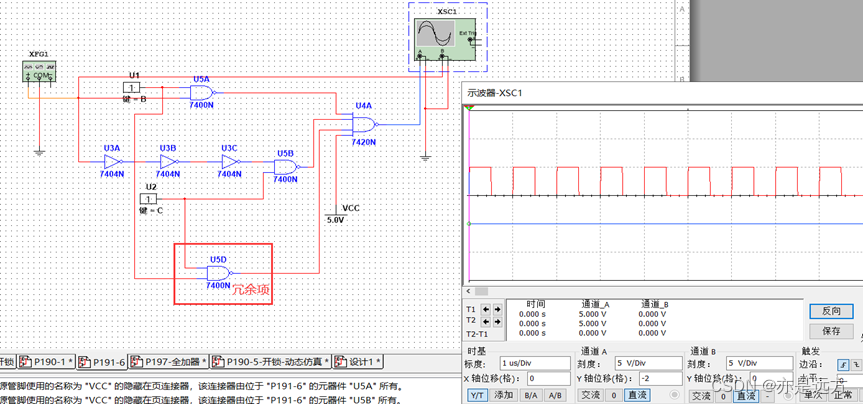

仿真实验电路,及其毛刺情况如图6所示:

(注:蓝色波形为输出F的信号,下同)

图6 冒险-电路图

由图中可得,电路出现毛刺,存在险象。

首先分析该电路的输出F信号:

分析: 当B=0,C=0时,F=0;

当B=0,C=1时,F=A非;

当B=1,C=0时,F=A;

当B=C=1时,F=A+A非,此时出现1-0-1险象。

从卡诺图中也可分析:

图中有一对相切的卡诺圈,所以:当ABC从011<—>111时,跨越了相切的卡诺圈,电路会出现逻辑冒险,产生毛刺,毛刺如图6蓝色波形所示。

冒险消除方法:

①添加冗余项:(该方法可以消除逻辑冒险)

方法原理:在卡诺图中两圈相切处增加一个冗余圈,可以消除逻辑冒险。

将“BC”用卡诺圈圈上,这样便不存在相切的卡诺圈,可以消除逻辑冒险。

增加冗余项后的仿真电路及冒险消除结果如图7所示:

图7 添加冗余项消除冒险

实验结果:从图中可看出,输出F的信号(蓝色波形)毛刺不存在,险象消除。

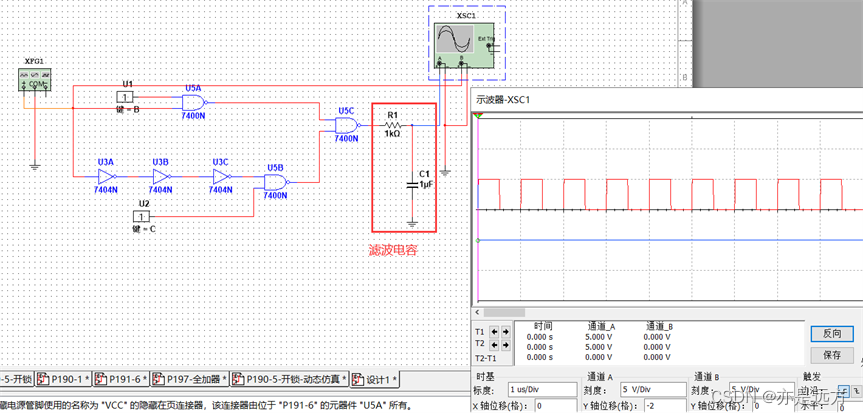

②接滤波电容:(该方法可以消除逻辑冒险和功能冒险)

方法原理:因为冒险所呈现的窄脉冲含有丰富的高频成分,在电路输出端并接一个电容(该电容容量约为几十皮法),电容滤除了大部分的高频成分,只保留低频成分,因此输出波形变得平缓,吸收掉冒险的尖峰脉冲。

实验结果:从图中可看出,输出F的信号(蓝色波形)毛刺不存在,险象消除。

最后

以上就是冷艳板凳最近收集整理的关于南京邮电大学电工电子基础B实验六(组合逻辑电路)的全部内容,更多相关南京邮电大学电工电子基础B实验六(组合逻辑电路)内容请搜索靠谱客的其他文章。

发表评论 取消回复