题目中给出了状态转换、信号示意图以及波形图。

题目要求:输入输出均为wire类型。

为了更清楚题目所给的状态转移,采用表格的形式来展现

状态转换:

| d | sel |

|---|---|

| d0 | 11 |

| d1 | 10 |

| d2 | 01 |

| d3 | 00 |

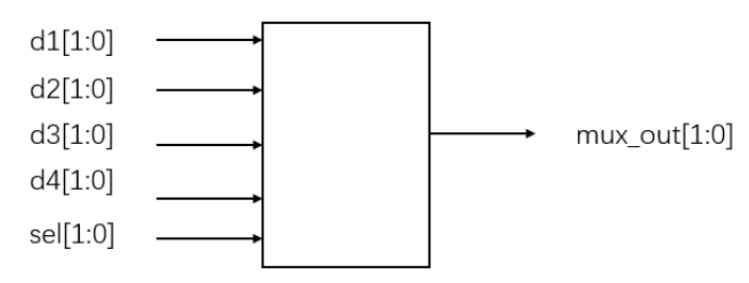

信号示意图:

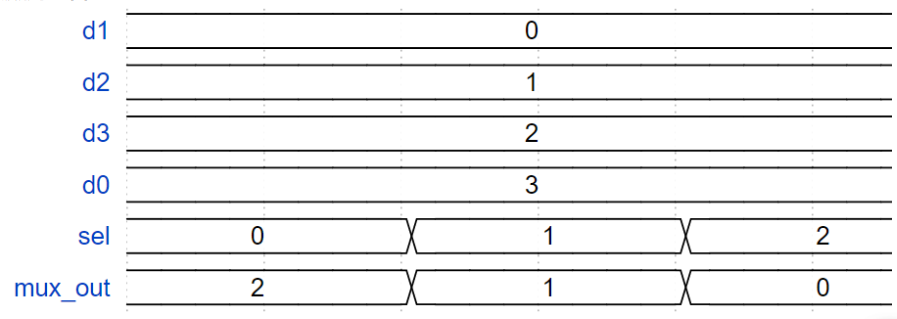

波形示意图:

注意:波形图给出的d1,d3是错误的,状态转换中,d1 为10,因此是2,而波形中是0,d3为00,因此为0,而波形中是2。本题以波形图为标准来编写Verilog。

同学解答了我的疑问,数据和波形没有问题,但是题目的状态转移我觉得写的也不是很规范,理解起来会有偏差,在写任何数据的时候,建议大家也要标记清楚各个数据代表的意思,一目了然。

如下编写可运行通过,但与题目不符,题目要求输出必须是wire,因此我们需要引入一个变量来寄存输出数据,然后通过线网类型wire给最终的输出变量mux_out

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output reg [1:0]mux_out

);

//*************code***********//

always @ (*)

begin

case(sel)

2'b00 : mux_out = d3;

2'b01 : mux_out = d2;

2'b10 : mux_out = d1;

2'b11 : mux_out = d0;

default : mux_out = d0;

endcase

end

//*************code***********//

endmodule

如下引入了reg类型的变量,mux_out_reg。符合要求且正常运行。

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output [1:0]mux_out

);

//*************code***********//

reg [1:0] mux_out_reg;

always @ (*)

begin

case(sel)

2'b00 : mux_out_reg = d3;

2'b01 : mux_out_reg = d2;

2'b10 : mux_out_reg = d1;

2'b11 : mux_out_reg = d0;

default : mux_out_reg = d0;

endcase

end

assign mux_out = mux_out_reg;

//*************code***********//

endmodule

题目的收获:

1、区分二进制表示形式与十进制表示形式(之前一直搞不懂该写2‘b0,还是

2’d0)

2’b00 = 2’d0

2’b01 = 2’d1

2’b10 = 2’d2

2’b11 = 2’d3

2、begin … end 中的变量必须用reg类型,但这里并不是给定了reg型,就非得是阻塞赋值或者非阻塞赋值,上面代码虽然是begin end中的变量是reg类型,但是还是使用的 =

3、case语句中,always块中的敏感列表直接写 * ,always@(*) ,表示所有的输入均为敏感变量。

4、用case语句,后面要加default,本来我认为sel输入包含了所有的01情况,也可不加,但是输入还有可能出现x或者h高阻态类型的情况,因此仍然需要加入default,建议不管输入是否包含所有情况,都加default

题库

最后

以上就是暴躁芹菜最近收集整理的关于牛客网Verilog快速入门题目收获——四选一多路器(VL1)的全部内容,更多相关牛客网Verilog快速入门题目收获——四选一多路器(VL1)内容请搜索靠谱客的其他文章。

![[从零开始学习FPGA编程-33]:进阶篇 - 基本时序电路-寄存器(Verilog语言)](https://www.shuijiaxian.com/files_image/reation/bcimg23.png)

发表评论 取消回复