主要内容摘自Quartus prime

Recommended Design Practices

For optimal performance, reliability, and faster time-to-market when designing with Altera devices, you should adhere to the following guidelines:

• Understand the impact of synchronous design practices

• Follow recommended design techniques, including hierarchical design partitioning, and timing

closure guidelines

• Take advantage of the architectural features in the targeted device

Following Synchronous FPGA Design Practices

Good synchronous design practices can help you meet your design goals consistently. Problems with other design techniques can include reliance on propagation delays in a device, which can lead to race conditions, incomplete timing analysis, and possible glitches.

In a synchronous design, a clock signal triggers every event. As long as you ensure that all the timing requirements of the registers are met, a synchronous design behaves in a predictable and reliable manner for all process, voltage, and temperature (PVT) conditions.

Implementing Synchronous Designs

Because the internal circuitry of registers isolates data outputs from inputs, instability in the combinational logic does not affect the operation of the design as long as you meet the following timing requirements:

• Before an active clock edge, you must ensure that the data input has been stable for at least the setup time of the register.

• After an active clock edge, you must ensure that the data input remains stable for at least the hold time of the register.

Asynchronous Design Hazards

Asynchronous design techniques have inherent problems such as relying on propagation delays in a device, which can vary with temperature and voltage fluctuations, resulting in incomplete timing constraints and possible glitches and spikes.

HDL Design Guidelines

When designing with HDL code, you should understand how a synthesis tool interprets different HDL design techniques and what results to expect.

Altera recommends that you design your combinational logic carefully to avoid potential problems and pay attention to your clocking schemes so that you can maintain synchronous functionality and avoid timing problems.

Optimizing Combinational Logic

In Altera FPGAs, these functions are implemented in the look-up tables (LUTs) with either logic

elements (LEs) or adaptive logic modules (ALMs).

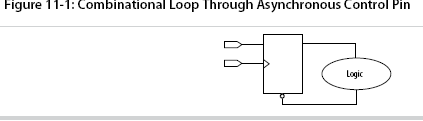

Avoid Combinational Loops

Combinational loops are among the most common causes of instability and unreliability in digital

designs. Combinational loops generally violate synchronous design principles by establishing a direct feedback loop that contains no registers.

You should avoid combinational loops whenever possible. In a synchronous design, feedback loops should include registers. For example, a combinational loop occurs when the left-hand side of an arithmetic expression also appears on the right-hand side in HDL code. A combinational loop also occurs when you feed back the output of a register to an asynchronous pin of the same register through combinational logic.

Avoid Unintended Latch Inference

A latch is a small circuit with combinational feedback that holds a value until a new value is assigned.

It is common for mistakes in HDL code to cause unintended latch inference; Quartus Prime Synthesis issues a warning message if this occurs. Unlike other technologies, a latch in FPGA architecture is not significantly smaller than a register. The architecture is not optimized for latch implementation and latches generally have slower timing performance compared to equivalent registered circuitry.

Latches have a transparent mode in which data flows continuously from input to output. Be aware that even an instantaneous transition through transparent mode can lead to glitch propagation. The TimeQuest analyzer cannot perform cycle-borrowing analysis.

Due to various timing complexities, latches have limited support in formal verification tools.

Avoid Delay Chains in Clock Paths

You require delay chains when you use two or more consecutive nodes with a single fan-in and a single fan-out to cause delay. Inverters are often chained together to add delay. Delay chains are sometimes used to resolve race conditions created by other asynchronous design practices.

Effects such as rise and fall time differences and on-chip variation mean that delay chains, especially those placed on clock paths, can cause significant problems in your design. Avoid using delay chains to prevent these kinds of problems.

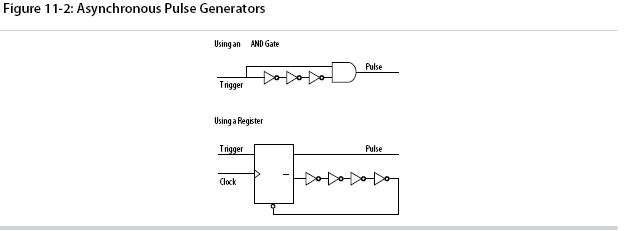

Use Synchronous Pulse Generators

You can use delay chains to generate either one pulse (pulse generators) or a series of pulses

(multivibrators). There are two common methods for pulse generation. These techniques are purely asynchronous and must be avoided.

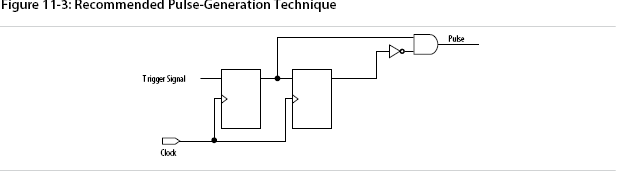

When you must use a pulse generator, use synchronous techniques.

The pulse width is always equal to the clock period. This pulse generator is predictable, can be verified with timing analysis, and is easily moved to other architectures, devices, or speed grades.

转载于:https://www.cnblogs.com/dashawntang/p/7206625.html

最后

以上就是动人宝贝最近收集整理的关于推荐 的FPGA设计经验(1)组合逻辑优化Recommended Design Practices的全部内容,更多相关推荐内容请搜索靠谱客的其他文章。

发表评论 取消回复