VL22 根据状态转移图实现时序电路

这里我把 00状态 记为 aa

01状态 记为 bb

10状态 记为 cc

11状态 记为 dd

parameter aa = 2'b00;

parameter bb = 2'b01;

parameter cc = 2'b10;

parameter dd = 2'b11;

因为有四个状态,所以设计两个2位寄存器用来存储当前状态和下一个状态

reg[1:0] cur;

reg[1:0] nex;

当初始化是,当前状态为00(aa),下一个状态也是00(aa)

rtl代码

`timescale 1ns/1ns

module seq_circuit(

input C ,

input clk ,

input rst_n,

output wire Y

);

parameter aa = 2'b00;

parameter bb = 2'b01;

parameter cc = 2'b10;

parameter dd = 2'b11;

reg[1:0] cur;

reg[1:0] nex;

reg yy;

always @(posedge clk or negedge rst_n)

if(!rst_n) begin

cur <= aa;

nex <= aa;

end

else

cur <= nex;

always@(*) begin

case (cur)

aa: begin

if(C == 1'b0)

nex = aa;

else

nex = bb;

yy = 1'b0;

end

bb: begin

if(C == 1'b0)

nex = dd;

else

nex = bb;

yy = 1'b0;

end

cc: begin

if(C == 1'b0) begin

nex = aa;

yy = 1'b0;

end

else begin

nex = cc;

yy = 1'b1;

end

end

dd: begin

if(C == 1'b0)

nex = dd;

else

nex = cc;

yy = 1'b1;

end

endcase

end

assign Y = yy;

endmodule

testbench 代码

`timescale 1ns / 1ps

module aaa1_tb( );

reg C ;

reg clk;

reg rst_n;

wire Y;

aaa aaa_1(

.clk(clk),

.rst_n(rst_n),

.C(C),

.Y(Y)

);

initial begin

C = 0; clk = 0; rst_n = 0;

#5 C = 0; clk = 1; rst_n = 1;

#5 C = 1; clk = 0; rst_n = 1;

#5 C = 1; clk = 1; rst_n = 1;

#5 C = 0; clk = 0; rst_n = 1;

#5 C = 0; clk = 1; rst_n = 1;

#5 C = 1; clk = 0; rst_n = 1;

#5 C = 1; clk = 1; rst_n = 1;

#5 C = 0; clk = 0; rst_n = 1;

#5 C = 0; clk = 1; rst_n = 1;

$stop;

end

endmodule

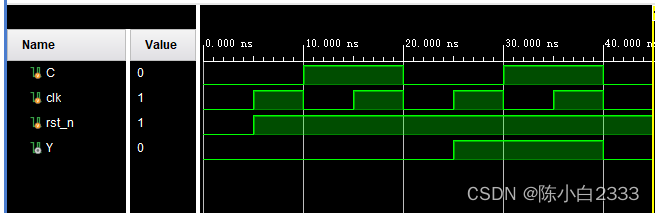

波形图

最后

以上就是糊涂鞋子最近收集整理的关于VL22 根据状态转移图实现时序电路的全部内容,更多相关VL22内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复