电平触发与边沿触发

always块可以使用电平触发也可以使用边沿触发,电平触发往往对应组合逻辑,边沿触发往往对应时序逻辑

举例

在这个例子中,timing变量通过边沿触发来赋值,comb通过电平触发来赋值

`timescale 1ns / 1ps

module test(

input clk,

input [2:0] a,

output reg timing,

output reg comb

);

always@(posedge clk )begin

if(a>2'd2)

timing<=1;

else

timing<=0;

end

always@(a)begin

if(a>2'd2)

comb=1;

else

comb=0;

end

endmodule

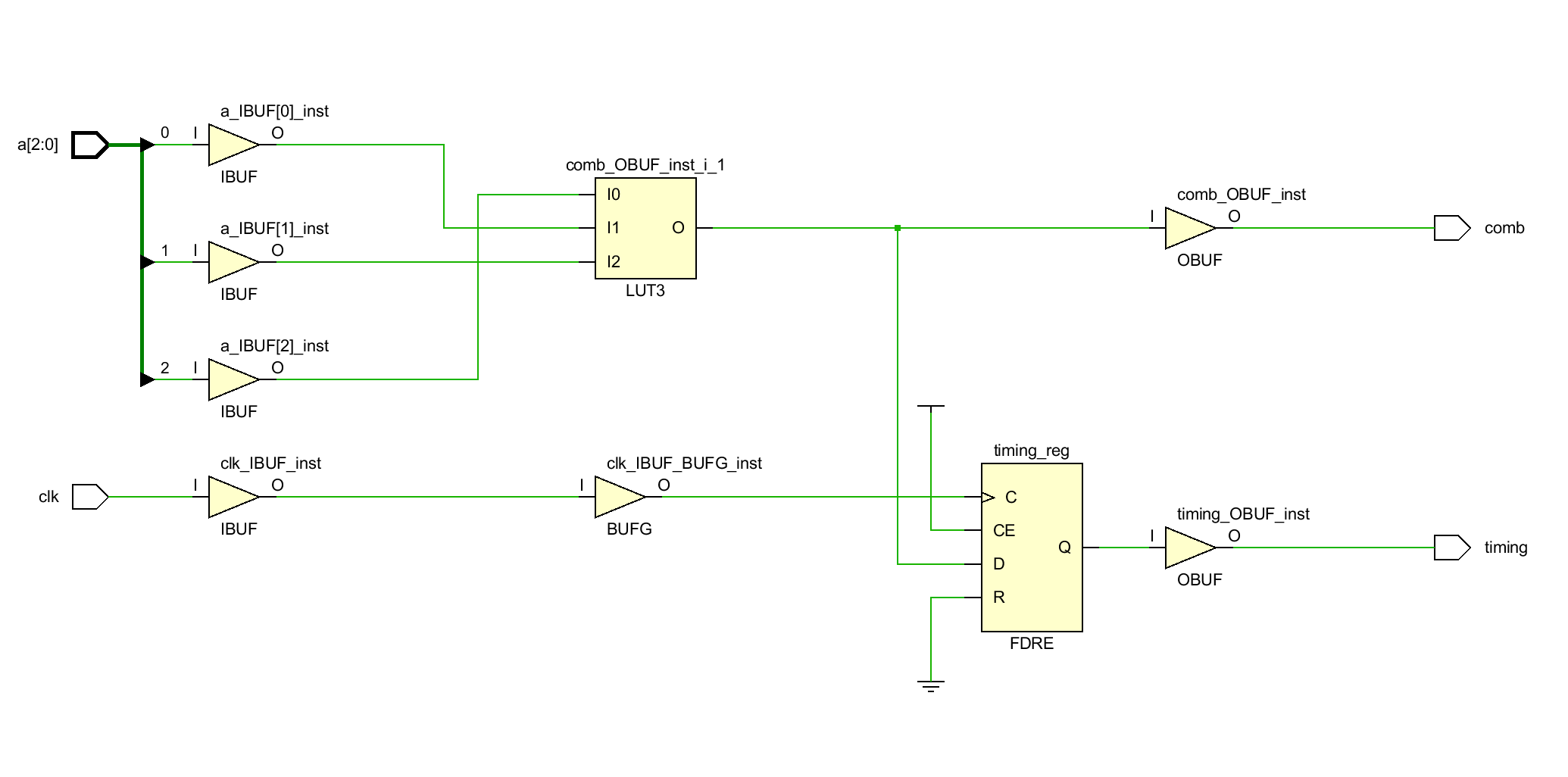

原理图

在原理图中可以看到,输入a经过LUT后分别给到了comb和timing_reg

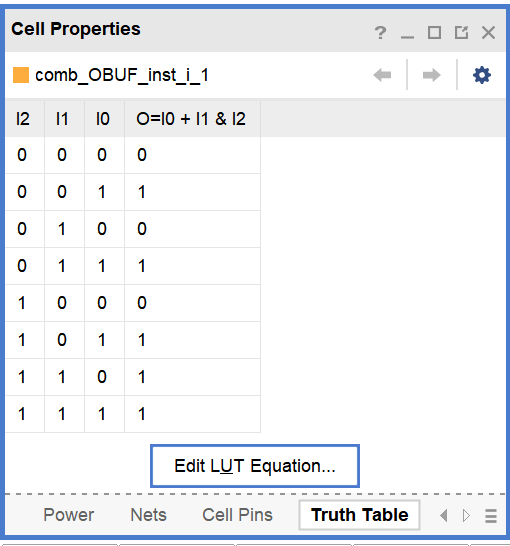

真值表

真值表满足代码中所要求电路实现的功能,在a>0时输出1,否则输出0

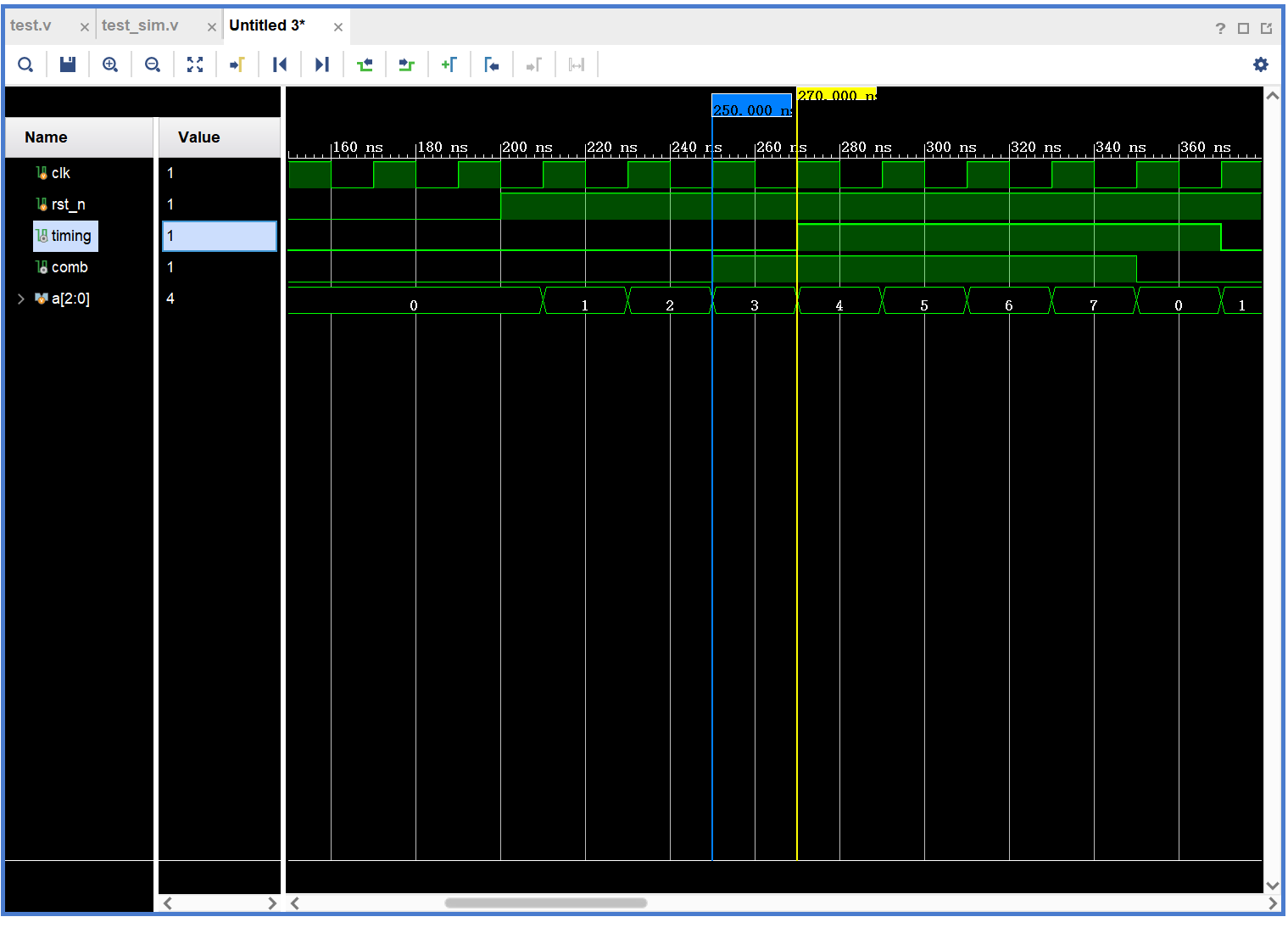

时序

根据时序图,comb比timing早一拍变化,这与原理图中comb的赋值是组合逻辑,timing的赋值是时序逻辑是相对应的

最后

以上就是幸福网络最近收集整理的关于always块的边沿触发与电平触发的全部内容,更多相关always块内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复