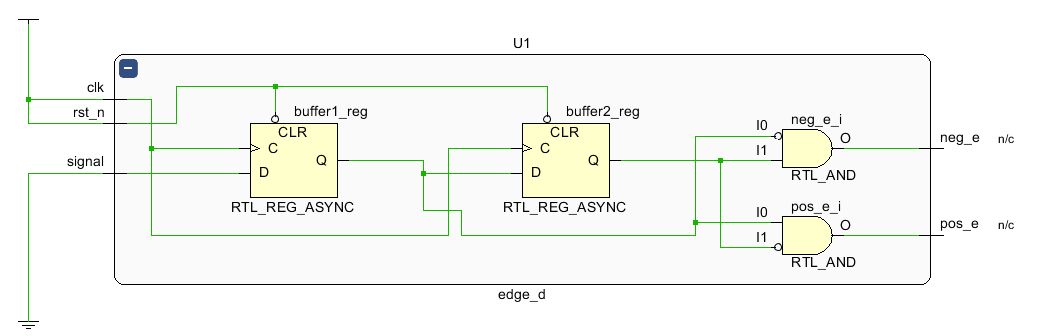

module edge_d(

clk ,

rst_n ,

signal,

//其他信号,举例dout

pos_e,

neg_e

);

//输入信号定义

input clk ;

input rst_n ;

input signal;

//输出信号定义

output pos_e ;

output neg_e ;

//中间信号定义

reg buffer1;

reg buffer2;

//时序逻辑写法

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

buffer1<=0;

buffer2<=0;

end

else begin

buffer1<=signal;

buffer2<=buffer1;

end

end

assign pos_e=~buffer1&&buffer2;

assign neg_e=buffer1&&~buffer2;

endmodule

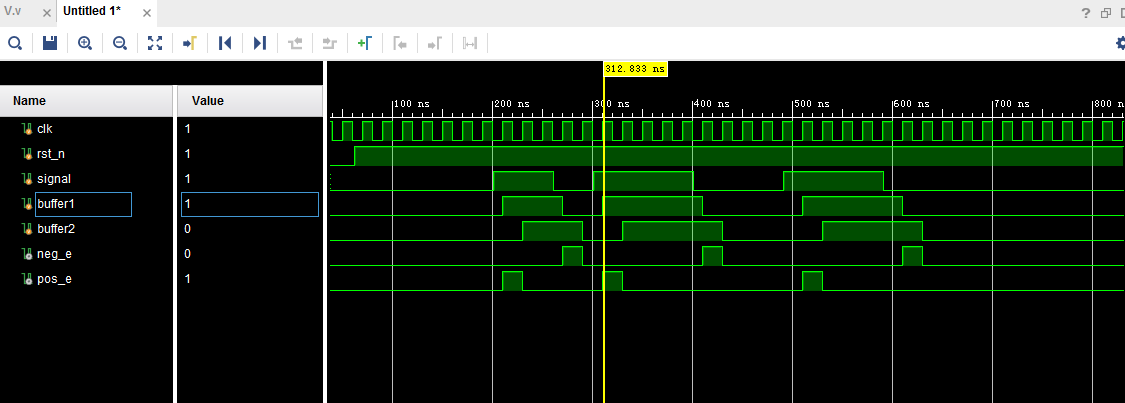

tb

`timescale 1 ns/1 ns

module testbench_name;

//时钟和复位

reg clk ;

reg rst_n;

//uut的输入信号

reg signal ;

//uut的输出信号

wire neg_e ;

wire pos_e ;

//时钟周期,单位为ns,可在此修改时钟周期。

parameter CYCLE = 20;

//复位时间,此时表示复位3个时钟周期的时间。

parameter RST_TIME = 3 ;

//待测试的模块例化

edge_d U1(

.clk ( clk ) ,

.rst_n ( rst_n ) ,

.signal ( signal ) ,

.pos_e ( pos_e ) ,

.neg_e ( neg_e )

);

//生成本地时钟50M

initial begin

clk = 0;

forever

#(CYCLE/2)

clk=~clk;

end

//产生复位信号

initial begin

rst_n = 1;

#2;

rst_n = 0;

#(CYCLE*RST_TIME);

rst_n = 1;

end

//输入信号din0赋值方式

initial begin

#1;

//赋初值

signal = 0;

#(10*CYCLE);

signal = 1;

#(3*CYCLE);

signal = 0;

#(2*CYCLE);

signal = 1;

#(5*CYCLE);

signal = 0;

#(4.5*CYCLE);

signal = 1;

#(5*CYCLE);

signal = 0;

#(4*CYCLE);

end

//开始赋值

endmodule

ref

https://blog.csdn.net/weixin_43343190/article/details/82961170?depth_1-utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-2&utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-2

最后

以上就是舒服毛巾最近收集整理的关于上升沿下降沿检测电路verilog及RTL仿真的全部内容,更多相关上升沿下降沿检测电路verilog及RTL仿真内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复