状态机的学习

- 状态机的概念

- 状态机的模型

- 状态机的设计

- 1.状态空间的定义

- 2.状态的跳转 (时序逻辑)

- 3.下个状态判断 (组合逻辑)

- 4.各个状态下的动作

状态机的概念

状态机,有限状态机(Finite State Machine,简称FSM)

在有限个状态之间按一定规律转换的时序电路。

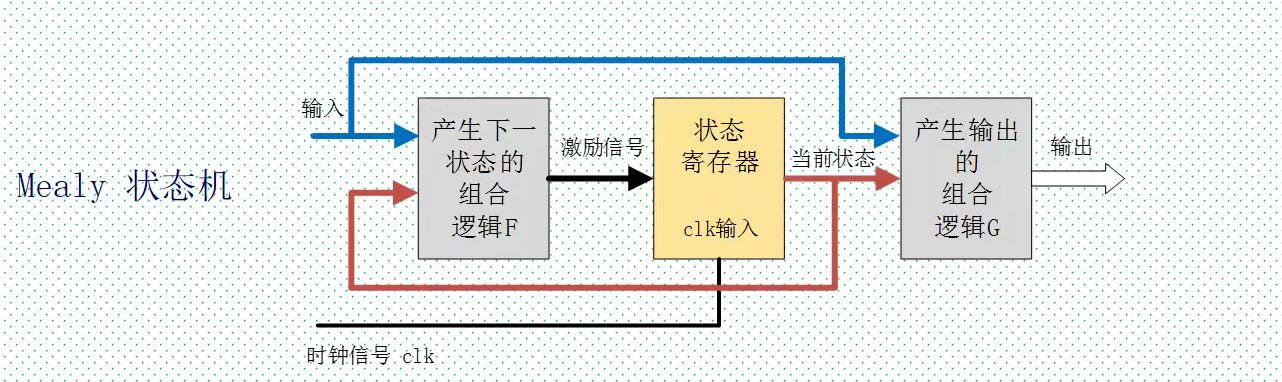

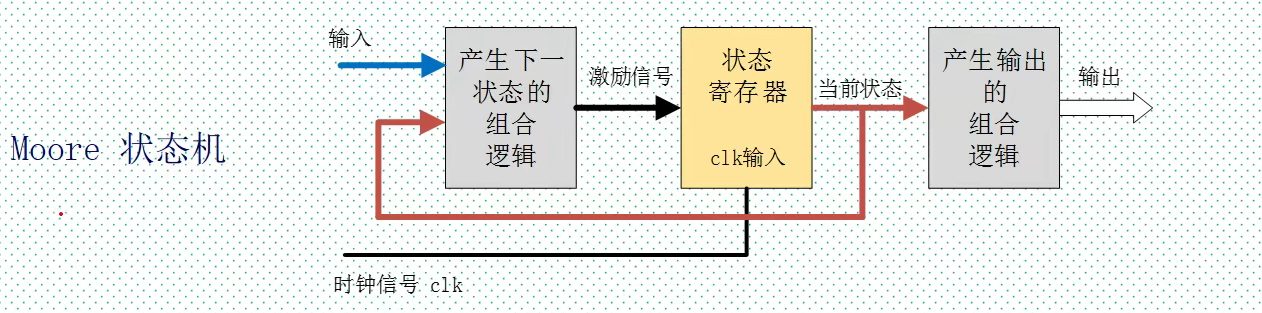

状态机的模型

状态寄存器由一组触发器组成,用来记忆状态机当前所处的状态,状态的改变只发生在时钟的跳变沿。状态是否改变、如何改变,取决于组合逻辑F的输出,F是当前状态和输入信号的函数。状态机的输出是由输出组合逻辑G提供的,G也是当前状态和输入信号的函数。

moore状态机跟Mealy状态机的区别在于输出只与当前状态有关。

状态机的设计

四段论:

状态空间定义

状态跳转

下一个状态判断

各个状态下的动作

1.状态空间的定义

// define state space

parameter SLEEP = 2'b00;

parameter STUDY = 2'b01;

parameter EAT = 2'b10;

parameter AMUSE = 2'b11;

//internal variable

reg [1:0] current_state;

reg [1:0] next_state;

状态空间定义了四种状态,用parameter来定义空间状态,定义了两个寄存器变量当前状态和下一状态。

另一种编码方式:

// define state space

parameter SLEEP = 4'b1000;

parameter STUDY = 4'b0100;

parameter EAT = 4'b0010;

parameter AMUSE = 4'b0001;

//internal variable

reg [3:0] current_state;

reg [3:0] next_state;

独热码:每个状态只有一个寄存器置位,译码逻辑简单。

2.状态的跳转 (时序逻辑)

// transition

always @(posedge clk or negdge rst_n) begin

if(!rst_n)

current_state <= SLEEP;

else

current_state <= next_state;

end

敏感列表:时钟信号以及复位信号边沿的组合。使用非阻塞赋值

3.下个状态判断 (组合逻辑)

//next state decision

always @(current state or input signals) begin

case (current_state)

SLEEP: begin

if(clock_alarm)

next_state = STUDY;

else

next_state = SLEEP;

end

SYUDY: begin

if (lunch_time)

next_state = EAT;

else

next_state = SYUDY;

end

EAT: ...;

AMUSE: ...;

default:...;

endcase

end

敏感信号表:所有的右边表达式中的变量以及if、case 条件中的变量,使用阻塞赋值。

4.各个状态下的动作

// action

wire read_book;

assign read_book = (current_state ==STUDY) ? 1'b1: 1'b0;

always @(current_state) begin

if(current_state == STUDY)

read_book = 1;

else

read_book = 0;

end

最后

以上就是还单身学姐最近收集整理的关于【FPGA基础快速入门2】状态机的学习状态机的概念状态机的模型状态机的设计的全部内容,更多相关【FPGA基础快速入门2】状态机内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复