大疆芯片开发岗A卷

文章目录

- 一、单选题

- 二、多选题

- 三、填空题

- 四、问答题

**说明:答案仅供参考,个别可能存在错误。**

一、单选题

1.下列关于多bit数据跨时钟域的处理思路,错误的有 A

A、发送方给出数据,接收方用本地时钟同步两拍再使用

B、发送方把数据写到异步fifo,接收方从异步fifo里读出

C、对于连续变化的信号,发送方转为格雷码发送,接收方收到后再转为二进制

D、发送方给出数据,发送方给出握手请求,接收方收到后回复,发送方撤销数据

解析:两级信号同步是处理单比特信号,而多比特数据可以用异步FIFO、格雷码、握手协议。

2.对12.918做无损定点化,需要的最小位宽是多少位,位宽选择11位时的量化误差是多少 C

A、12位,0.0118

B、13位,0.0039

C、12位,0.0039

D、13位,0.0118

解析:当小数点后第8位×2后结果为1.008,如果按0.008继续乘2下去,结果不可能得到1,这时只能进行“四舍五入”原则将1.008当做1。因此需要位宽为12bit。

当位宽为11bit时,转化的二进制数为1100.1110101=12.91406

量化误差:|12.91406-12.918|=0.00394。

3.两个噪声源的均方根噪声幅度分别是10uVrms, 5uVrms; 两个噪声源叠加后的均方根噪声幅度不可能是以下值中的哪个? B

A、11.18uVrms

B、2uVrms

C、5uVrms

D、14uVrms

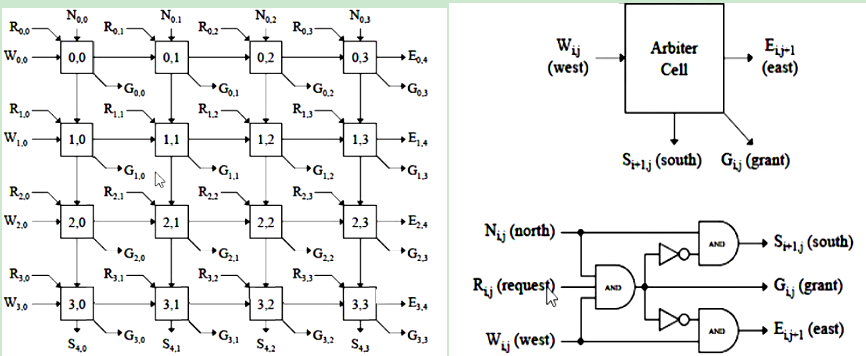

4.虑如下的4x4的“二维仲裁器”R00到R33为输入,G00到G33为输出,N和W也为输入,E和S也为输出,假设所有的逻辑门(包括非门/与门/反向器)延时都为1ns,请问该电路的最大延迟为D

A、23ns

B、25ns

C、19ns

D、21ns

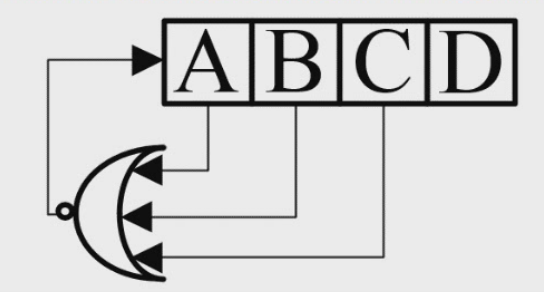

5.下图所示4bit右移位寄存器,0时刻ABCD初始状态为0111,请写出5个时刻之后的ABCD输出

A、1010

B、0100

C、1101

D、1110

解析:0111->0011->0001->0000->1000->0100(第五次移位值)。

6.1个16K x 8位的存储器,其地址线和数据线总和是 D

A、46

B、17

C、48

D、22

解析:16K=24+210=2^14,即需要14根地址线;8bit位宽需要8根数据线,一共需要22根线

7.数字系统中,采用( )可以将减法运算转化成为加法运算D

A、原码

B、BCD码

C、ASCII码

D、补码

8.关于流水线设计的理解,错误的是:A

A、流水线设计会消耗较多的组合逻辑资源

B、流水线设计会导致原有通路延时增加

C、流水线设计的思想,是使用面积换取速度

D、关键路径中插入流水线,能够提高系统时钟频率

解析:(流水线消耗了更多的寄存器资源(时序资源))(流水线为了使setup time更容易满足(原有通路延时降低),会降低系统时钟周期,增加系统的时钟频率;使用面积换取速度

9.在Verilog语言中如果a= 1"b1, b=3’b101, C= 1’b0,则{a,(3({c},b} =C

A、8’b10110101

B、7’b1011101

C、7’b1000101

D、8’b10001010

10.下面哪种逻辑门]可以实现逻辑( AXORB) OR (C AND D) ?A

A.、NAND

B、NOR

C、XOR

D、INV

11.关于DFT (design for test) 的描述错误的是:A

A、DFT测试不能覆盖电路的时序问题

B、DFT测试过程通常会消耗大量的动态功耗

C、DFT的主要目的是发现芯片在生产过程中出现的缺陷

D、寄存器扫描链是一种常用的DFT技术

解析:DFT的at-speed test会采用芯片PLL高速时钟进行寄存器的setup和hold测试

12.以下哪个工具不具备逻辑综合功能C

A、Synplify

B、Design Compiler

C、Modelsim

D、ISE

解析:Modelsim专业的仿真软件,时序和功能仿真,不具备逻辑综合功能

13.对芯片静态功耗影响最大是哪项D

A:、工作模式

B:、频率

C、负载

D、电压

解析: P=I*V

14.组合逻辑电路中的冒险是由于(D)引起的。

A、电路有多个输出

B.、电路未达到最简

C、逻辑门类型不同

D、电路中的时延

15.指令系统中程序控制类指令的功能是B

A、实现主存与CPU之间的数据传送

B、实现程序执行顺序的改变

C、实现算术和逻辑运算

D、实现堆栈操作

解析:程序控制类指令包括跳转指令,循环指令,子程序指令以及中断指令。这些指令可以控制程序的执行顺序

16.在对信号做降采样前添加滤波器,一般需要添加什么样的滤波器, 完成什么功能:D

A、高通,抗周期延拓

B、高通,抗混叠滤波

C、低通,抗周期延拓

D、低通,抗混叠滤波

17.假设一个cycle只能完成 个(8bits8bits) 或一个(17bits+ 17bits+ 17bits)操作,那么设计16bits16bits乘法最少可以多少个cycle完成C

A、2个cycles

B、4个cycles

C、3个cycles

D、1个cycle

18.下面哪项不是负反馈电路?C

A、电压串联反馈

B、电压并联反馈

C、电容并联反馈

D、电流串联反馈

解析:负反馈电路有四种:电压串联、电压并联、电流串联、电流并联

19.如下关于"线与”逻辑的描述,错误的是:B

A、可以用OC门来实现“线与”

B、“线与”逻辑必须在输出端加一个下拉电阻

C、“线与”逻辑是两个输出信号相连可以实现“与”的功能

D、可以用OD门来实现“线与"

解析: OD: open-drain,源级开漏输出(开漏),OC: open-collector,集电极开路。OD是对mos管而言,OC是对双极型管而言,两者实现线与需外加.上拉电阻

20.下列说法正确的是:(B)

A、乘法器在FPGA上必须使用DSP资源

B、基于SRAM的FPGA器件,每次上电之后必须重新进行配置

C、FPGA的ChipScope设置同样的采样深度,如果想一次观测更长时间的信号波形,可以将采样时钟换成更高频率的时钟

D、Source clock latency也属于FPGA IO接口约束

解析:乘法器是可以通过LUT实现的;片上逻辑分析仪观测和周期数有关,频率没关系;时钟延迟应该不是IO

二、多选题

1.关于异步处理,以下说法正确的是:AC

A、静态配置信号可以不做异步处理

B、异步FIFO采用格雷码的原因是为了提高电路速度

C、异步处理需要考虑发送和接收时钟之间的频率关系

D、单比特信号打两拍后可以避免亚稳态的发生

2.下面哪些是非易失性存储器AB

A、flash

B、EPROM

C、DRAM

D、SRAM

3.关于16点FF T描述正确的是BCD

A、每个蝶形算法需要1次复数加法

B、每级有8个蝶形算法

C、每个蝶形算法需要1次复数乘法

D、共有4级分解

解析:完成一个蝶形运算需要一次复数乘法和两次复数加法

4.Verilog语言中,下列哪些语句不可以被综合:BD

A、用generate语句产生的代码

B、initial语句块

C、always语句块

D、force语句

解析:always、generate、for、case、function、assign都是DUT代码中常用的可综合语句

5.在不增加pipeline的情况下,如何解决条critical path的setup时序不满足的问题ACD

A、使用更先进工艺的工艺库

B、在这条path.上插入寄存器

C、将部分组合逻辑电路搬移到前级path_上

D、降低时钟频率

解析:插入寄存器就是添加流水,违背题意;A为综合工具DC常用方法,B实际上就是pipeline,C可减小传播延时和组合逻辑延时和建立时间,D可加大时钟周期

6.下列关于代码覆盖率描述错误的是:AB

A、代码覆盖率达到百分之-百说明代码bug已消除

B、代码覆盖率包括功能覆盖率

C、代码覆盖率包括条件覆盖率

D、代码覆盖率包括语句覆盖率

解析:覆盖率是衡量设计验证完成程度的指标,并不是验证的目的。任何覆盖率达到100%并不代表芯片bug已消除。代码覆盖率包括行覆盖率、条件覆盖率、状态机覆盖率和翻转覆盖率。功能覆盖率反映开发出来的需要覆盖的功能点覆盖的比例。断言覆盖率测量断言被触发的频繁程度。

7.C程序中定义了一个全局数组,编译后此数组变量可能分配在下列哪个段:BC

A、text段

B、bss段

C、data段

D、stack段

解析:bss段用来存放未初始化的全局变量;data段用来存放已初始化的全局变量;堆栈用来存放局部变量;text段用来存放程序执行代码

8.下面电路中属于时序电路的是?ABD

A、寄存器

B、触发器

C、译码器

D、计数器

9.下列优化方法中哪些是速度优化方法:BC

A、资源共享

B、关键路径优化

C、流水线

D、串行化

解析:面积优化——资源共享、串行化;

速度优化——流水线、关键路径法,寄存器配平;

10.对于PSK和QAM调制,以下哪些说法是正确的:BCD

A、对于QAM调制,星座图的每个点的幅度相等

B、2PSK和4PSK在归-化条件下,其幅度都是1

C、4-QAM调制与QPSK的调制方式一致

D、在同样信道条件下,16-QAM的误码率大于4-QAM

PSK调制,星座图中的点都位于单位圆上,模相同(都为1),只有相位不同。而QAM调制星座图中的点不再位于单位圆.上,而是分布在复平面的一定范围内,各点如果模相同,则相位必不相同,如果相位相同则模必不相同。

三、填空题

1.write-back cache和write-through cache的区别: ( Write-back ) cache只在cache line被替代的时候把cache里的有效数据写下一级存储。

解析:Write-back(回写模式:在数据更新时只写入缓存Cache。只在数据被替换出缓存时,被修改的缓存数据才会被写到后端存储。此模式的优点是数据写入速度快,因为不需要写存储;缺点是一旦更新后的数据未被写入存储时出现系统掉电的情况,数据将无法找回。

2.正则表达式里可以使用计数符和通用字符集进行搜索匹配,这些计数符中,( * )号的意思是四配0个,1个或者多个,( + )号的意思是四配1个或者多个,( ? )号的意思是匹配0个或者1个

3.FPGA时序检查中对于异步复位电路的时序分析分别叫做( 恢复时间检查 )和 ( 移除时间检查 )。

4.并行计算是提高程序运行速度的关键,设a为并行计算部分的所占比例,n为并行处理的节点数,则并行计算带来的加速比为( 1/(a/n+1-a) )。

解析: S=(Ws+Wp )/(Ws+Wp/p),Ws 程序中的串行部分,Wp程序中的并行部分,PWs+Wp/p为并行的节点数。

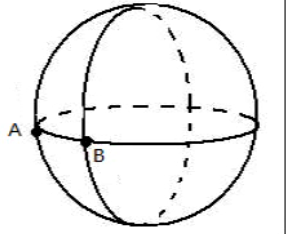

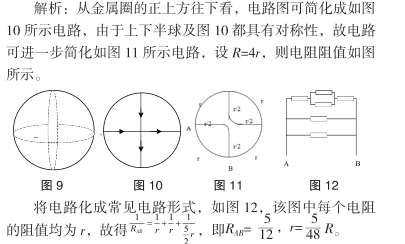

5.下图球框由三个相同的铁圈两两正相交组成,每个铁圈的电阻为均为R。AB两点间的电阻为( 5R/48 )。

四、问答题

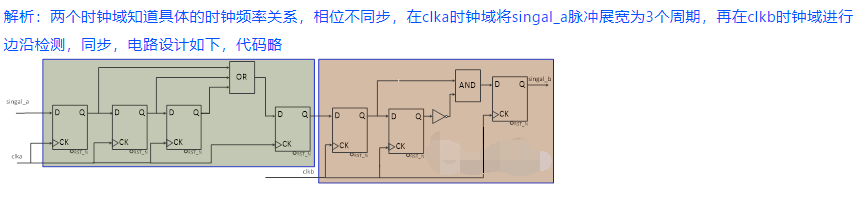

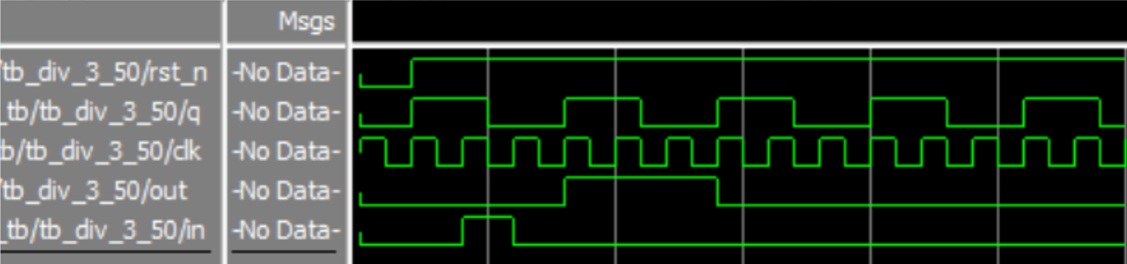

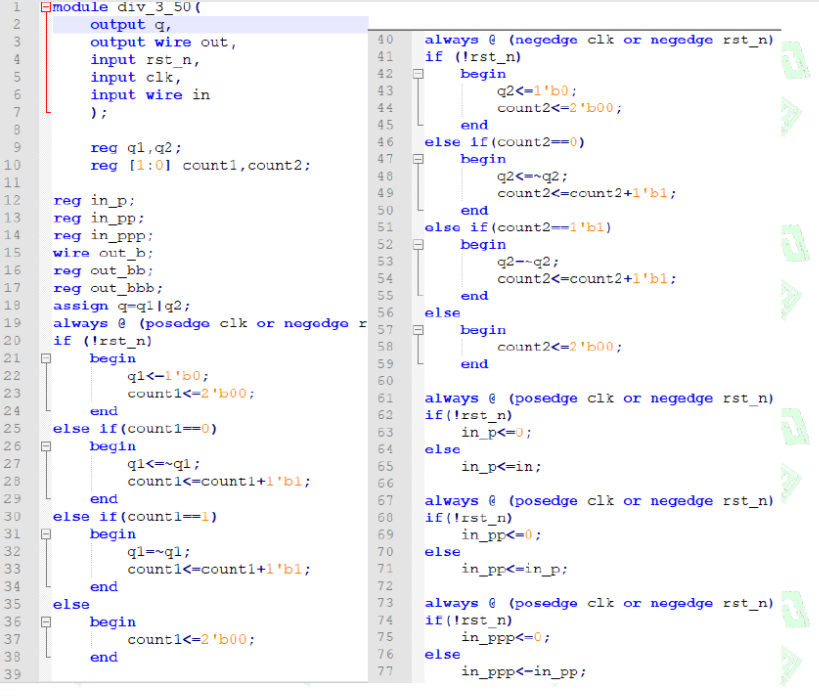

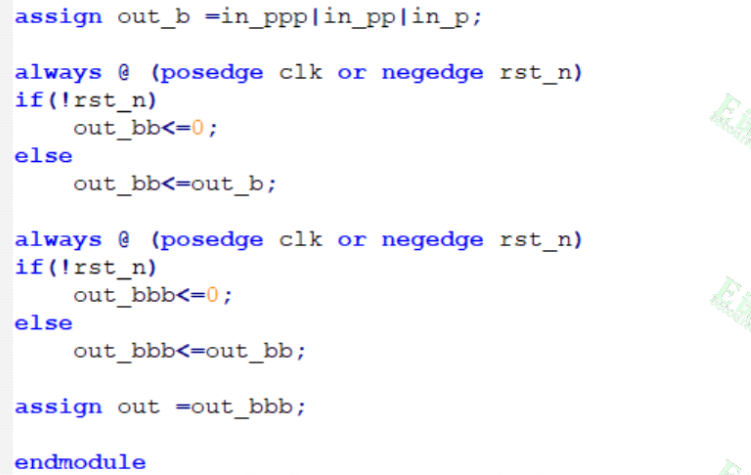

1.Signal_a是clka (300M) 时钟域的一个单时钟脉冲信号, 如何将其同步到时钟域clkb (100M) 中,并产生出Signal_b同步脉冲信号。请用Verilog代码描述,并画出对应的时序波形说明图。

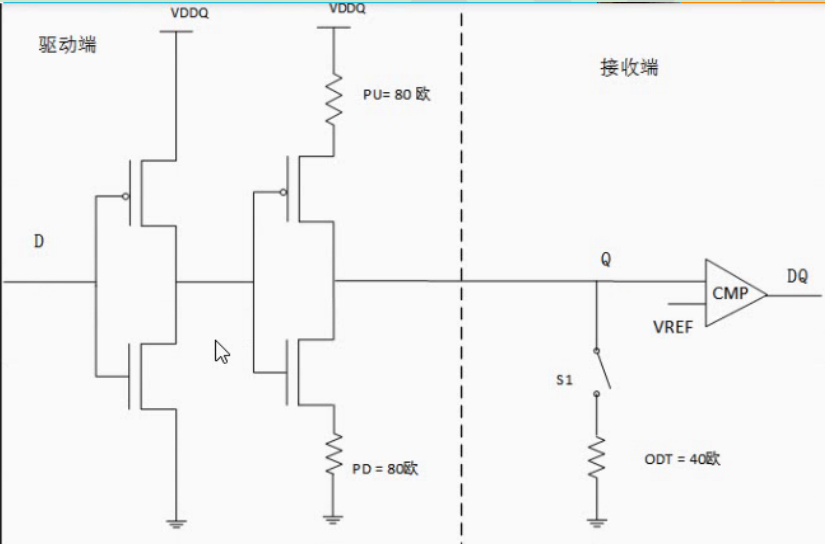

2.如下图,一个高速接口的端口电路示意图,要求D端发送数字0/1, DQ端收到相同的数字0/1. VREF电压为比较器数字输出0/1的判决电压。

(1) S1断开时,DQ端VREF电压需设置为?

(2) S1连通时,DQ端VREF电压需设置为?

(3)驱动端发送0时功耗较低,这句话是否正确?为什么?

备注: VREF电压是AD比较器判0或1的基准参考电压

答案:(1)S1断开的时候,若D为1,Q端电压为VDDQ,因此VREF要小于VDDQ。若D为0,Q端的电压为0,因此VREF要大于0,因此0<VREF<VDDQ

VDDQ

(2) S1连通时,若D为1,Q端电压为VDDQ/3,若D为0,Q端的电压为0,因此VREF要大于0,因此0<VREF<VDDQ/3

(3) 驱动端为0时,NMOS管导通,反相器输出接地,电阻没有电流,因此功耗较低。

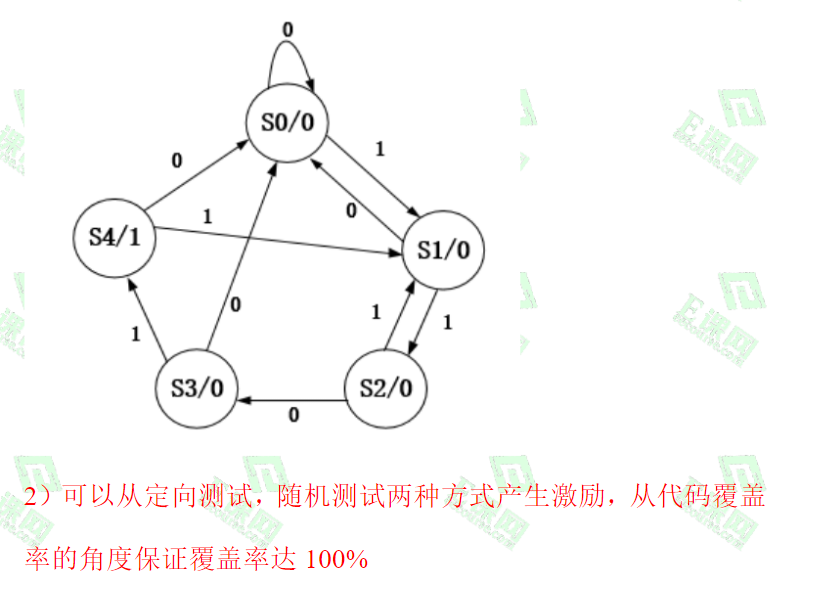

3.用moore型状态机实现序列"1101“从右到左的不重要检测。 (注:典型的状态机设计分为moore与mealy两大类,其中mealy状态机的输出不仅与当前状态值有关,而且与当前输入有关; moore状态机的输出仅与当前状态值有关,而与此时的输入无关)

1)请画出状态转移图,其中状态用S0,S1, S2…标识

2)针对这个具体设计如何衡量验证的完备性?

4.进行一个运算单元的电路设计, A[7: 0]* 1111011,请尽量用最少的资源来实现,写出对应的RTL代码

module mul (

input [7:0]A,

output [15:0]B) ;

wire [15:0] reg1 ;

wire [15:0] reg2;

wire [15:0] reg3;

assign reg1={A,{8{1'b0}}} ;

assign reg2={{6{1'b0}} ,A,{2{1'b0}}} ;

assign reg3={{8{1'b0}} ,A} ;

assign B = reg1-reg2-reg3;

endmodule

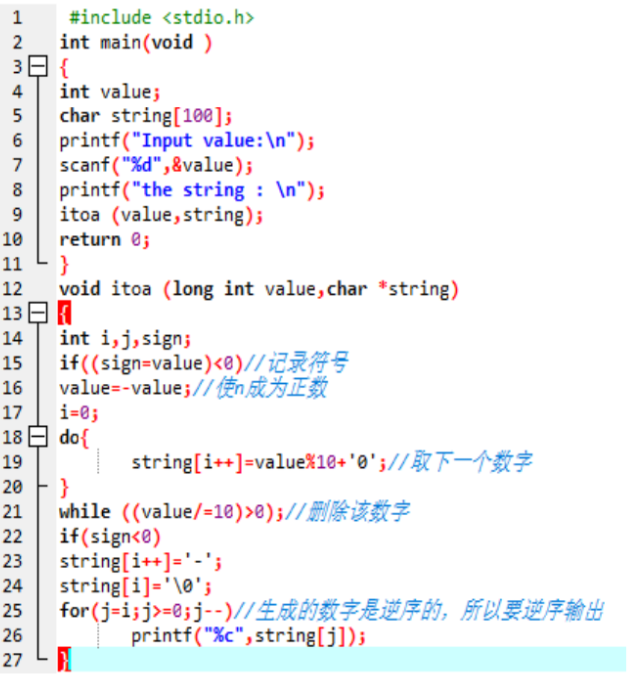

5.用C语言实现整数到ASCII码字符串的转换

void itoa(long int value,char *string) {

//value为一个int值, string是用来存放转换后的字符串的

}

最后

以上就是俭朴小刺猬最近收集整理的关于大疆FPGA/芯片开发工程师(A卷)笔试题(含详解)一、单选题二、多选题三、填空题四、问答题的全部内容,更多相关大疆FPGA/芯片开发工程师(A卷)笔试题(含详解)一、单选题二、多选题三、填空题四、问答题内容请搜索靠谱客的其他文章。

发表评论 取消回复