1,敏感变量的描述完备性

Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。如果在赋值表达式右端引用了敏感电平列表中没有列出的信号,在综合时将会为没有列出的信号隐含地产生一个透明锁存器。这是因为该信号的变化不会立刻引起所赋值的变化,而必须等到敏感电平列表中的某一个信号变化时,它的作用才表现出来,即相当于存在一个透明锁存器,把该信号的变化暂存起来,待敏感电平列表中的某一个 信号变化时再起作用,纯组合逻辑电路不可能作到这一点。综合器会发出警告。

例如:``

Example1

input a,b,c;

reg e,d;

always @(a or b or c)

begin

e=d&a&b; /*d没有在敏感电平列表中,d变化时e不会立刻变化,直到a,b,c中某一个变化*/

d=e |c;

end

Example2

input a,b,c;

reg e,d;

always @(a or b or c or d)

begin

e=d&a&b; /*d在敏感电平列表中,d变化时e立刻变化*/

d=e |c;

end

2,条件的描述完备性

如果if语句和case语句的条件描述不完备,也会造成不必要的锁存器。

Example1:

if (a==1'b1) q=1'b1;//如果a==1'b0,q=? q将保持原值不变,生成锁存器!

Example2:

if (a==1'b1) q=1'b1;

else q=1'b0;//q有明确的值。不会生成锁存器!

Example3:

reg[1:0] a,q;

....

case (a)

2'b00 : q=2'b00;

2'b01 : q=2'b11;//如果a==2'b10或a==2'b11,q=? q将保持原值不变,锁存器!

endcase

Example4:

reg[1:0] a,q;

....

case (a)

2'b00 : q=2'b00;

2'b01 : q=2'b11;

default: q=2'b00;//q有明确的值。不会生成锁存器!

endcase

Verilog中端口的描述

1,端口的位宽最好定义在I/O说明中,不要放在数据类型定义中;

Example1:

module test(addr,read,write,datain,dataout)

input[7:0] datain;

input[15:0] addr;

input read,write;

output[7:0] dataout; //要这样定义端口的位宽!

wire addr,read,write,datain;

reg dataout;

Example2:

module test(addr,read,write,datain,dataout)

input datain,addr,read,write;

output dataout;

wire[15:0] addr;

wire[7:0] datain;

wire read,write;

reg[7:0] dataout; //不要这样定义端口的位宽!!

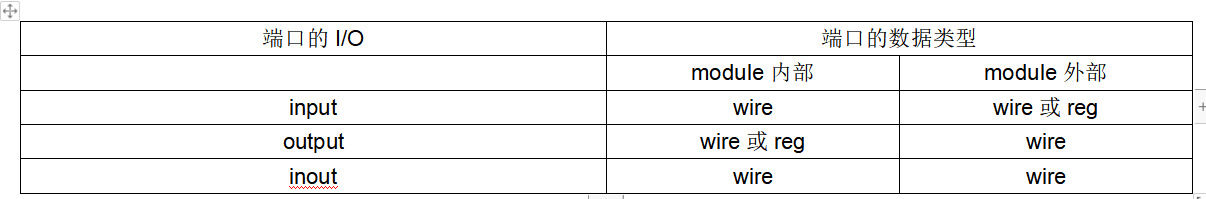

`2,端口的I/O与数据类型的关系:

assign语句的左端变量必须是wire;直接用"="给变量赋值时左端变量必须是reg!

Example:

assign a=b; //a必须被定义为wire!!

********

begin

a=b; //a必须被定义为reg!

end

例如A是INTEGER型,范围从0到255;B是STD_LOGIC_VECTOR,定义为8位。A累加到255时,再加1就一直保持255不变,不会自动反转到0,除非令其为0;而B累加到255时,再加1就会自动反转到0。所以在使用时要特别注意!

以触发器为例说明描述的规范性:

1,无置位/清零的时序逻辑

always @( posedge CLK)

begin

Q<=D;

end

2,有异步置位/清零的时序逻辑

异步置位/清零是与时钟无关的,当异步置位/清零信号到来时,触发器的输出立即 被置为1或0,不需要等到时钟沿到来才置位/清零。所以,必须要把置位/清零信号 列入always块的事件控制表达式。

always @( posedge CLK or negedge RESET)

begin

if (!RESET)

Q=0;

else

Q<=D;

end

3,有同步置位/清零的时序逻辑

同步置位/清零是指只有在时钟的有效跳变时刻置位/清零,才能使触发器的输出分 别转换为1或0。所以,不要把置位/清零信号列入always块的事件控制表达式。但是 必须在always块中首先检查置位/清零信号的电平。

always @( posedge CLK )

begin

if (!RESET)

Q=0;

else

Q<=D;

end

结构规范性

在整个芯片设计项目中,行为设计和结构设计的编码是最重要的一个步骤。 它对逻辑综合和布线结果、时序测定、校验能力、测试能力甚至产品支持 都有重要的影响。考虑到仿真器和真实的逻辑电路之间的差异,为了有效的。

先整理到这,下周的博客会记录编写仿真文件时的注意事项。这周没有时间了!!!

最后

以上就是坚定秀发最近收集整理的关于FPGA设计过程若干需要强调注意的关键点(敏感变量的描述完备性)的全部内容,更多相关FPGA设计过程若干需要强调注意内容请搜索靠谱客的其他文章。

发表评论 取消回复