看到标题了?时序(Timing)可以堪称现代电子回路设计的灵魂。在继续看这一节的时候,一定把之前的静态组合回路弄得了如指掌!过了上一关,才能进入这一关哦~~

何为时序?之前也说过一点,说白了就是世界上没有两个钟走时是一样准的道理一样的。这里就是由于MOS的制造工艺,电特性(阻容特性)乃至现代14nm级别的内部量子效应导致每个MOS管对应于输入和产生的输出之间有一定的时间差,并且和没有两块完全一样的MOS原理一样(没人能破这个,因为量子波函数支配这个世界,除非你能把量子力学推翻。。。),每块MOS间的传达时间的细小的差别(在1ps--picosec级别相当于10^(-12)秒 到 纳秒 级别)会在极高开关切换频率时产生极大的误差(过几节就能看到量的分析~)。大家有的时候看厂家的图纸一定有时序,有的时候一看一头雾水,那么看过这几节后,一定会了如指掌。

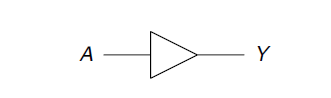

那么我们在设计的时候遇到了这种问题,怎么办。这就是大名鼎鼎的 时序分析 的数学工具了。。。又是数学 是的!一次学会,一生难忘!接下来我直接引进几个定义(开始如果一头雾水,没事继续看下去),以一个缓存--非“非”门

作为例子:

1.上升沿/下降沿:

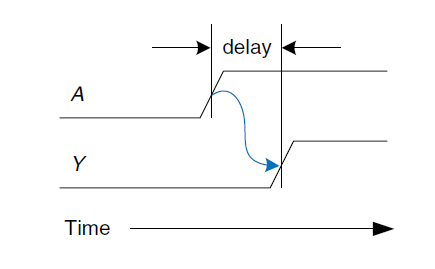

这里当输入A从0变为1时,输出Y在经过一段延迟(delay)之后也从0到1,我们定义从0(Low)到1(High)就是上升沿(raising edge),反之,。。。(自己想)叫做下降沿(falling edge)。注意我们我们测量延迟的起始时间,看图中的时间轴(Time),A是在变为1/2的时间点开始测量,直到Y变为1/2的时间点位置,这段时间被定义为延迟。(1/2其实根源很深,个人觉得是和模拟电路中3dB点有关,顺便一提,这一类的图都在描述电路的所谓 瞬态响应--transient response)

这里当输入A从0变为1时,输出Y在经过一段延迟(delay)之后也从0到1,我们定义从0(Low)到1(High)就是上升沿(raising edge),反之,。。。(自己想)叫做下降沿(falling edge)。注意我们我们测量延迟的起始时间,看图中的时间轴(Time),A是在变为1/2的时间点开始测量,直到Y变为1/2的时间点位置,这段时间被定义为延迟。(1/2其实根源很深,个人觉得是和模拟电路中3dB点有关,顺便一提,这一类的图都在描述电路的所谓 瞬态响应--transient response)

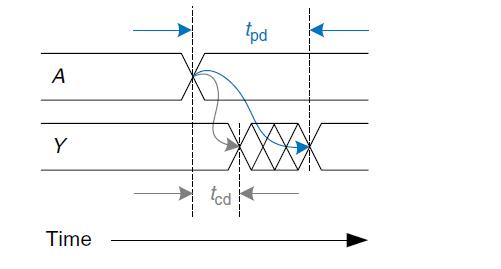

2.Tpd (传播延迟):当输入发生变化时,得到稳定输出的 最大 延迟时间(propagation delay)

3.Tcd (污染延迟): 当输入发生变化时,到刚刚影响输出的 最小 延迟时间(contamination delay)

见下图例:

。图中比如说输入A,有上下2根线,分别代表A从0到1变化和从1到0变化的两种情况,当然大部分情况下都是对称的,所以我们只看一根就行。这里两种延迟的测量方法和上面一样。蓝色箭头就是Tpd,灰色就是Tcd。注意Y中间那一段类似于震荡的形状表示在那段时间内,Y处于不稳定状态。

。图中比如说输入A,有上下2根线,分别代表A从0到1变化和从1到0变化的两种情况,当然大部分情况下都是对称的,所以我们只看一根就行。这里两种延迟的测量方法和上面一样。蓝色箭头就是Tpd,灰色就是Tcd。注意Y中间那一段类似于震荡的形状表示在那段时间内,Y处于不稳定状态。

Tcd和Tpd一般受物理影响,比如温度,多输出的非等时性,制造工艺等等。所以这个在厂家的手册会有记载的。

3.Critical Path(关键路径):从输入到输出经过逻辑门最多的线路。Short Path:从输入到输出经过逻辑门最少的线路。

这里2,3除了物理影响之外,由于我们本身就是在设计硬件,所以我们当然受2,3的限制。我们先看一下例子然后解释:

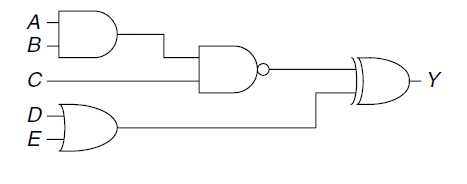

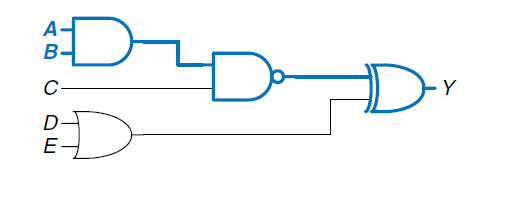

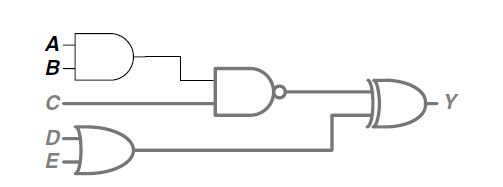

例:现在有如下组合逻辑回路:

,由定义给出Critical Path(下图蓝线)

,由定义给出Critical Path(下图蓝线)

。这时再看定义2,可知整个电路中Tpd相当于 关键路径 中 每个逻辑门的Tpd的叠加。 而下图则是Short Path:

。这时再看定义2,可知整个电路中Tpd相当于 关键路径 中 每个逻辑门的Tpd的叠加。 而下图则是Short Path:

所以整个电路中Tcd相当于 最短路径 中 每个逻辑门的Tcd的叠加。

所以整个电路中Tcd相当于 最短路径 中 每个逻辑门的Tcd的叠加。

好了讲到这里,我们进入动手时间~。

在上个例子中,假设根据特性手册所有的逻辑门都有Tcd= 60ps,Tpd = 100ps,求整个电路的Tcd和Tpd。。。。加法小学生都会~

转载于:https://blog.51cto.com/physic/1308243

最后

以上就是善良大树最近收集整理的关于1.8节 逻辑电路灵魂--时序的全部内容,更多相关1.8节内容请搜索靠谱客的其他文章。

发表评论 取消回复