导读:作者有幸在中国电子信息领域的排头兵院校“电子科技大学”攻读研究生期间,接触到前沿的数字IC验证知识,旁听到诸如华为海思、清华紫光、联发科技等业界顶尖集成电路相关企业面授课程,对数字IC验证有了一些知识积累和学习心得。为帮助想入门前端IC验证的朋友,思忱一二后,特开此专栏,以期花最短的时间,走最少的弯路,学最多的IC验证技术知识。

文章目录

- 一、专栏内容

- 1.1、概览版

- 1.2、详细版

- 二、专栏技术栈目标

- 三、数字IC的岗位介绍

- 四、专栏内容规划

- 五、学习要求 - “三多”

一、专栏内容

1.1、概览版

- ①、本专栏涵盖数字IC验证工程师必须掌握的核心理论和技能

- ②、Linux操作系统(shell)、gvim文本编辑工具(正则表达,快捷键)、EDA逻辑仿真工具

- ③、Verilog语言、SystemVerilog验证和UVM验证方法学

- ④、SoC芯片设计验证实践项目(MCU)

- ⑤、带随机的随机激励生成,覆盖率驱动的验证策略,逻辑仿真技术,调试技术,断言技术

- ⑥、应用所学验证理论和结论解决数字电路系统中的功能验证问题

1.2、详细版

- ①、本专栏涵盖数字IC验证工程师必须掌握的核心理论和技能

- ②、Linux操作系统(shell)、gvim文本编辑工具(正则表达,快捷键)、EDA逻辑仿真工具(Mentor-Questasim和Sysnopsys-VCS是重点)

- 主流EDA厂商及其工具

- Cadence: NC-Sim

- Mentor: Questasim(Modelsim升级版)

- synopsys: VCS

- 主流EDA厂商及其工具

- ③、Verilog语言、SystemVerilog验证和UVM验证方法学

- C/Matlab --(人工实现算法)–> RTL --(EDA工具实现)–> CMOS

- DUT:Design under Test

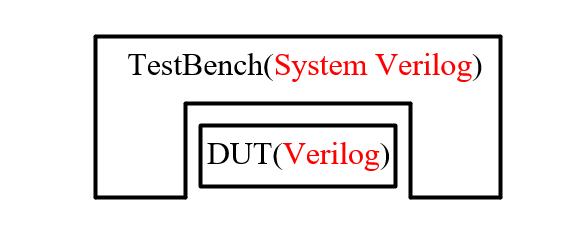

- 通常用Verilog去完成DUT的RTL代码编写,它会被综合成电路和门级网表,最终流片。需要知道的是,设计工程师编写的RTL代码很难保证逻辑功能是完全正确的,验证工程师就需要去描述各种工作场景,发送激励来验证他的行为是否满足预期!

- TOM:Time Of Market 上市时间

- TestBench(验证环境)结构,由DUT决定

- DUT简单,TestBench通常使用

FLatten结构 - DUT复杂、芯片迭代TOM(上市时间)要求高、Reusable(可重用)要求,TestBench通常使用

Hierarchical结构,由此也就有了验证方法学,汇总成了UVM(Universal Verification Methodology - 通用验证方法学)。

- DUT简单,TestBench通常使用

- ④、SoC芯片设计验证实践项目(MCU)

- ⑤、带随机的随机激励生成,覆盖率驱动的验证策略;逻辑仿真技术,调试技术,断言技术

-

“带随机的随机激励生成,覆盖率驱动的验证策略”:属于UVM验证方法学,在RTL设计时会详细介绍

-

“逻辑仿真技术”:针对简单的逻辑,使用诸如Questasim的EDA工具做一些仿真

-

“调试技术”:发现BUG,如何分析BUG,有些BUG是DUT的,有些可能是TestBench的。

-

“断言技术”:TestBench和DUT是上图所示的马蹄形结构,TestBench只能看到DUT的接口,如果要看DUT内部的信号,这个时候就可以使用断言技术了,查看内部行为与预期是否一致!

-

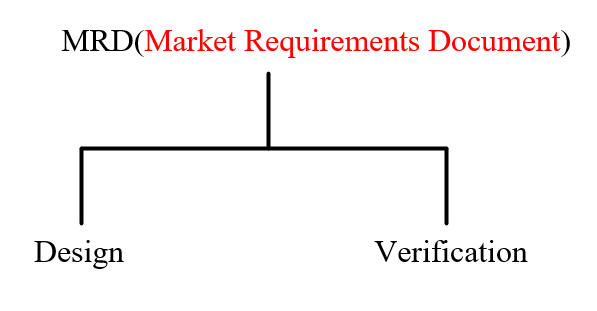

验证的核心:完备性

- I、Design:实现功能点

- II、Verification:验证功能点

- ①、理解所有的功能点

- ②、验证所有的功能点

-

使用随机激励原因:

- I、设计的功能点如果细分下来,可能有上百万之多,验证此时无法做到一一覆盖,此时就有了随机激励的方法学。该种方法,以时间换空间,每天都不停的跑,但是每次跑的用例发出的激励都是不一样的。通过随机种子与时间相关联,时间不一样,随机种子不一样,随机激励不一样。

- II、使用随机激励,这样人为分析遗漏的地方也可能被涉及到!

-

使用覆盖率驱动原因:

- I、激励随机生成发送,那么我的验证达到什么程度才算验证完成?这时就有了:覆盖率驱动。前面灌激励随机,后面收集结果看覆盖率。看验的那些点,是否通过随机给覆盖到了。

- II、覆盖率分类:

- ①、功能覆盖率:看功能点是否达到。

- ②、代码覆盖率:通过工具分析,激励是否把代码的每一行,每一个分支及其组合都给覆盖到了。【行覆盖、条件覆盖、Toggle覆盖】

-

- ⑥、应用所学验证理论和结论解决数字电路系统中的功能验证问题

二、专栏技术栈目标

- 熟练使用Linux操作系统

- 熟练使用gvim文本编辑工具

- 熟悉使用EDA逻辑仿真工具Questasim和VCS

- 熟练掌握经典数字电路的Verilog RTL设计

- 熟练掌握System Verilog验证语言

- 熟练掌握UVM验证方法学

- 熟练掌握SoC芯片架构、应用场景和数据流向

- 熟练掌握AHB-SRAM/AHB-SD-Host/APB-SPI的验证流程、验证方法、验证重点和难点

- 掌握带约束的随机化验证策略和覆盖率驱动的验证策略

三、数字IC的岗位介绍

- 前端(RTL逻辑实现)

- 设计

- 验证(功能验证)

- EDA仿真验证(验证主流,本专栏重点)

- FPGA原型验证(系统级验证)

- 后端(RTL逻辑转化为netlist)

- BES(综合和timing)

- DFX(DFT针对制造缺陷,仅作测试;DFX除了制造,还有功能需要调试,也会在DFX设计中考虑)

注:对于前端而言,后续提升途径有:

- I、技术角度可走:架构工程师、系统工程师

- II、管理角度可走:验证Leader、项目经理、部门经理

四、专栏内容规划

-

数字IC验证工程师基础理论和技能

- LInux操作系统

- Gvim文本编辑工具

- 经典数字电路的Verilog RTL设计

- 逻辑仿真工具QuestaSim、VCS

-

SystemVerilog验证语言

- Questasim(VCS) + Labs(实验)

-

UVM验证方法学

- VCS + Labs(实验)

五、学习要求 - “三多”

- 多写代码

- 多做仿真

- 多做练习

最后

以上就是犹豫白猫最近收集整理的关于【数字IC验证快速入门】1、浅谈数字IC验证,了解专栏内容,明确学习目标的全部内容,更多相关【数字IC验证快速入门】1、浅谈数字IC验证内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复