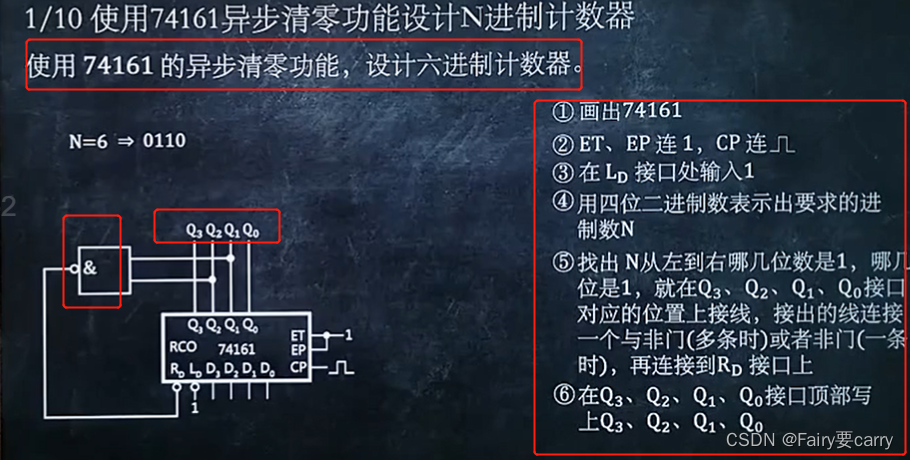

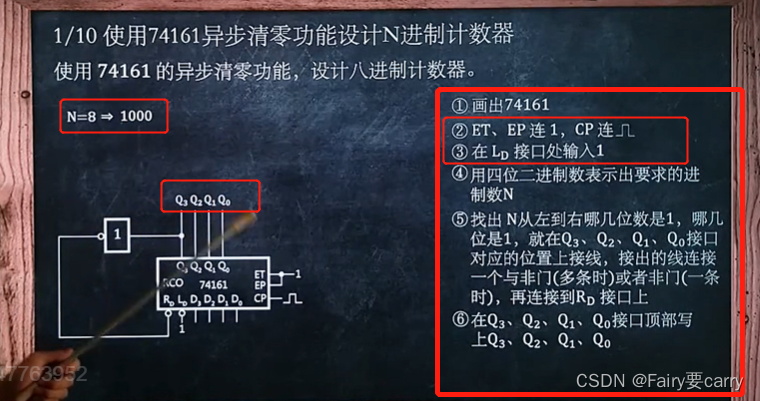

LD接口处为1,ET,EP连1,CP连欧

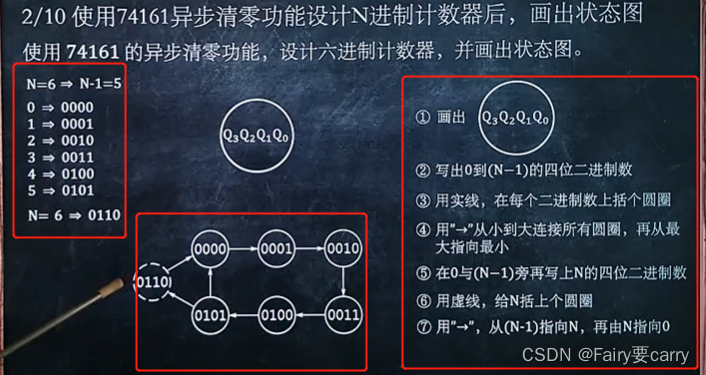

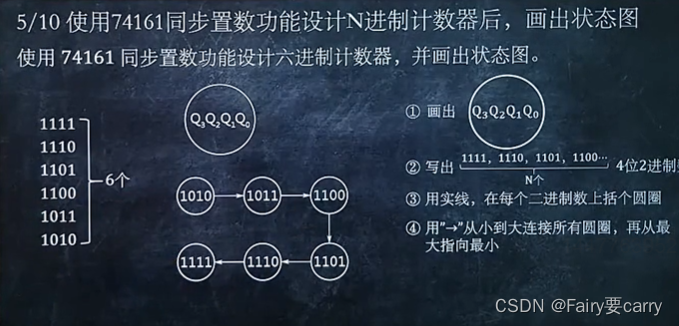

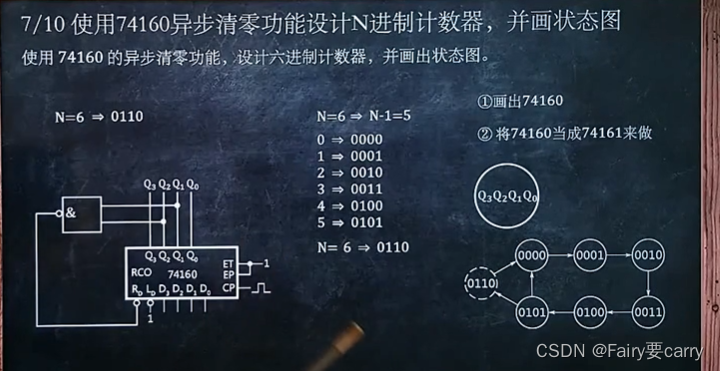

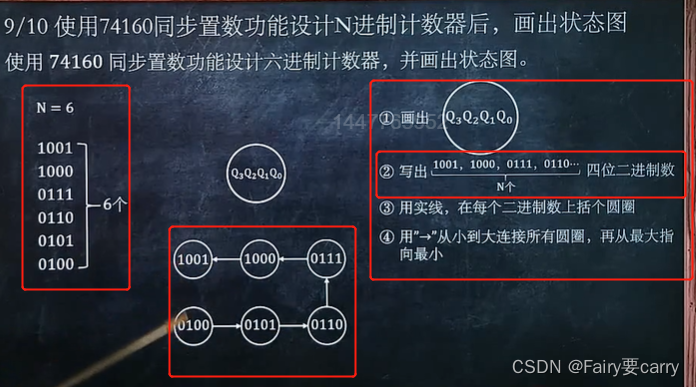

看是几进制计数器,6,得到0-5的二进制数,从小到大连起来,然后得到6的二进制,指向最小值

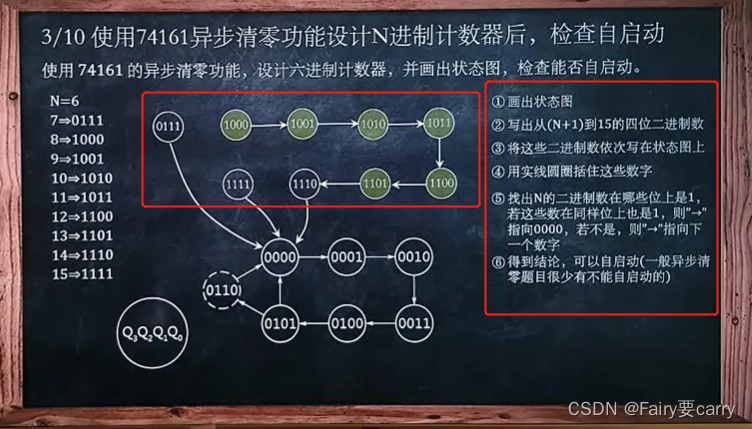

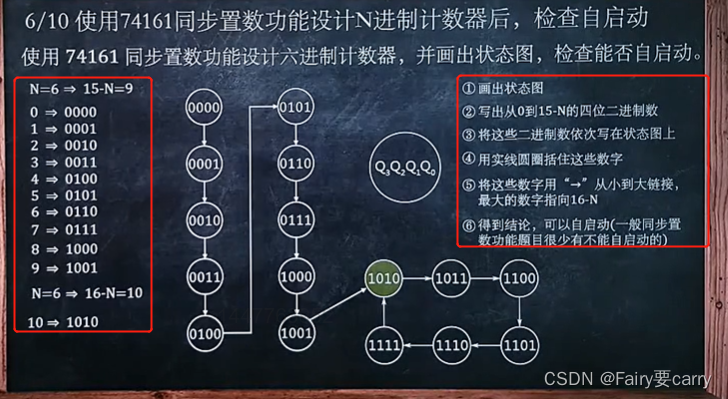

检查自启动

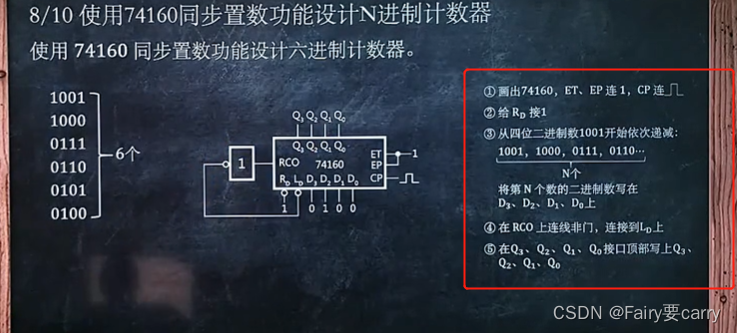

设计N进制计数器

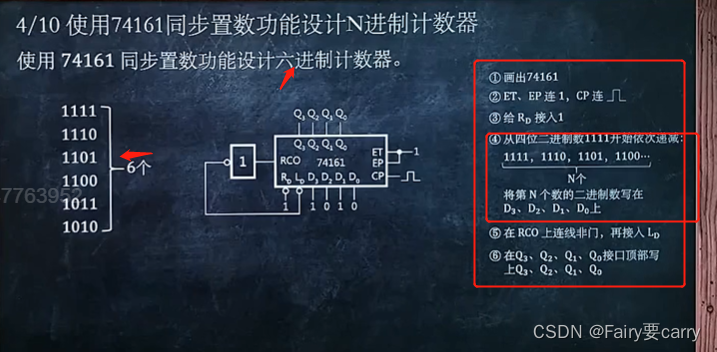

找是几进制器,然后1111向下递减n就行,放到D上

同步置数功能设计N进制器,需要从最高1111往下减N

同步自启动,是0到15-N,异步是N+1到15;然后画出两个状态图连起来

ET、EP接1,CP接欧,Q3,Q2,Q1,Q0接上面,D3,D2,D1,D0,Ld,Rd为结果;

0110为六进制,12位置为1所以两根线接与非门

同步设计进制器,需要把结果写在D上;异步的话是在Q上

并且同步Rd接1,Ld接与非与RCO,从1001开始递减,寻找第N个

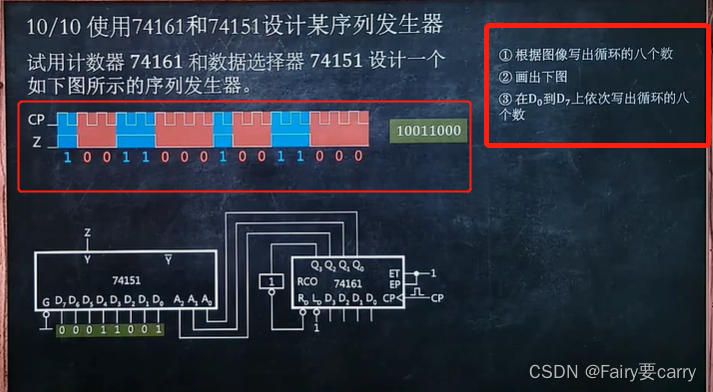

设计某序列发生器

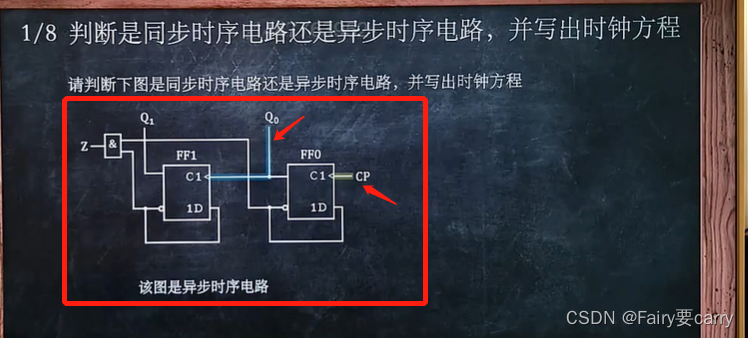

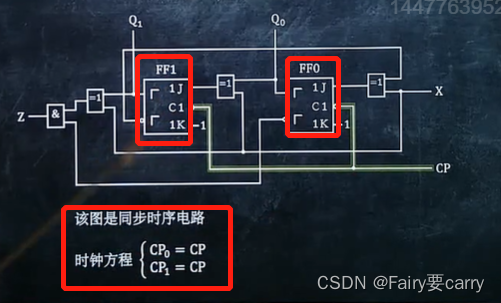

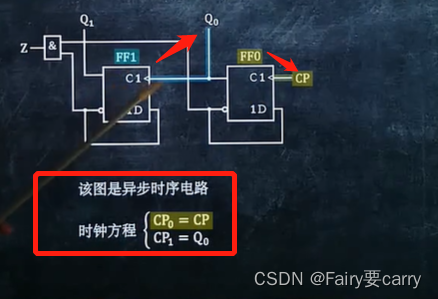

时序逻辑电路

看c1接的位置是否相同,相同就是同步时序电路

时钟方程:

看连接的地方,都是cp,所以方程等于cp

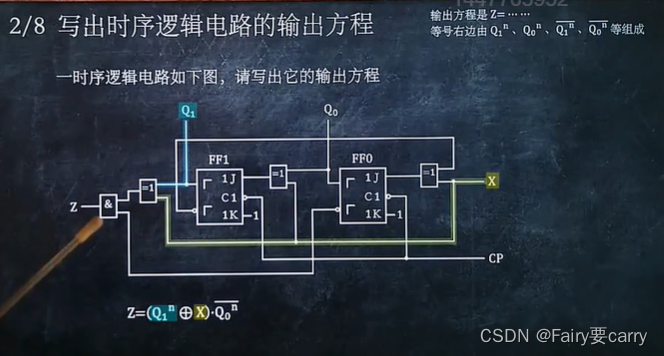

输出方程

主要判断Z的电路,注意JK输入输出是相反的比如FF0就是JK,所以输入为Q0N非,N代表当前Q状态

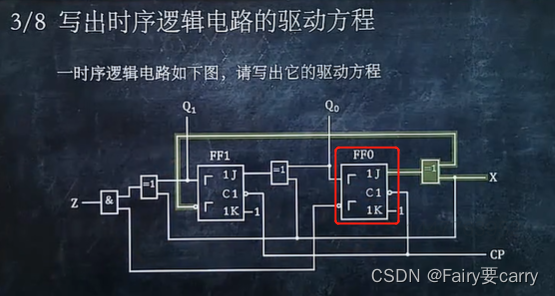

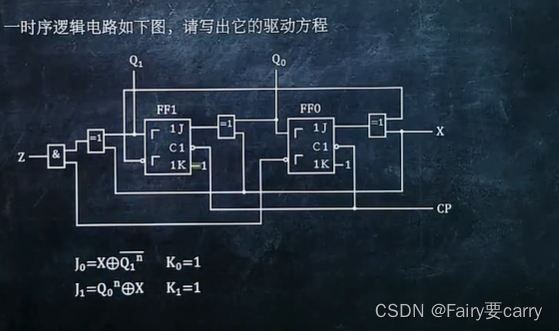

驱动方程:

可以看出0触发器一个连接x,一个连接Q1非——>因为FF1是JK,输出是Q1,所以输入为Q1非

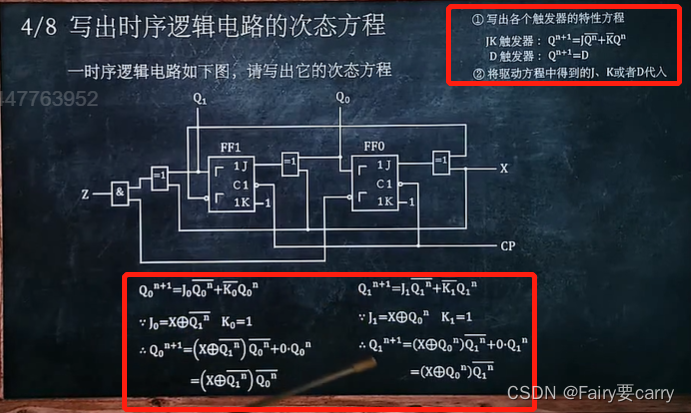

次态方程

次态方程需要结合驱动方程中JK的值;

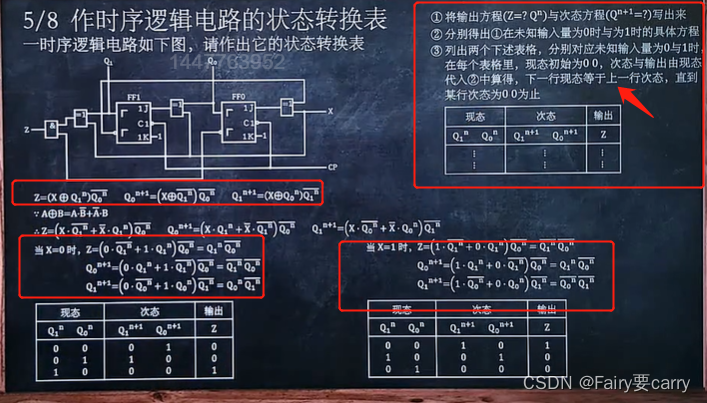

状态转换表

先得到状态转换表,根据状态转换表(Q和Z的值),带入Q的值(现态),得到次态Qn的值,得到输出Z的值;

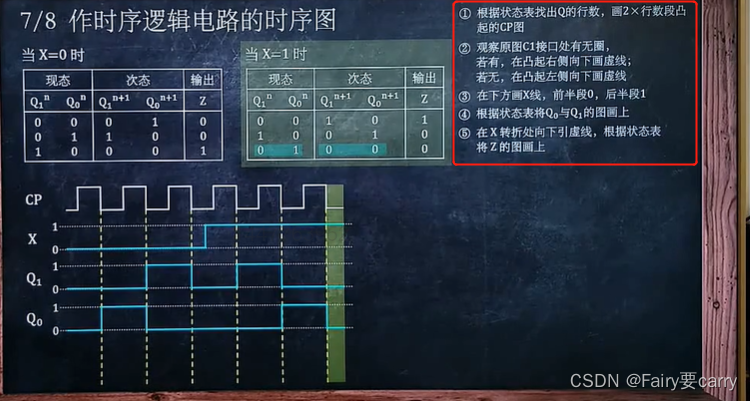

时序图

有圈,所以cp右侧画虚线

先要得到状态转换表,也就是Q1n+1和Q0n+1,然后还有Z,Qn+1=JK,带入Q的初始值

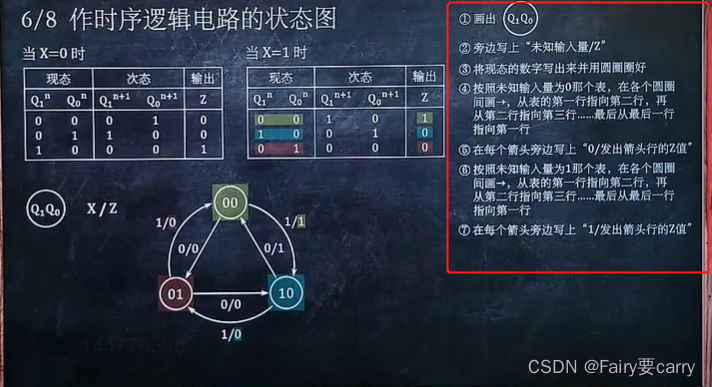

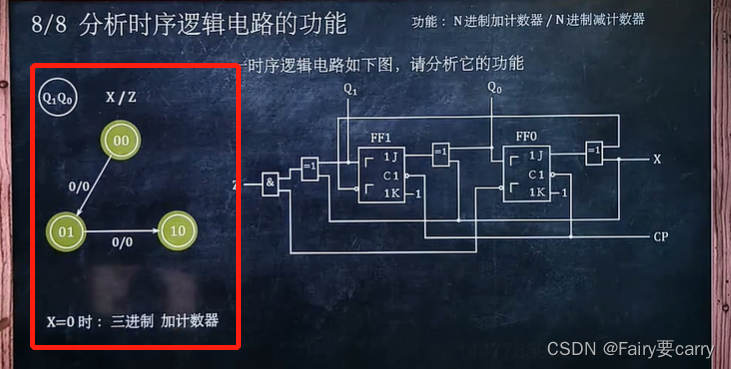

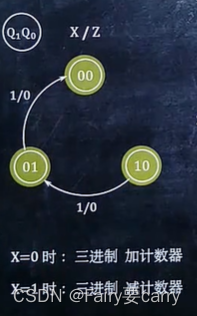

分析时序逻辑电路的功能

先得到状态图

看它的图有几个然后是几进制器

0时,指的里面,可以得到是递增的

1时,指的是外面可以发现是递减的

最后

以上就是自觉丝袜最近收集整理的关于计数器集成芯片+分析时序逻辑电路的全部内容,更多相关计数器集成芯片+分析时序逻辑电路内容请搜索靠谱客的其他文章。

发表评论 取消回复