我理解这个D触发正常运转要满足四个约束,第一个是建立时间,第二个是保持时间,第三个是对于最后一个传输门的关断时间的控制,第四个是时钟周期 约束。

建立时间约束和保持时间和保持时间约束是使触发器能够正常采集新的数据信号D,时钟周期约束是使数据信号能够正常的传播给下一级触发器。

我们把D触发器的前一个锁存器(或者叫双稳态电路,就是前一个环形电路)叫做D触发器的采集部分,把D触发器的后一个锁存器(或者叫双稳态电路,就是后一个环形电路)叫做D触发器的传播部分。

建立时间约束

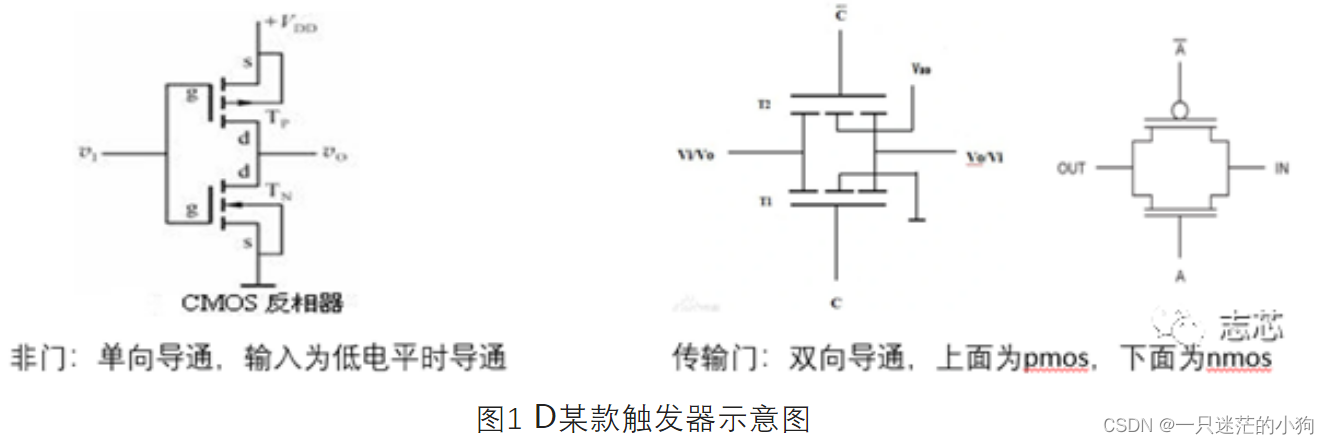

假设CLK的初始状态为0,从左往右,此时第一个传输门导通,第二个传输门关闭,第三个传输门关闭,第四个传输门导通。

此时D触发器的采集部分信号走向为:D -> a -> b -> c -> d 。从以上信号走向可以看出,信号必须在CLK上升沿到来之前在d点保持稳定,否则如果在这之前D pin的信号发生变化,就会导致DFF锁住错误的信号。换句话说,如果假设路径1需要花费的时间为t0,那么D处的信号必须要在CLK上升沿之前的t0或更早的时间内保持稳定。此即setup的物理意义,也是timing report种library setup time所代表的含义。

为什么在建立阶段,信号需要传播到d点,而不是a点或b点或c点呢?因为反相器的导通靠的是栅极衬底之间的电势差在衬底表面形成一层反型层来导电。以pmos为例,衬底是N阱,衬底表面的反型层p型层,但是其实衬底表面的空穴(带正电)和衬底里面的电子(多子,带负点)一直存在对向运动(这种运动是不是叫湮没?一次消灭一对导电粒子)(运动能量来源一是二者之前天然电势差形成的静电能);在反向器输入端有电流输入时,可以不断的提供静电位能使得衬底上的反型层保持一定的粒子浓度进行导电;当反相器输入电流突然消失,没有持续的电位能维持反型层的存在,那么此时反相器的导电性只能维持一个很短的时间;另外反相器此时的输入电流在导线(有电阻,会做功)上不断耗散,可能电流都传不到下一个反相器;所以数据信号必须传播到d点。

此时D触发器的传播部分信号走向为:h->e->f->g->h。后一个环形电路导通,使得触发器输出端Q一直是一个稳定态。

2、保持时间约束

当CLK从0变成1后,从左往右,此时第一个传输门关闭,第二个传输门导通,第三个传输门导通,第四个传输门关闭。

此时信号走向为d -> a -> -> b -> e -> f(Q) -> g -> h。需要注意的是,当信号从0变为1的过程中,在一段很短的时间内,所有传输门都可能导通,若此时D端信号发生变化而CLK的transition比较慢,则会发生新值覆盖旧值而导致信号错误的现象。因此,D段信号需要在传输门完成开/关过程中保持稳定,此即为hold的物理意义,也是timing report中library hold time代表的含义。

为什么CLK从0变为1后,d->a->b->c->d环形电路可以保持呢(传输过程中间肯定有能量耗散)?是不是因为每次传导到传输门之后,电源网络又重新给反相器的栅衬电容充电,所以让能量又起来了?

3、对于最后一个传输门的关断时间的控制

在信号从d传输到f(Q的)过程中, e点和f点之间的反相器的栅漏电容的逐步变小(电荷在释放)导致输入电流逐渐截止;如果第四个传输门(从左往右)关闭的过早,那么可能导致Q端的输出为高阻态,为了防止这种情况出现,最后一个传输门不能过早关断。

4、时钟周期约束

时钟上升沿到达后至少要保证数据信号从d点传播到h点,中间的delay为 t1的话,那么时钟周期应该≥2t1.

最后

以上就是孝顺歌曲最近收集整理的关于D触发器的建立时间和保持时间物理含义探讨的全部内容,更多相关D触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复