FPGA D触发器实验

实验目的

(1)熟悉Quatus18.1的软件应用

(2)熟悉ip核的调用

(3)掌握D触发器的逻辑功能和触发方式

实验环境

Quartus Prime 18.1标准版

Cyclone IV EP4CE6F17C8

测试工具:Signal Tap、In-Systeam Source and Probes Editor

实验原理

1)系统原理

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。触发器具有两个稳定状态,即"0"和"1",

D触发器触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

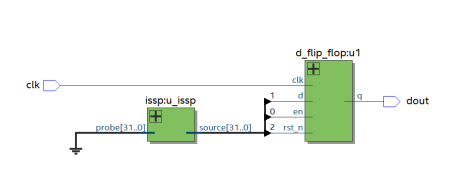

2)电路原理图

定义输入信号:d;

定义使能输入信号:en;

定义输出信号:q和q_n;

其中调用ip核得到的RTL视图如下:

3)代码实现

模块代码:

module d_flip_flop(

input

clk

,

input

rst_n

,

input

d

,

input

en

,

output

q

,

output

q_n

);

reg q_out;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

q_out <= 1'b0;

end

else if(en)begin

q_out <= d;

end

end

assign q = q_out;

assign q_n = ~q_out;

endmodule

顶层文件代码:

module dff_top(

input

clk

,

output dout

);

wire

rst_n

;

wire

din

;

wire

en

;

wire

q

;

wire

q_n

;

wire [3:0] probe ;

d_flip_flop u1(

.clk

(clk ),

.rst_n (rst_n),

.d

(din ),

.en

(en ),

.q

(q

),

.q_n

(q_n )

);

issp u_issp(

.source ({rst_n,din,en}),

.probe (probe)

);

assign dout = q;

endmodule

4)测试结果

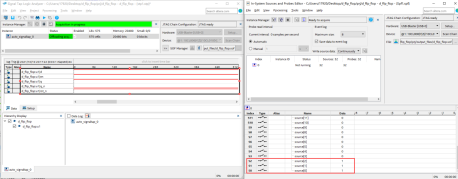

打开In-Systeam Source and Probes Editor测试软件。

其中的source[0]对应是使能信号en;

其中的source[1]对应是输入信号din;

其中的source[2]对应是复位按键rst_n;

而后,我们将使能信号en、输入信号din、复位按键rst_n都置为1时,d触发器q的输出也为1.如下图:

最后

以上就是妩媚灰狼最近收集整理的关于FPGA D触发器实验FPGA D触发器实验的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复