基本RS触发器设计

- 实验目的

- 实验要求

- 实验原理

- 程序代码

- 测试用例

- 仿真波形图

- 电路管脚图

- 引脚配置文件

- 工程文件

实验目的

- 学习基本RS触发器的原理与设计方法;

- 掌握灵活运用Verilog HDL语言进行各种描述与建模的技巧和方法。

实验要求

- 使用合适的或者你喜欢的描述方式来实现基本RS触发器;当RS=11时,选择输出00或11中的一种输出组合。

- 课前任务:在Xilinx ISE上完成创建工程、编辑程序源代码、编程、综合、仿真、验证,确保逻辑正确性。

- 实验室任务:配置管脚,将输入R和S连接到2个开关上,将输出Q和Q#连接到2个LED灯。生成*.bit文件,完成板级验证。

- 撰写实验报告。

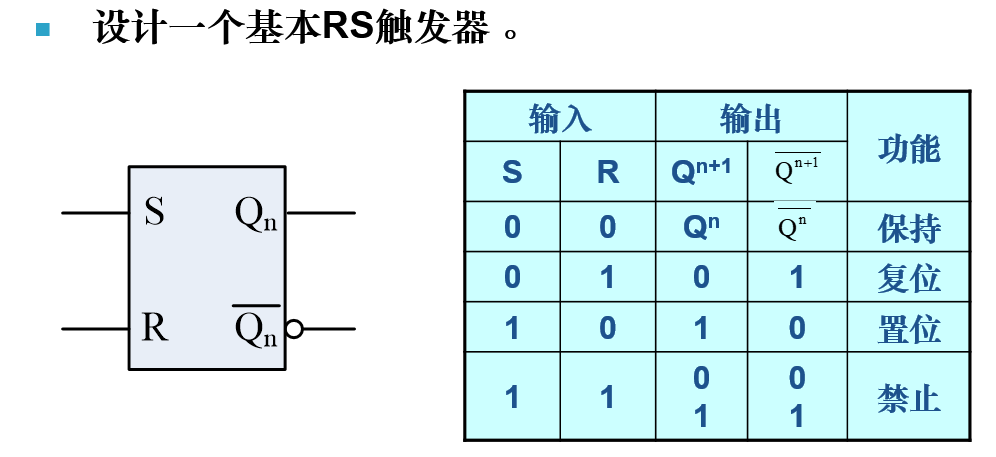

实验原理

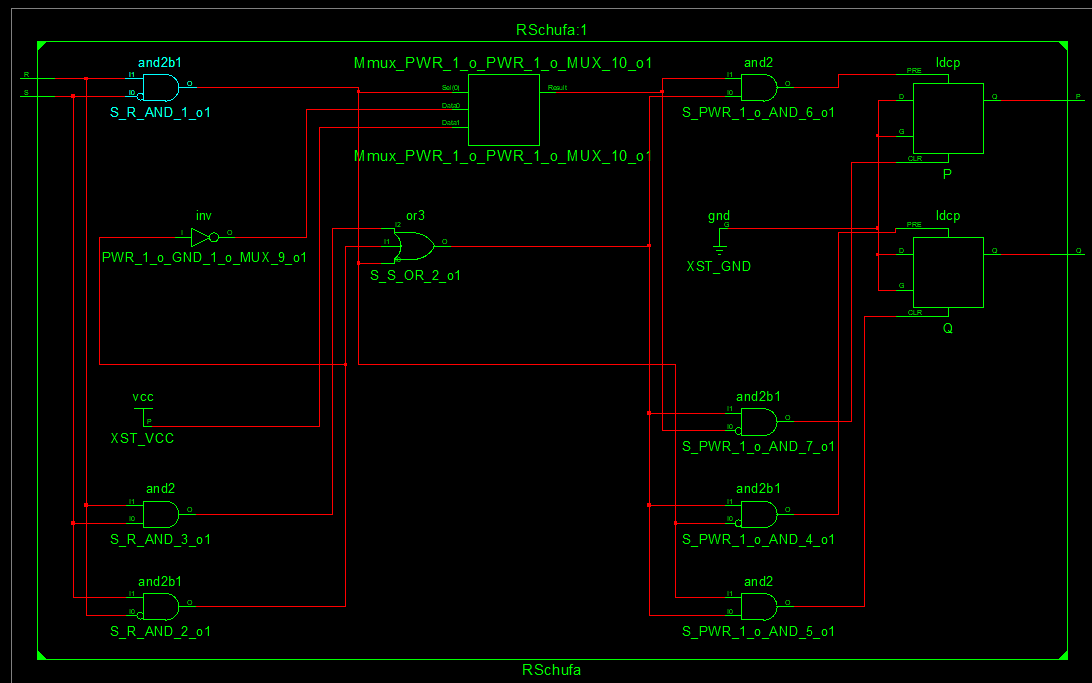

程序代码

module RSchufa(S,R,Q,P);

input S,R;

output reg P,Q;

always @(*)

if((~S)&R)begin Q=0;P=1;end

else if(S&(~R))begin Q=1;P=0;end

else if(S&R) begin P=1;Q=1;end

endmodule

测试用例

initial begin

R=1;S=0;

#100;

R=0;S=1;

#100;

R=0;S=0;

#100;

R=1;S=1;

#100;

R=1;S=0;

#100;

R=0;S=0;

#100;

R=0;S=1;

#100;

end

endmodule

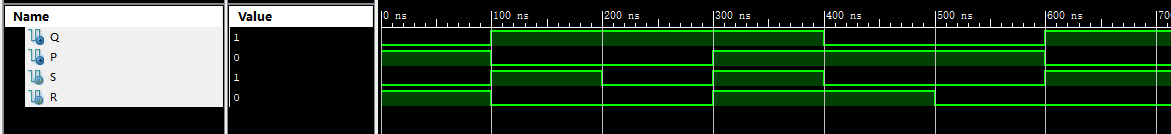

仿真波形图

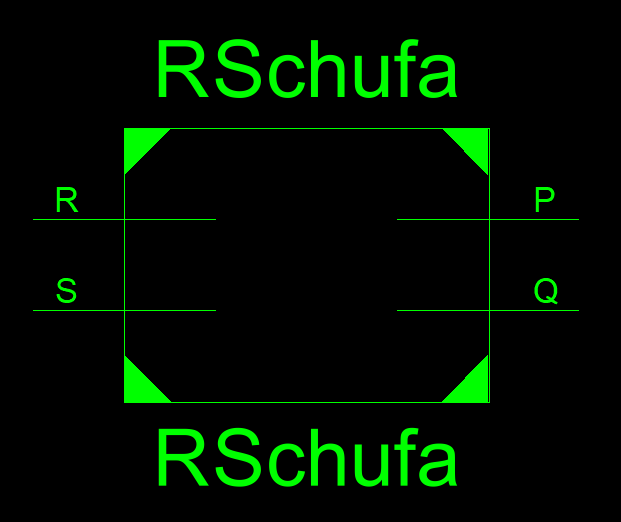

电路管脚图

引脚配置文件

NET "R" LOC = T3;

NET "S" LOC = U3;

NET "P" LOC = P2;

NET "Q" LOC = R1;

NET "P" IOSTANDARD = LVCMOS18;

NET "Q" IOSTANDARD = LVCMOS18;

NET "R" IOSTANDARD = LVCMOS18;

NET "S" IOSTANDARD = LVCMOS18;

NET "R" PULLDOWN;

NET "S" PULLDOWN;

工程文件

工程文件: 基本RS触发器设计实验.

最后

以上就是贪玩航空最近收集整理的关于杭电数字电路课程设计-实验八-基本RS触发器设计实验的全部内容,更多相关杭电数字电路课程设计-实验八-基本RS触发器设计实验内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复