杭电计算机组成原理寄存器堆设计实验4

杭电计算机组成原理寄存器堆设计实验4

(5页)

本资源提供全文预览,点击全文预览即可全文预览,如果喜欢文档就下载吧,查找使用更方便哦!

9.9 积分

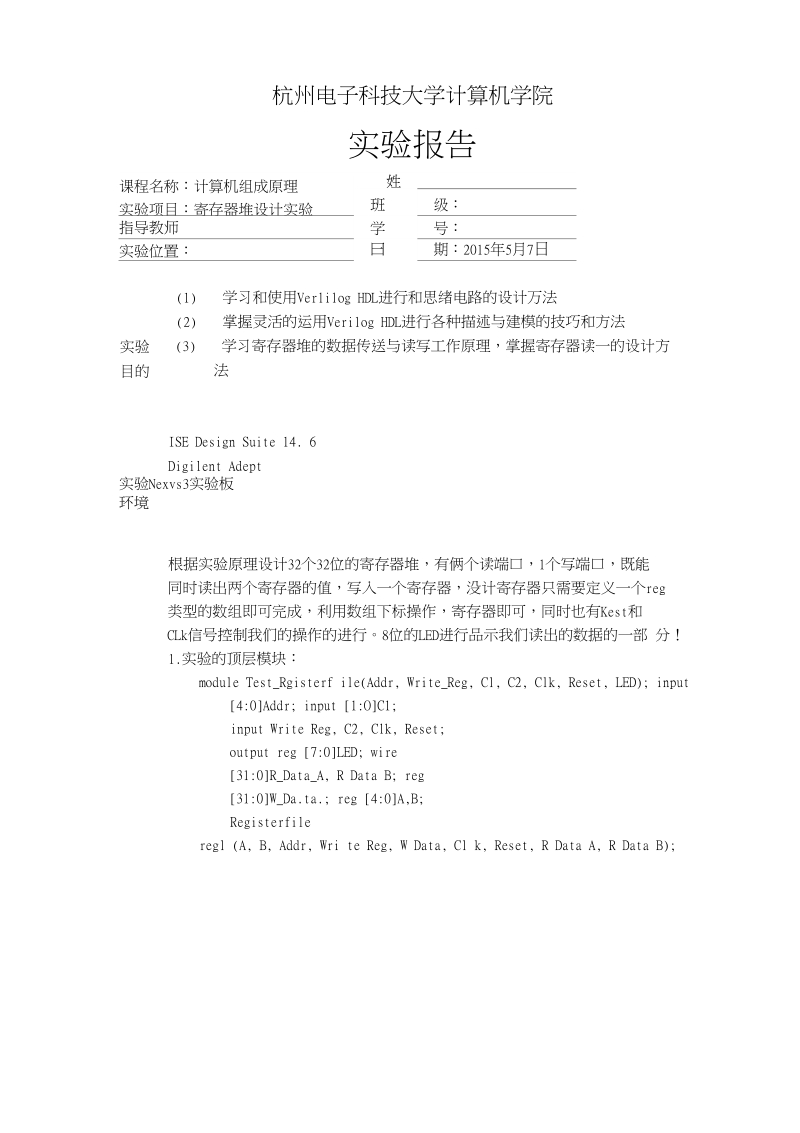

杭州电子科技大学计算机学院实验报告课程名称:计算机组成原理 实验项目:寄存器堆设计实验姓班级:指导教师学号:实验位置:曰期:2015年5月7日(1) 学习和使用Verlilog HDL进行和思绪电路的设计万法(2) 掌握灵活的运用Verilog HDL进行各种描述与建模的技巧和方法实验目的(3) 学习寄存器堆的数据传送与读写工作原理,掌握寄存器读一的设计方 法ISE Design Suite 14. 6Digilent Adept实验Nexvs3实验板 环境根据实验原理设计32个32位的寄存器堆,有俩个读端口,1个写端口,既能 同时读出两个寄存器的值,写入一个寄存器,没计寄存器只需要定义一个reg 类型的数组即可完成,利用数组下标操作,寄存器即可,同时也有Kest和 CLk信号控制我们的操作的进行。8位的LED进行品示我们读出的数据的一部 分!1.实验的顶层模块:module Test_Rgisterf ile(Addr, Write_Reg, Cl, C2, Clk, Reset, LED); input [4:0]Addr; input [1:O]C1;input Write Reg, C2, Clk, Reset; output reg [7:0]LED; wire [31:0]R_Data_A, R Data B; reg [31:0]W_Da.ta.; reg [4:0]A,B;Registerfileregl (A, B, Addr, Wri te Reg, W Data, Cl k, Reset, R Data A, R Data B);alvays@(Addr or Write_Reg or Cl or C2 or R_Data_A or R_Data_B) begin A:0;B二0;LRD=O:W_Data=0; if (!Write_Rcg) begin if(!C2) begin A=Addr; case (Cl)2’b00:LED=R Data A[7:0];2,b01:LED=R Data A[15:8];2'bl0:LED=R_Data_A[23:16];2' bll:LED=R Data A[31:24]; cndcascend else begin B=Addr; case (Cl)2,bOO:LED=R Data B[7:0];2’b01:LED=R_I)ata_B[15:8];2’ blO:LED=R_Data_B[23:16];2’bll:LED=R_Data_B[31:24];cndcaseendendelsebegin case (Cl)2’b00:W Data=32, hOOOO 0003;2’ bOl:W Data二32’ hOOOO 0607;2’blO:W Data=32, hEFEr EEPr;2’ bl1:W_Data=32’ hill1—1234; cndcascend endendmodule2.寄存器的操作模块:module Registerfile(input [4:0]R_Addr_A, input [4:0]R_Addr_B,input [4:0]W_Addr, input Write_Reg, input [31:0]W Data, input Clk, input Reset, output [31:0]R Data A, output [31:0]R_Data_B );reg [31:0]REG Files[0:31]; reg [5:0]i;initialbeginfor(i=0;i<=31;i=i+l)REG Files[i]:0;endassign R_Data_A=REG_Files[R_Addr_A]; assign R_Dat.a_B=REG_P'iles [R_Addr_B];always@(posedge Clk or posedge Reset) begin if (Reset)for(i=0;i〈=31;i=i+l)REG_Files[i]=0;elseif(Write Reg && W Addr!=0)REG一Files[W_Addr]=W_Data; endendmoduleLOC 二 U16;LOC=V16;LOC=U15;LOC=V15;LOC=Mil;LOC=Nil;LOC=Rll;LOC=Til;(接数据记录和汁算令 uoiz^ioooww00001?write R(9000C2X01Ohiixt Naw"Kf ,? Z 涔尸i± | I r O > H ▼」、,H3.管脚配賈NET AddrLOJ LOC = M8; NET 〃Addr[l]〃 LOC = N8; NET 〃Addr[2]〃 LOC = U8; NET 〃Addr[3]〃 LOC = V8; NET 〃Addr[4]〃 LOC = T5; NET "C1[O]" LOC = T1O; NET 〃C1[1]〃 LOC = T9; NET 〃C2〃 LOC = B8;NET 〃Clk" LOC = C9;NET "LED [OK NET "LED[1]〃 NET "LED[2]〃 NET 〃LED[3]〃 NET "LED[4]" NET 〃LED[5]〃 NET 〃LED[6]〃 NET "LED[7]〃NET "Reset" LOC = 1)9;NET,zWrite Regz,LOC = V9;实验仿真波形:结论(结果)按照实验的要求,一步步的进行操作。能够正确的进行Wirejeg写操作,进 行读操作吋LED灯的显示,利用选择A, B操作读出信号,已经Reset进行清 零信号的操作,都能顺利的进行,本实验多次失败,收获不小。 试验心得与小结本实验,让我更加淸楚的汄识到寄存器如何进行操作,实验了很多次,学到 了很多的东丙,经过多次的调试最终成功了,还是特别的开心。在不同模块 中调川寄存器,利用寄存器数组的方式进行,32位的数据的输入采用选择信 号进行操作,这些都是一步步的实验进行下来的收获!成绩评定: 指导教W签名: 关 键 词: 计算机 组成 原理 寄存器 设计 实验

天天文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

天天文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

最后

以上就是花痴菠萝最近收集整理的关于寄存器堆计算机组成实验,杭电计算机组成原理寄存器堆设计实验4的全部内容,更多相关寄存器堆计算机组成实验内容请搜索靠谱客的其他文章。

发表评论 取消回复